The Use and Construction of

Numerical Simulation Packages based on

Physical Device Models for the

Design of Silicon VLSI

# S. Selberherr

Institut für Allgemeine Elektrotechnik und Elektronik Technische Universität Wien Gußhausstraße 27-29, A-1040 Wien AUSTRIA **ABSTRACT:** A brief and qualitative review about the entitled subject is given. Particular emphasis is laid on providing references to the relevant literature.

## 1. INTRODUCTION

Silicon VLSI Technology has evolved to a standard that hundreds of thousands transistor devices are integrated in a single chip. To optimize the efficiency in device design and fabrication improved understanding of basic device operation has become crucial. The application of numerical simulation packages for the development of prototype devices is therefore a basic requirement.

# 2. HISTORY

Hermann Gummel [27] in 1964 was the first to suggest fully numerical modeling of a semiconductor device based on partial differential equations [62] which describe all different regions of a device in one unified manner. He has demonstrated this technique for the one dimensional bipolar transistor. This approach was further developed and applied to pn-junction theory by De Mari [15], [16] and to IMPATT diodes by Scharfetter and Gummel [52]. A two dimensional solution of Poisson's equation with application to a MOS structure was first published by Loeb et al. [34] and Schroeder and Muller [53] in 1968. Kennedy and O'Brien [31] investigated in 1969 the junction field effect transistor by means of a two dimensional numerical solution of Poisson's equation and one continuity equation. At the same time Slotboom [59] presented a two dimensional analysis of the bipolar transistor solving Poisson's equation and both continuity equations. Since then two dimensional numerical modeling has been applied to nearly all important devices. For some more citations regarding the history of modeling the interested reader is refered to [56].

#### 3. COMPREHENSIVE LITERATURE

A few monographs [12], [19], [33], [37], [44], [56] have been published on the subject of numerical device simulation.

Various conferences with proceedings published as books, e.g.:[6], [7], [8], [9], [41], [43] have taken place, and courses, e.g.:[2], [17], [39], [40], [42], [61] have been held.

Among many more the following outstanding review papers have been published [18], [21], [30] and [45].

## 4. THE PHYSICAL MODEL

Five basic equations as given first by Van Roosbroeck [62] are primarily used to describe current flow in silicon.\* These are the Poisson equation (1), the continuity equations for electrons (2) and holes (3) and the current relations for electrons (4) and holes (5). The principles for the derivation of these equations can be found in, e.g., [57].

$$\operatorname{div} \operatorname{grad} \psi = \frac{q}{\epsilon} \cdot (n - p - C) \tag{1}$$

$$\operatorname{div} \vec{J}_n - q \cdot \frac{\partial n}{\partial t} = q \cdot R \tag{2}$$

$$\operatorname{div} \, \vec{J}_p + q \cdot \frac{\partial p}{\partial t} = -q \cdot R \tag{3}$$

$$\vec{J}_n = -q \cdot \mu_n \cdot (n \cdot \operatorname{grad} \psi - \operatorname{grad} (Ut_n \cdot n)) \tag{4}$$

$$\vec{J}_p = -q \cdot \mu_p \cdot (p \cdot \operatorname{grad} \psi + \operatorname{grad} (Ut_p \cdot p))$$

(5)

These equations include a couple of so-called physical parameters for which appropriate physical models have to be given. The dependent unknowns are  $\psi, n, p$  which are the electrostatic potential, the concentration of electrons and the concentration of holes.

The Poisson equation (1) requires the net doping concentration C which is probably the most prominent parameter of the whole model in order to be complete. To obtain qualitatively and quantitatively the net doping concentration for a

<sup>\*</sup> Physically more sophisticated techniques like Monte Carlo methods will not be discussed

particular device configuration is an art on its own. The subject process simulation has therefore attained significant relevance in recent years. An overview and an impression how difficult the treatment of this subject is can be found in the reports [38], [48], [49], [50] of the very famous groups at the Stanford University. q and  $\epsilon$  denote the elementary charge and the permittivity constant, respectively.

The current continuity equations (2) and (3) show the net generation/recombination rate R as physical parameter. This parameter has been introduced by a quite artificial procedure, c.f.: [56] and, therefore, particular care must be devoted to model this quantity appropriately. A concise review can be found in [4], [20], [56].

The current relations (4) and (5) are the most complex equations out of the set of the basic semiconductor device equations. Their derivation from more fundamental physical principles is not at all straightforward. They appear therefore with all sorts of slight variations in the specialized literature and a vast number of papers has been published where with some of their subtleties is dealt with. The interested reader is referred to, e.g., [3], [5], [24], [14], [57].

$\mu_n$  and  $\mu_p$ , the mobilities of electrons and holes, respectively, and  $Ut_n$  and  $Ut_p$ , the electronic voltages of electrons and holes, respectively, are the physical parameters in my particular formulation of (4) and (5). These quantities have again to be appropriately modeled in order to be able to compute practically useful results with the basic semiconductor equations, e.g., [4], [56]. A selfconsistent derivation of my form of the current relations (4) and (5) has been presented in [28] where also their superiority has been tried to be explained. Some additional discussion can be found in [58].

# 5. THE MATHEMATICAL MODEL

The basic semiconductor equations (1) to (5) together with appropriate boundary conditions and models for the involved physical parameters constitute a nonlinear system of mixed elliptic — parabolic partial differential equations. Of particular concern for such a complex mathematical model are therefore questions of existence, uniqueness and qualitative structure of solutions. This is not only interesting from a theoretical point of view, but also very important in the practical context, since knowledge of the properties of the mathematical model is an essential prerequisite for the selection of suitable and efficient numerical algorithms. Furthermore, destructive and/or missing results from mathematical analysis often indicate that some error has been introduced in the physical model by, for instance, oversimplifying assumptions. The mathematical analysis thus can serve as an independent strategy to falsify improper physical reasoning (Remember that one rarely can verify physical models). However, it remains to state that the mathematical analysis of the basic semiconductor equations

did contribute prominently in recent years to the enhancement of efficiency and applicability of numerical device simulation codes, though the novice engineer in this field might have more "important" interests. Nevertheless, the best texts to serve as a substantial introduction are the monographs by Mock [44] and Markowich [37].

# 6. THE NUMERICAL MODEL

In order to numerically solve the basic semiconductor equations three fundamental steps have to be carried out. First, the mathematical domain which constitutes a semiconductor device has to be appropriately partitioned into sufficiently small subdomains. Secondly, consistent approximations to the partial differential equations must be seeked by assuming a particular functional (usually algebraic) behavior of their solutions for each subdomain. Thereby, one obtains a corresponding (usually algebraic) system of nonlinear equations which, thirdly, has to be solved. This system of nonlinear equations has usually only point values of the solution functions as discrete unknowns. These point values give together with the assumed functional behavior of the second step an approximation to the exact solution of the analytically posed problem, the accuracy of which depends on the quality of the partitioning of the entire simulation domain into subdomains.

For this very general concept exists a variety of choices for the detailed procedure. Most established are either finite-difference or finite-element methods. These classical methods are frequently considered as mutually exclusive from their underlying mathematical principles. However, with some distant but definitely rigorous view the detailed advantages of one of the procedures can be translated into the other. I have personally enjoyed the comments in [18] about these questions. Further insight can be gained from the book by Mock [44] and a very detailed introduction into this field can be found in [56].

## 7. AN EXAMPLE

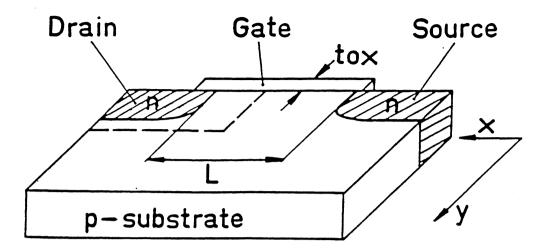

In the following some results calculated with MINIMOS 3 for a realistic n-channel MOSFET with  $0.5\mu m$  effective channel length are presented to serve for the novice as a didactical example.\* With Fig.1 the geometrical specifications of the MOSFET are given for reference. The gateoxide thickness is 12.5nm; the substrate doping is  $10^{17} \text{cm}^{-3}$  and a threshold tailoring implant is performed.

<sup>\*</sup> A similar discussion of this example can be found in [58].

Fig.1: Structure of MOSFET

One feature of major benefit of device simulation is the fact that physical phenomena can be selectively switched off. This enables the study of detailed device behavior in a manner not accessible to experiment. With the following results the physical phenomenon "energy relaxation" will be presented with the just mentioned strategy.

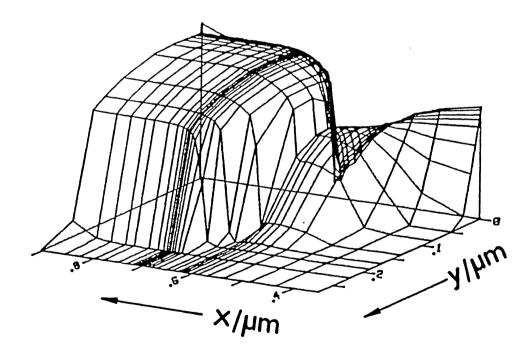

Fig.2: Electron Concentration  $\tau_{\epsilon}=0$

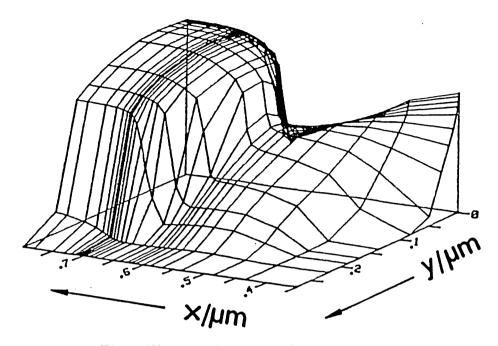

Fig.3: Electron Concentration  $\tau_{\epsilon}$ =0.1ps

In Fig.2 and Fig.3 the electron concentration close to the drain (dashed area in Fig.1) is shown for a bias point leading to saturation (5V applied at the drain contact). The result in Fig.2 was calculated by assuming a vanishing energy relaxation time  $\tau_{\epsilon}$ . For the result in Fig.3 the energy relaxation time  $\tau_{\epsilon}$ =0.1ps has been taken. One can observe from these figures that the electron concentration becomes smoother due to carrier heating. Furthermore, the electrons are pushed into the substrate which increases the average distance of the carriers from the  $Si/SiO_2$  interface.

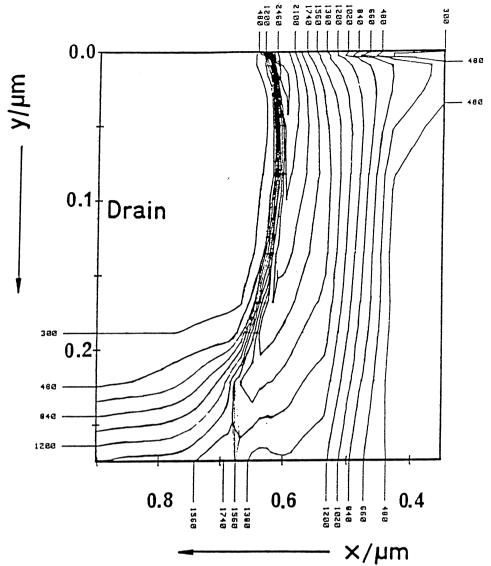

In Fig.4 the carrier temperature of the electrons is shown. The carrier temperature is proportional to the electronic voltage by q/k, i.e., elementary charge over Boltzmann's constant. The carrier temperature must not be mixed up with the lattice or ambient temperature which is kept constant at 300K for this example. Only for cold carriers the carrier temperature and the lattice temperature are equal. In our example the maximum of the carrier temperature is about eight times the equilibrium value which would have been assumed by neglecting energy relaxation.

Fig.4: Carrier Temperature of Electrons

# 8. DEVICE SIMULATION PROGRAMS

Over the last two decades a couple of dozens device simulation programs have been written all over the world. Table 1 summarizes exactly one dozen out of these without any claim that these programs are in any extent superior to the many not mentioned because of lack of space. The only intent of the presentation of the table is to provide the interested reader with references about actual software products.

The minimum effort to be spent to design and code a new device simulation program when building on the available knowledge can be estimated in the order of three person years. Any organization starting the development of a new program should keep that closely in mind. For instance, for the present state of

MINIMOS we have spent roughly ten person years and four complete redesigns from a software engineering point of view. For BAMBI we have spent roughly eight person years and we know that still some non negligible effort will have to be spent to make the product totally satisfactory.

| $\operatorname{Code}$ | Authorship | Features          | Application | Reference  |

|-----------------------|------------|-------------------|-------------|------------|

| BAMBI                 | VIENNA     | 2-D,2-Carr.,Tran. | arbitrary   | [22], [23] |

| $\mathbf{CADDET}$     | HITACHI    | 2-D,2-Carr.       | planar FET  | [60]       |

| FIELDAY               | IBM        | 2-D,2-Carr.,Tran. | arbitrary   | [10], [11] |

| GALENE                | AACHEN     | 2-D,2-Carr.,Tran. | planar      | [35], [36] |

| GEMINI                | STANFORD   | 2-D,Poiss.        | arbitrary   | [25], [26] |

| MINIMOS               | VIENNA     | 2-D,2-Carr.       | planar MOS  | [54], [55] |

| PISCES                | STANFORD   | 2-D,2-Carr.,Tran. | arbitrary   | [46], [47] |

| WATMOS                | WATERLOO   | 3-D,Poiss.        | planar MOS  | [13], [29] |

| ***                   | MICHIGAN   | 2-D,2-Carr.       | planar MOS  | [63]       |

| ***                   | MITSUBISHI | 2-D,2-Carr.       | planar MOS  | [32]       |

| ***                   | NTT        | 2-D,2-Carr.       | planar MOS  | [1]        |

| ***                   | PHILIPS    | 2-D,2-Carr.       | planar      | [51]       |

Table 1: Device Simulation Programs

## ACKNOWLEDGEMENT

My work is considerably supported by the research laboratories of SIEMENS AG at Munich, FRG, the research laboratories of DIGITAL EQUIPMENT CORPORATION at Hudson, USA, and the "Fond zur Förderung der wissenschaftlichen Forschung" under contract S43/10. I am indebted to my teacher, Prof.H.Pötzl, for many critical and stimulating discussions.

#### REFERENCES

- 1. Adachi T., Yoshii A., Sudo T., "Two-Dimensional Semiconductor Analysis Using Finite-Element Method", IEEE Trans. Electron Devices, Vol. ED-26, pp.1026-1031, 1979.

- 2. Antognetti P., Antoniadis D.A., Dutton R.W., Oldham W.G., "Process and Device Simulation for MOS-VLSI Circuits", Martinus Nijhoff, The Hague, 1983.

- 3. Baccarani G., "Physics of Submicron Devices", Proc.VLSI Process and Device Modeling, pp.1-23, Katholieke Universiteit Leuven, 1983.

- 4. Baccarani G., Rudan M., Guerrieri R., Ciampolini P., "Physical Models for Numerical Device Simulation", in: Process and Device Modeling, pp.107-158, North-Holland, Amsterdam, 1986.

- 5. Blotekjaer K., "Transport Equations for Electrons in Two-Valley Semiconductors", IEEE Trans. Electron Devices, Vol. ED-17, pp.38-47, 1970.

- 6. Board K., Owen D.R.J., "Simulation of Semiconductor Devices and Processes", ISBN 0-906674-38-7, Pineridge Press, Swansea, 1984.

- 7. Board K., Owen D.R.J., "Simulation of Semiconductor Devices and Processes: Volume 2", ISBN 0-906674-59-X, Pineridge Press, Swansea, 1986.

- 8. Browne B.T., Miller J.J., "Numerical Analysis of Semiconductor Devices", ISBN 0-906783-00-3, Boole Press, Dublin, 1979.

- 9. Browne B.T., Miller J.J., "Numerical Analysis of Semiconductor Devices and Integrated Circuits", ISBN 0-906783-03-8, Boole Press, Dublin, 1981.

- 10. Buturla E.M., Cottrell P.E., "Simulation of Semiconductor Transport Using Coupled and Decoupled Solution Techniques", Solid-State Electron., Vol.23, pp.331-334, 1980.

- 11. Buturla E.M., Cottrell P.E., Grossman B.M., Salsburg K.A., "Finite-Element Analysis of Semiconductor Devices: The FIELDAY Program", IBM J.Res.-Dev., Vol.25, pp.218-231, 1981.

- 12. Cham K.M., Oh S.Y., Chin D., Moll J.L., "Computer-Aided Design and VLSI Device Development", ISBN 0-89838-204-1, Kluwer, Boston, 1986.

- 13. Chamberlain S.G., Husain A., "Three-Dimensional Simulation of VLSI MOS-FET's", Proc.Int.Electron Devices Meeting, pp.592-595, 1981.

- 14. Cook R.K., Frey J., "Two-Dimensional Numerical Simulation of Energy Transport Effects in Si and GaAs MESFET's", IEEE Trans. Electron Devices, Vol. ED-29, pp. 970-977, 1982.

- 15. DeMari A., "An Accurate Numerical Steady-State One-Dimensional Solution of the P-N Junction", Solid-State Electron., Vol.11, pp.33-58, 1968.

- 16. DeMari A., "An Accurate Numerical One-Dimensional Solution of the P-N Junction under Arbitrary Transient Conditions", Solid-State Electron., Vol.11, pp.1021-2053, 1968.

- 17. DeMeyer K.M., "VLSI Process and Device Modeling", Katholieke Universiteit Leuven, 1983.

- 18. Engl W.L., Dirks H.K., Meinerzhagen B., "Device Modeling", Proc.IEEE, Vol.71, pp.10-33, 1983.

- 19. Engl W.L., "Process and Device Modeling", ISBN 0-444-87891-2, North Holland, Amsterdam, 1986.

- 20. Engl W.L., Dirks H., "Models of Physical Parameters", in: Introduction to the Numerical Analysis of Semiconductor Devices and Integrated Circuits, pp.42-46, Boole Press, Dublin 1981.

- 21. Engl W.L., Manck O., Wieder A.W., "Device Modeling", in: Process and Device Modeling for Integrated Circuit Design, pp.3-17, Noordhoff, Leyden 1977.

- 22. Franz A.F., Franz G.A., Selberherr S., Ringhofer C., Markowich P., "Finite Boxes A Generalization of the Finite Difference Method Suitable for Semiconductor Device Simulation", IEEE Trans. Electron Devices, Vol. ED-30, pp.1070-1082, 1983.

- 23. Franz A.F., Franz G.A., "BAMBI A Design Model for Power MOSFET's", IEEE Trans.CAD of Integrated Circuits and Systems, Vol.CAD-4, pp.177-189, 1985.

- 24. Frey J., "Transport Physics for VLSI", in: Introduction to the Numerical Analysis of Semiconductor Devices and Integrated Circuits, pp.51-57, Boole Press, Dublin 1981.

- 25. Greenfield J.A., Dutton R.W., "Nonplanar VLSI Device Analysis Using the Solution of Poisson's Equation", IEEE Trans. Electron Devices, Vol. ED-27, pp.1520-1532, 1980.

- 26. Greenfield J.A., Hansen S.E., Dutton R.W., "Two-Dimensional Analysis for Device Modeling", Report G-201-7, Stanford University, 1980.

- 27. Gummel H.K., "A Self-Consistent Iterative Scheme for One-Dimensional Steady State Transistor Calculations", IEEE Trans. Electron Devices, Vol.-ED-11, pp.455-465, 1964.

- 28. Hänsch W., "Carrier Transport in Semiconductor Devices of Very Small Dimensions", in: Two-Dimensional Systems: Physics and Devices, Vol.67, pp.296-303, Springer, Berlin, 1986.

- 29. Husain A., Chamberlain S.G., "Three-Dimensional Simulation of VLSI MOS-FET's: The Three-Dimensional Simulation Program WATMOS", IEEE J.Solid-State Circuits, Vol.SC-17, pp.261-268, 1982.

- 30. Kani K., "A Survey of Semiconductor Device Analysis in Japan", Proc.NA-SECODE I Conf., pp.104-119, 1979.

- 31. Kennedy D.P., O'Brien R.R., "Two-Dimensional Mathematical Analysis of a Planar Type Junction Field-Effect Transistor", IBM J.Res.Dev., Vol.13, pp.662-674, 1969.

- 32. Kotani N., Kawazu S., "Computer Analysis of Punch-Through in MOS-FET's", Solid-State Electron., Vol.22, pp.63-70, 1979.

- 33. Kurata M., "Numerical Analysis for Semiconductor Devices", Lexington, Massachusetts, 1982.

- 34. Loeb H.W., Andrew R., Love W., "Application of 2-Dimensional Solutions of the Shockley-Poisson Equation to Inversion-Layer M.O.S.T. Devices", Electron.Lett., Vol.4, pp.352-354, 1968.

- 35. Manck O., Heimeier H.H., Engl W.L., "High Injection in a Two-Dimensional Transistor", IEEE Trans. Electron Devices, Vol. ED-21, pp.403-409, 1974.

- 36. Manck O., Engl W.L., "Two-Dimensional Computer Simulation for Switching a Bipolar Transistor Out of Saturation", IEEE Trans. Electron Devices, Vol. ED-22, pp.339-347, 1975.

- 37. Markowich P.A., "The Stationary Semiconductor Device Equations", ISBN 3-211-81892-8, Springer, Wien New-York, 1986.

- 38. Meindl J.D., Dutton R.W., Gibbons J.F., Helms C.R., Plummer J.D., Tiller W.A., Ho C.P., Saraswat K.C., Deal B.E., Kamins T.I., "Computer-Aided Engineering of Semiconductor Integrated Circuits", Report TRDXG501, ICL17-78, Stanford University, 1980.

- 39. Miller J.J., "An Introduction to the Numerical Analysis of Semiconductor Devices and Integrated Circuits", ISBN 0-906783-04-6, Boole Press, Dublin, 1981.

- 40. Miller J.J., "Finite Element Programming with Special Emphasis on Semiconductor Device and Process Modelling", ISBN 0-906783-22-4, Boole Press, Dublin, 1983.

- 41. Miller J.J., "NASECODE III: Numerical Analysis of Semiconductor Devices and Integrated Circuits", ISBN 0-906783-20-8, Boole Press, Dublin, 1983.

- 42. Miller J.J., "New Problems and New Solutions for Device and Process Modelling", ISBN 0-906783-45-3, Boole Press, Dublin, 1985.

- 43. Miller J.J., "NASECODE IV: Numerical Analysis of Semiconductor Devices and Integrated Circuits", ISBN 0-906783-43-7, Boole Press, Dublin, 1985.

- 44. Mock M.S., "Analysis of Mathematical Models of Semiconductor Devices", ISBN 0-906783-07-0, Boole Press, Dublin, 1983.

- 45. Newton A.R., "Computer-Aided Design of VLSI Circuits", Proc.IEEE, Vol.-69, pp.1189-1199, 1981.

- 46. Pinto M.R., Dutton R.W., "An Efficient Numerical Model of CMOS Latch-Up", IEEE Electron Device Lett., Vol.EDL-4, pp.414-417, 1983.

- 47. Pinto M.R., "PISCES IIB", Stanford University, 1985.

- 48. Plummer J.D., Dutton R.W., Gibbons J.F., Helms C.R., Meindl J.D., Tiller W.A., Christel L.A., Ho C.P., Mei L., Saraswat K.C., Deal B.E., Kamins T.I., "Computer-Aided Design of Integrated Circuit Fabrication Processes for VLSI Devices", Report TRDXG501-82, ICL17-79, Stanford University, 1982.

- 49. Plummer J.D., Dutton R.W., Gibbons J.F., Helms C.R., Meindl J.D., Tiller W.A., Ho C.P., Saraswat K.C., Deal B.E., "Computer-Aided Design of Integrated Circuit Fabrication Processes for VLSI Devices", Report TRDXG501-84 ICL17-79, Stanford University, 1984.

- 50. Plummer J.D., Dutton R.W., Bravman J.C., Deal B.E., Helms C.R., Saraswat K.C., Sigmon T., Stevenson D.A., Tiller W.A., Deal B.E., Fahey P., McVittie j.P., Hansen S.E., "Process Simulators for Silicon VLSI and High Speed GaAs Devices", Stanford University, 1986.

- 51. Polak S.J., Schilders W.H.A., DenHeijer C., Wachters A.J.H., Vaes H.M., "Automatic Problemsize Reduction for On-State Semiconductor Problems", IEEE Trans. Electron Devices, Vol. ED-30, pp.1050-1056, 1983.

- 52. Scharfetter D.L., Gummel H.K., "Large-Signal Analysis of a Silicon Read Diode Oscillator", IEEE Trans. Electron Devices, Vol. ED-16, pp.64-77, 1969.

- 53. Schroeder J.E., Muller R.S., "IGFET Analysis Through Numerical Solution of Poisson's Equation", IEEE Trans. Electron Devices, Vol. ED-15, pp.954-961, 1968.

- 54. Schütz A., Selberherr S., Pötzl H., "A Two-Dimensional Model of the Avalanche Effect in MOS Transistors", Solid-State Electron., Vol.25, pp.177-183, 1982.

- Selberherr S., Schütz A., Pötzl H., "MINIMOS A Two-Dimensional MOS Transistor Analyzer", IEEE Trans. Electron Devices, Vol. ED-27, pp.1540-1550, 1980.

- 56. Selberherr S., "Analysis and Simulation of Semiconductor Devices", ISBN 3-211-81800-6, Springer, Wien New-York, 1984.

- 57. Selberherr S., Griebel W., Pötzl H., "Transport Physics for Modeling Semiconductor Devices", in: Simulation of Semiconductor Devices and Processes, pp.133-152, Pineridge Press, Swansea, 1984.

- 58. Selberherr S., "The Status of MINIMOS", in: Simulation of Semiconductor Devices and Processes, pp.2-15, Pineridge Press, Swansea, 1986.

- 59. Slotboom J.W., "Iterative Scheme for 1- and 2-Dimensional D.C.-Transistor Simulation", Electron.Lett., Vol.5, pp.677-678, 1969.

- 60. Toyabe T., Yamaguchi K., Asai S., Mock M.S., "A Numerical Model of Avalanche Breakdown in MOSFET's", IEEE Trans. Electron Devices, Vol.-ED-25, pp.825-832, 1978.

- 61. VanDeWiele F., Engl W.L., Jespers P.G., "Process and Device Modeling for Integrated Circuit Design", Noordhoff, Leyden, 1977.

- 62. VanRoosbroeck W.V., "Theory of Flow of Electrons and Holes in Germanium and Other Semiconductors", Bell Syst.Techn.J., Vol.29, pp.560-607, 1950.

- 63. Watanabe D.S., Slamet S., "Numerical Simulation of Hot-Electron Phenomena", IEEE Trans. Electron Devices, Vol. ED-30, pp.1042-1049, 19833.