# GaAs-MESFET Simulation with MINIMOS

Ph. Lindorfer, S. Selberherr

Institut für Mikroelektronik, Technische Universität Wien A-1040 WIEN, Gußhausstraße 27-29, AUSTRIA

### ABSTRACT

This paper presents the implementation of models allowing the simulation of GaAs MESFETs with MINIMOS 5 - an integrated 2D and 3D device simulator for silicon MOSFETs. Models for the Schottky contact and possible device geometries are shown. As a result a simulation of a T-gate MESFET is presented.

#### INTRODUCTION

GaAs devices have become of increasing importance for high speed analog and digital circuits since their introduction in 1970. GaAs FET amplifiers, oscillators, mixers, etc. are widely used in microwave applications whereas very fast digital circuits have been developed based on GaAs MESFET logic. Because of the physical properties of GaAs, the MESFET is the mostly used device for those applications. Moreover, MESFET offer some advantages over MOSFETs. Mobilities are higher, since carriers are transported deep in the bulk and no minority carrier storage effects take place, which results in faster switching speeds. Furthermore, MESFETs are less radiation sensitive, because of the missing gate oxide.

With the increasing relevance of MESFETs the need for efficient simulation of these devices has become apparent. Using the framework and capabilities of MINIMOS 5 which is our integrated two- and three-dimensional device simulator for silicon MOSFETs with transient and small signal analysis capabilities we implemented models

allowing the simulation of MESFETs and models for GaAs as substrate material.

## BASIC EQUATIONS

MINIMOS 5 solves the basic semiconductor equations in two or three space dimensions. The set of equations consists of the Poisson equation (1) and the continuity equations for electrons (2) and holes (3):

$$div \ grad \ \psi = \frac{q}{\varepsilon} \cdot (n - p - C) \tag{1}$$

$$div J_n = q \cdot R \tag{2}$$

$$div J_p = -q \cdot R \tag{3}$$

The current relations for electrons and holes differ slightly from the classical formulations, which can be found in [1]:

$$J_{n} = q \cdot \mu_{n} \cdot n \cdot (-grad \ \psi + \frac{1}{n} \cdot grad \ (U_{t_{n}} \cdot n))$$

(4)

$$J_{p} = q \cdot \mu_{p} \cdot p \cdot (-grad \ \psi - \frac{1}{p} \cdot grad \ (U_{t_{p}} \cdot p))$$

(5)

In equation (4) and (5) the second term accounts for carrier heating effects by field dependent modelling of the carrier temperatures. Detailed information about the derivation of these formulations can be found in [2]. These equations have proven to work well for silicon MOSFETs and MESFETs

with gate length down to 0.1 microns. For GaAs devices the classical drift-diffusion approach has proven to be suitable only for relatively long devices whereas for very small feature sizes nonstationary transport effects can become apparent which are usually claimed to be properly modelled by either Monte Carlo methods or hydrodynamic equations based on higher moments of the Boltzmann equation [3]. We have evidence that our current relations (4) and (5) in connection with appropriate models for the carrier voltages Utn and  $U_{tp}$  push the limit of applicability of these enhanced drift-diffusion equations significantly towards smaller feature sizes. Final investigations which give a sound proof will have to be carried out.

### BOUNDARY CONDITIONS

To allow the simulation of MESFETs with MINI-MOS a boundary condition for the Schottky gate contact had to be implemented.

A Dirichlet boundary condition is used for the potential  $\psi$

$$\psi = \psi_{app} - \psi_s \tag{6}$$

where  $\psi_{app}$  is the applied voltage and  $\psi_s$  is the surface potential at the interface.  $\psi_s$  depends on the barrier height  $\phi_B$  in the following way

$$\psi_{s} = \phi_{B} - \frac{E_{g}}{2} - \frac{kT}{2g} \cdot ln\left(\frac{N_{v}}{N_{c}}\right) \tag{7}$$

where the barrier height is allowed to change in case of large reverse bias

$$\Delta\phi_B = \sqrt{\frac{qE}{4\pi\varepsilon_*}}\tag{8}$$

to account for the image force lowering.  $\varepsilon$ , is the permittivity of the semiconductor, E the electric field at the interface,  $E_g$  the bang gap of the semiconductor and  $N_c$  and  $N_v$  the density of states of the conduction and the valence band.

Implicit boundary conditions are implemented for the carrier densities n and p by using boundary conditions for the current densities  $J_n$  and  $J_p$  perpendicular to the interface.

$$J_n = -q \cdot v_n \cdot (n - n_0) \tag{8}$$

$$J_{p} = q \cdot v_{p} \cdot (p - p_{0}) \tag{9}$$

$n_0$  and  $p_0$  are the equilibrium carrier concentrations at the surface defined by

$$n_0 = n_i \cdot exp\left(-\frac{\psi_s}{U_T}\right) \tag{10}$$

$$p_0 = n_i \cdot exp\left(\frac{\psi_s}{U_T}\right) \tag{11}$$

The surface recombination velocities  $v_n$  and  $v_p$  are modeled current dependent.

$$v_{n,p} = v_d + \sqrt{\frac{2 k T}{m_{n,p}^* \pi \eta_{n,p}}} \frac{exp\left(-v_d^2\left(\frac{m_{n,p}^* \eta_{n,p}}{2 k T}\right)\right)}{1 + erf\left(v_d\sqrt{\frac{m_{n,p}^* \eta_{n,p}}{2 k T}}\right)}$$

(12)

Here  $m^*$  is the effective mass for either electrons or holes,  $\eta_{n,p}$  is an 'non-ideality' factor, which accounts for changes in the band structure at the interface and  $v_d$  is the drift velocity defined by

$$v_d = \frac{J_{n,p}}{q \cdot (n,p)} \tag{13}$$

Equation (12) is bounded from above by the saturation velocity of the semiconductor  $v_{sat}$  which limits  $v_d$  and from below by the condition  $v_d = 0$  which gives

$$v_{n,p} = \sqrt{\frac{2 k T}{m_{n,p}^* \pi \eta_{n,p}}}$$

(14)

This formulation gives a higher recombination velocity at large forward biased Schottky contacts which avoids an unrealistic accumulation of carriers and so leads to better results in those cases. A detailed derivation of this model can be found in [4].

### PROCESS MODELS

To provide user-friendly use of MINIMOS for GaAs simulation various process parameters like implantation statistics and diffusion coefficients for various dopants have been implemented based on Monte Carlo calculations with PROMIS [5].

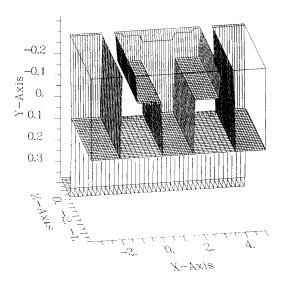

Fig. 1

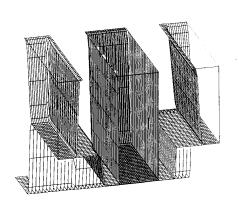

Fig. 2

These parameters can easily set by the user via the input deck, to define source/drain and/or channel implantation. Moreover, the user has the possibility to use one— or two-dimensional data from a process simulator.

## DEVICE GEOMETRIES

For an efficient simulation of GaAs devices it is necessary to simulate different nonplanar geometries like recessed gate or T-gate MESFETs. Various enhancements had to be made to allow the simulation of these nonplanarities with MINIMOS 5 which was able to simulate nonplanar MOS structures [6]. Fig. 1 shows shape of the source, the gate and the drain contact of a T-gate MESFET whereas one can see a recessed gate device with the recessed semiconductor surface in Fig. 2. The figures are not on the same scale in all three space dimensions.

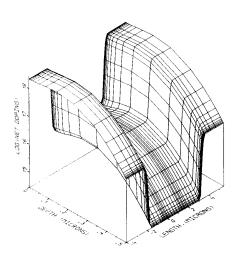

Fig. 3

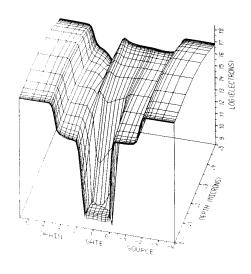

#### RESULTS

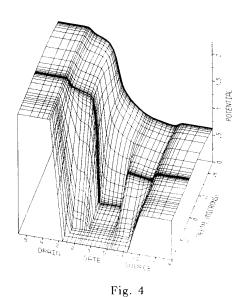

As an example an n-channel T-gate MESFET with 1.5 micron gate length was simulated. The shape of contacts with the dimensions of the Tgate is shown in Fig. 1. The thickness of the semiconductor layer is 0.5 micron. The Schottky barrier height is 0.6 V. The device is biased with -0.2 V on gate and 1.5 V on drain. The device has a source/drain implantation with a peak concentration of 2 · 1018 and a channel implantation with a peak of 1016, which is shown in Fig. 3. In Fig. 4 one can see the potential distribution in the device. In front the shape of the T-gate can be seen. The electron concentration of the transistor is shown in Fig. 5. The depletion region reaches 0.2 microns into the layer. Deeper in the bulk one can see a considerable channel with a carrier concentration in the order of 1016. The drain current in this case is 0.36 mA for 10.0 microns gate width.

### ACKNOWLEDGEMENT

This work was considerably supported by the research laboratories of SIEMENS AG in Munich, FRG and by DIGITAL in Hudson, USA.

280 - GaAs IC Symposium

### REFERENCES

- SELBERHERR S., Analysis and Simulation of Semiconductor Devices, ISBN 3-211-81800-6,

Springer, Wien-New York, 1984.

- [2] HÄNSCH W., SELBERHERR S., "MINI-MOS 3: A MOSFET Simulator that Includes Energy Balance", IEEE ED-34, No. 5,1987.

- [3] FENG Y., HINTZ A., "Simulation of Submicrometer GaAs MESFETs Using a Full Dynamic Transport Model", IEEE ED-35, No. 9,1988.

- [4] NYLANDER J.O., MASSZI F., SELBER-HERR S., BERG S. "Computer Simulations of Schottky Contacts with a Non-Constant Recombination Velocity", Solid-State Electronics, Vol. 32, No. 5, 1989.

- [5] HOBLER G.,"Multiple Use of Trajectories in Monte Carlo Ion Implantation Simulation", Proc. NASECODE VI Conf., 1989.

- [6] THURNER M., "Dreidimensionale Modellierung von MOS Transistoren", Dissertation, Technical University Vienna, 1988.

Fig. 5