# A Physically Based DC- and AC-Model for Vertical Smart Power DMOS Transistors

Martin Stiftinger†, Winfried Soppa‡, and Siegfried Selberherr†

†Institute for Microelectronics, Technical University Vienna Gusshausstraße 27–29, A-1040 Wien, Austria

‡Bereich Halbleiter, SIEMENS AG Balanstraße 73, D-8000 München 80, Germany

#### Abstract

Based on device simulations an analytical DC- and AC-model for vertical DMOS transistors has been developed. It is based on a subcircuit approach. An enhanced MOS model for the channel and an adapted JFET model which accounts for drift velocity saturation in the drift region are used. As in existing approaches both the nonconstant doping in the channel region and the AC-behavior of the DMOS have not been thoroughly investigated special attention is paid to these aspects. Comparisons with numerical device simulations are presented to confirm the physical correctness of the new approaches.

### 1 Introduction

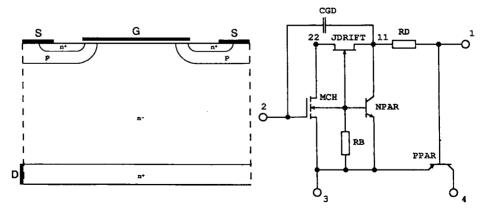

Smart Power DMOS transistors (see Fig. 1) serve primarily as interface between digital control logic and the power load (DMOS-switches can consist of up to 10.000 cells). Since they are also used in analog applications (e.g. as a single cell transistor) there are high demands on the accuracy of analytical models for circuit simulation.

Extensive device simulations with MINIMOS [5] and BAMBI [1] have led us to develop a subcircuit approach for an analytical model which is shown in Fig. 2. As circuit simulations of DMOS transistors have often to be performed in complex circuits (integrated technology) one of the major goals was to use as little elements in the subcircuit as possible to keep simulation times short.

The channel is represented by an enhanced analog MOSFET model which also accounts for the strongly nonuniform channel doping profile in lateral direction, the drift region is approximated by a modified JFET model which includes the drift velocity saturation in the epi-layer. The gate-drain capacitance is modeled by a nonlinear capacitance, while parasitic behavior under reverse bias is described by standard bipolar transistor models.

## 2 Drift region

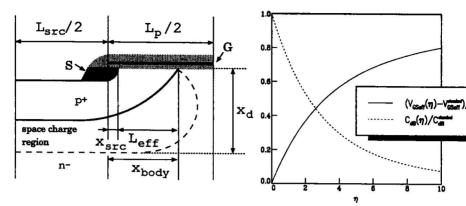

The modified JFET model accounts for the special geometry of a DMOS cell (see Fig. 3) [6] and drift velocity saturation which has important influence on the quasi-saturation behavior

(only slight dependence of the drain current on  $V_{GS}$  for high gate voltages) of the device [2]:

$$I_{D} = \frac{A_{d}qN_{epi}\mu_{epi}}{x_{d}\left(U_{bi} - U_{p}\right)} \cdot \frac{\left(U_{BD} - U_{p} - \frac{1}{2}U_{dD}\right)U_{dD}}{\left(1 + \left(\frac{U_{dD}\mu_{s}}{x_{d}v_{max}}\right)^{a}\right)^{1/a}} \quad \text{with} \quad U_{p} = U_{bi} - \frac{qN_{epi}\left(L_{p} - 2x_{body}\right)^{2}}{8\epsilon_{s}}$$

(1)

For  $\mu_s$  the perpendicular field reduction of the mobility in the epi-layer is taken into account,  $x_d$  is the vertical extent of the space charge region, which can also easily be calculated.  $A_d$  is the maximal area for the vertical current flow.  $U_{dD}$  denotes the voltage between drain and the drain end of the channel (nodes 22 and 11 in Fig. 2).

### 3 Channel

The channel doping profile is defined by the different lateral subdiffusions of n<sup>+</sup>-source and p-body and is analytically approximated by [3]

$$N_A(x) = N_A(0) \exp\left(-\eta \frac{x}{L}\right) = N_{A0} \exp\left(-\eta \frac{x}{L}\right)$$

(2)

where  $N_{A0}$  is the channel doping concentration on the source end of the channel. The only approximation made when including equation (2) in our model is the assumption of a linearly distributed channel potential. This can be justified by observing that the carriers reach their saturation velocity  $v_{sat}$  first on the source end of the channel (higher doping concentration) and then move with  $v_{sat}$  through the channel and by the quasi-saturation behavior of the drift region which keeps the voltage across the channel sufficiently low (no classical pinch-off).

In the DC-case the result are two additional terms in the drain current. The first term increases the effective gate-source voltage (i.e. decreases threshold voltage), the second decreases the bulk depletion charge  $C_{dB}$ . Both lead to a higher drain current and are plotted (N is a normalization factor) against the "steepness factor"  $\eta$  in Fig. 4.  $\eta$  simply is the logarithm of the ratio of the doping concentration at the source and the drain end of the channel, where an exponential shape is assumed.

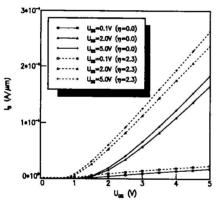

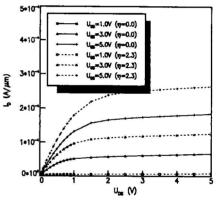

The higher drain current can physically be explained by a higher channel conductivity due to a smaller depletion charge at the drain end of the channel. Numerical device simulations with PISCES [7] and MINIMOS confirm this result. Fig. 5 shows the influence on the input characteristic with a clear decrease of the threshold voltage, Fig. 6 that on the output characteristic. For  $\eta=0$  the "classical" result is obtained.

This approach can also be used to generalize a charge based capacitance model [4] for nonconstant channel doping. The drain charge e.g. in this model reads ( $U_C$  is the channel potential):

$$Q_{D} = -WL \frac{\int_{0}^{U_{D}S} q^{2}n^{2} (U_{C}) \int_{0}^{U_{C}} qn (U_{C}') dU_{C}' dU_{C}}{\left(\int_{0}^{U_{D}S} qn (U_{C}) dU_{C}\right)^{2}}$$

(3)

Instead of the channel charge in the classical case

$$qn\left(U_{C}\right) = C_{ox}\left(U_{GSeff} - \left(1 + \kappa f_{B}\right)U_{C}\right) \tag{4}$$

the expression

$$qn(U_C) = C_{ox} \left( U_{GS} - U_{FB} - 2\Phi_F - U_C(x) - f_{B0} \exp\left(-\frac{\eta}{2} \frac{x}{L}\right) \left(2\left(2\Phi_F - U_{BS}\right) + \kappa U_C(x)\right) \right)$$

(5)

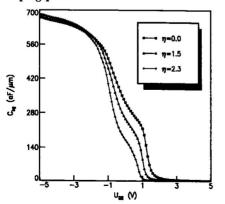

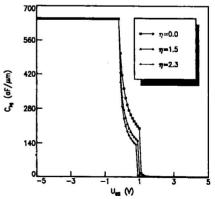

is used. For  $\eta=0$  also in this case the "classical" results are obtained. Also the AC-description of the depletion regime includes the dependency on the "stepness" of the channel doping. Comparisons with AC device simulations of a MOSFET with nonconstant doping profile performed with PISCES and the analytical model (Fig. 7 and 8) show clearly that the new approach is both a considerable improvement over the "classical" model and physically sound. The curves in Fig. 8 have neither been fitted to those in Fig. 7 nor have overlap- and junction-capacitances been taken into account in the curves in Fig. 8.

### Acknowledgement

This work is supported by the Entwicklungszentum für Mikroelektronik, SIEMENS at Villach, Austria.

### References

- A.F. Franz, G.A. Franz, W. Kausel, G. Nanz, P. Dickinger, C. Fischer, "BAMBI 2.1 User's Guide", Technical University Vienna, 1989.

- [2] M.N. Darwish, "Study of the Quasi-Saturation Effect in VDMOS Transistors", IEEE Trans. Electron Devices, Vol. ED-33, No. 11, pp. 1710-1716, November 1986.

- [3] Y.-K. Kim, J.G. Fossum, "Physical DMOST Modeling for High-Voltage IC CAD", IEEE Trans. Electron Devices, Vol. 37, No. 3, pp. 797-803, March 1990.

- [4] S. Oh, D.E. Ward, R.W. Dutton "Transient Analysis of MOS Transistors", IEEE J. Solid State Circuits, Vol. SC-15, No. 4, pp. 636-643, August 1980.

- [5] S. Selberherr, P. Habaš, O. Heinreichsberger, Ph. Lindorfer, P. Pichler, H. Pötzl, A. Schütz, M. Stiftinger, M. Thurner "MINIMOS 5 User's Guide", Technical University Vienna, 1990.

- [6] W. Soppa, J. Hänseler "A Process Oriented VDMOSFET Model for Circuit Simulation", Proceedings of ISPSD'92, Tokyo, Japan, May 1992.

- [7] "TMA PISCES-2B user's manual", Technology Modeling Associates, Inc.

Fig.1. Structure of the vertical DMOS transistor

Fig.2. Subcircuit model for the vertical DMOS transistor

Fig.3. Geometry of the DMOS cell for the modified JFET model

<u>Fig.5.</u> Numerical simulations of input characteristic for uniform and non-uniform channel doping profile

<u>Fig. 7.</u> Numerical simulations of  $C_{bg}$  over  $U_{GS}$  for uniform and non-uniform channel doping profile

<u>Fig.6.</u> Numerical simulations of output characteristic for uniform and non-uniform channel doping profile

<u>Fig. 8.</u>  $C_{bg}$  over  $U_{GS}$  for uniform and non-uniform channel doping profile in the analytical channel model.