# VLSI PERFORMANCE ANALYSIS METHOD FOR LOW-VOLTAGE CIRCUIT OPERATION

G. SCHROM\*, D. LIU\*\*, C. FISCHER\*, CH. PICHLER\*, CH. SVENSSON\*\*, and S. SELBERHERR\*

\* Institute for Microelectronics, TU Vienna

Gusshausstrasse 27-29, A-1040 Vienna, Austria

Phone +43/1/58801-5239, FAX +43/1/5059224

\*\* Dept. of Physics and Measurement Technology, Linköping University, S-58183 Linköping, Sweden

Phone +46/13/281727, FAX +46/13/137568

#### ABSTRACT

An efficient and accurate method for VLSI performance analysis is presented. It takes measured or simulated IV and capacitance data as input and yields the noise margins and delay parameters directly without any intermediate parameter extraction, avoiding the common errors of compact modeling. The method is applied to the IV/C data of an ultra-low-power CMOS process and the results are then verified by a rigorous device-level simulation of ring oscillators.

### INTRODUCTION

Because of the enormous possible power savings and due to reduced thermal and reliability problems future VLSI technologies will increasingly employ low-voltage circuit operation [1]. This, however, implies that the transition region between weak and strong inversion in MOSFETs will dominantly determine VLSI circuit performance [2]. Unfortunately, this is a weak point of virtually all compact MOSFET models, so a new method was developed avoiding these problems.

## ANALYSIS METHOD

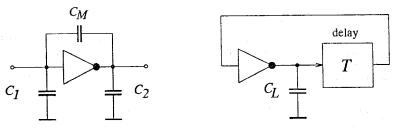

For the DC analysis a matrix of drain currents  $I_D(V_G,V_D)$  for the PMOS and NMOS transistor is computed. Using cubic interpolation in  $V_D$  direction and a modified exponential interpolation in  $V_G$  direction results in a very accurate DC model. The inverter transfer curve and noise margins are then obtained by solving  $I_{Dn}+I_{Dp}=0$  [3]. For the dynamic analysis a ring oscillator is modeled as shown in Fig. 1. All capacitive effects are modeled by a constant load capacitance of  $C_L=C_1+4C_M+C_2=C_{Gn}+C_{GDn}+C_{Dgn}+C_{Dn}+C_{Gp}+C_{GDp}+C_{Dp}$  where  $C_X(V_{GS},V_{DS})=(C_X(0,0)+C_X(V_{DD},V_{DD}))/2$ , assuming a partial compensation of the nonlinearities in the inverter circuit. The inverter delay is then calculated from the delay T and the period  $t_p$  as  $t_d=(t_p-2T)/2$ . The influence of interconnects can be easily included by adding the appropriate capacitance to  $C_L$ . Similarly, the maximum clock frequency and leakage time of dynamic circuits can be determined [2].

## VERIFICATION AGAINST DEVICE-LEVEL SIMULATIONS

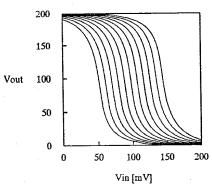

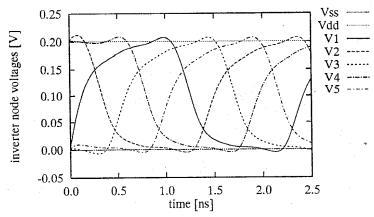

The method was tested with an ultra-low-power CMOS process designed for  $V_{DD}=200 \mathrm{mV}$  [2]. The device data were obtained by process and device simulation using VISTA with its SFC (Simulation Flow Controller) to allow quick process design and evaluation [4]. The analysis yielded inverter noise margins of  $NM_H=28 \%$  and  $NM_L=23 \%$  and a delay time of  $t_d=290 \mathrm{ps}$ . Fig. 2 shows the inverter transfer curves and Fig. 3 shows the inverter noise margins and delay time over a range of  $V_{DD}$ . To verify these results complete ring oscillators with 5 and 9 stages were rigorously simulated on the two-dimensional device level. The inverter delay is determined from the ring oscillator period  $t_p$  as  $t_d=t_p/2n_{stage}$  as  $t_d=230 \mathrm{ps}$ . Despite of the simple, i.e., quasi-static and linear dynamic model the delay time error is only 26%. This can be partially attributed to the fact that only small voltages (reducing the non-linearity of the capacitances) and small currents (reducing the non-quasi-stationary error) are involved.

### CONCLUSION

The analysis method presented here takes measured or simulated IV/C data and extracts the most important performance parameters, i.e., noise-margins and inverter delay directly without any model parameter fitting. It is noteworthy that there is no necessity to know any compact model of the devices or to define model parameters such as  $\beta_{n,p}$  or  $V_{Tn,p}$  which become very questionable at low supply voltages. Avoiding these sources of error makes our method a simple, yet powerful tool for performance analysis, especially for low-voltage/low-power circuit operation.

## ACKNOWLEDGEMENTS

This work is supported by Siemens Corporation, Munich, Germany; and Digital Equipment Corporation, Hudson, USA.

# REFERENCES

- [1] D. Liu and Ch. Svensson. Trading Speed for Low Power by Choice of Supply and Threshold Voltages. IEEE J. Solid-State Circuits, 28(1):10-17, 1993.

- [2] G. Schrom, D. Liu, Ch. Pichler, Ch. Svensson, and S. Selberherr. Analysis of Ultra-Low-Power CMOS with Process and Device Simulation. In 24th European Solid State Device Research Conference - ESSDERC'94, 1994.

- [3] N.H.E. Weste and K. Eshraghian. Principles of CMOS VLSI Design. Addison Wesley, 1993.

- [4] Ch. Pichler and S. Selberherr. Process Flow Representation within the VISTA Framework. In S. Selberherr, H. Stippel, and E. Strasser, editors, Simulation of Semiconductor Devices and Processes, volume 5, pages 25-28. Springer, 1993.

Figure 1: Dynamic inverter model and simplified ring oscillator model

5.0 4.5 td NML NM [10%Vdd], td [ns] 4.0 NMH -----3.5 3.0 2.5 2.0 1.5 1.0 0.5 0.0 0.05 0.10 0.15 0.20 Vdd [V]

Figure 2: Inverter transfer characteristics for  $W_n/W_p = 0.1...10$  (ULP process at  $V_{DD} = 200 \, \mathrm{mV}$ )

Figure 3: Noise margins and delay time vs.  $V_{DD}$

Figure 4: Inverter output voltages of a 5-stage ring oscillator at  $V_{DD}=200\mathrm{mV}$  (device-level simulation)