# The Simulation System for Three-Dimensional Capacitance and Current Density Calculation with a User Friendly GUI

M. Mukai<sup>a</sup>, T. Tatsumi<sup>a</sup>, N. Nakauchi<sup>a</sup>, T. Kobayashi<sup>a</sup>, K. Koyama<sup>a</sup>, Y. Komatsu<sup>a</sup>, R. Bauer<sup>b</sup>, G. Rieger<sup>b</sup>, S. Selberherr<sup>b</sup>

<sup>a</sup>ULSI R&D Laboratories, Semicon.Comp., SonyCorporation

<sup>4</sup>-14-1, Asahi-cho, Atsugi-shi, Kanagawa-ken, 243 JAPAN

<sup>b</sup>Institute for Microelectronics, TU Vienna

Gusshausstrasse 27-29, A-1040 Vienna, AUSTRIA

#### Abstract

For the realization of today's wiring miniaturization, it is required to accurately estimate the interconnect wiring capacitance and the current density, which has not been so far adequately accomplished. We have developed SENECA, the three-dimensional wiring capacitance and current density simulation system with graphical user interface for easy and flexible operation. The realization of this graphical input interface made it possible to reduce the man power from more than three days work to less than 30 minutes for a practical structure. The comparison between simulation and experiment proves quite good agreement. Three important applications are given to show how SENECA is utilized for practical cases.

#### 1. Introduction

According to today's wiring miniaturization, it is required to accurately estimate the interconnect wiring capacitance and the current density, which has not been so far adequately accomplished. Firstly, correct prediction of wiring capacitance is necessary to evaluate switching speed, delay of signal and cross-talks. Wiring capacitance can be classified into wire-to-ground capacitance and wire-to-wire capacitance. For conventional processes, wire-to-wire capacitance could be ignored because the distance between wires was large and its magnitude was relatively small compared with wire-to-ground capacitance. However, as the process advances, the distance between wires becomes very small, and wire-to-wire capacitance cannot be neglected. Secondly, from the aspect of wiring reliability the concentration of the current density distribution generates heat and might cause electromigration resulting in failure there. Therefore the precise prediction of current density is also necessary to maintain reliability.

We developed SENECA, a three-dimensional simulation system capable of very easily simulating wiring capacitance and current density for practical complex structures.

## 2. The Simulation System SENECA

SENECA consists of three modules: the input interface SCIN, the numerical calculation part SCAP [1][2] which utilizes a three-dimensional finite element approach

for the computation of wiring capacitances and current densities, and the output processor and viewer SCOUT.

The input data for SCAP consists of coordinate points and permittivity information of every hexahedron which is obtained by sectioning the object into small pieces, and the location information of electrodes. In case of practical applications, sectioning objects into hexahedrons by hand is almost impossible because the number of hexahedrons for practical objects soon reaches the order of a thousand or more. In order to resolve this problem, we developed a graphical input interface called SCIN, which enables to construct complex input structures accurately and very efficiently with very easy interactive operation. As one important feature of SCIN, rectangular parallelepiped, cylinder and spoon-cut, which are the structures used in wirings, are prepared as built-in models of input data, and the desired structure can be created by combining those built-in models and specifying parameters. Thus a defined input structure can be subsectioned into hexahedron meshes automatically and it generates thereby the input data for three-dimensional finite element numerical analysis. The realization of this graphical input interface made it possible to reduce the man power from more than three days work to less than 30 minutes for a practical structure.

SCAP can calculate three-dimensional wiring capacitances and current densities using finite element analysis. The three-dimensional Laplace equation is solved for the input configuration specified with SCIN. Tetrahedrons are used for discretization with quadratic shape functions leading to 10 parameters per element. Hexahedrons are decomposed automatically to tetrahedrons.

SCOUT, the output processor, calculates electric field, current density, generated heat from the current flow, and plots colored mapping and also vector representations. It can show any cross sections on the three-dimensional object, partial enlargement on any specified part, and print out with very simple button operation.

### 3. Evaluation and Practical Applications of SENECA

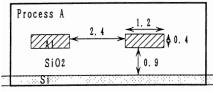

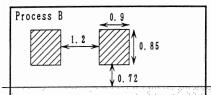

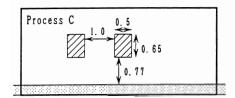

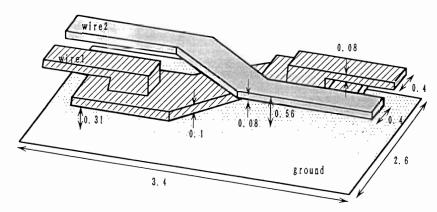

In order to investigate the interconnect capacitances between lines and between line and ground, SENECA was applied to the three kinds of processes  $A(0.7\mu m)$  rule generation),  $B(0.5\mu m)$  rule generation).  $C(0.35\mu m)$  rule generation). Shown in Fig.1 are the structures and dimensions of process A, B, C, respectively. Firstly, the detailed comparison is made on process B between experiments and simulations. Table 1 gives some of the results showing quite good agreement of 10% difference or less. In Table 2, the ratio is shown of the capacitance between wires and between wire and ground. As the process shrinks from A to C, the role of wire to wire capacitance increases from 13.8% for process A to 65.7% for process C, resulting in the very important contribution. Fig.2 shows the twisted wiring structure and we also calculated capacitance for this structure as shown in Table 3. Usually for this kind of complex structures, actual measurement is quite difficult. Only simulation makes it possible to obtain accurate capacitances.

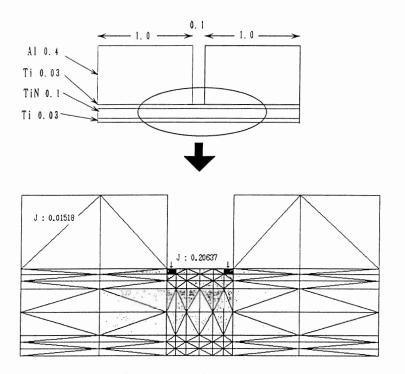

SENECA was applied to estimate the current density distribution in order to investigate the reliability[2] due to current localization for the layered wire with the aluminum layer crack caused by stress-induced migration. The wire is connected through barrier metal such as Ti/TiN/Ti. Fig. 3 shows the enlargement of the

cracked part. High current densities are shown darker than low densities. The magnitude of the highest current density parts specified with arrows and the lowest current density part are shown in the figure. The current density ratio is around 13.6 compared with the lowest part. From this current localization we can see the importance of barrier metal structures.

### 4. Conclusion

We have developed SENECA, the three-dimensional wiring capacitance and current density simulation system with graphical user interface for easy and flexible operation. SENECA is now in practical use for simulating wiring capacitances of LSIs and current density estimation for achieving better reliability. The comparison between simulation and experiment proves quite good agreement. Three important applications are given to show how SENECA is utilized for practical cases.

### References

[1] R. Bauer et al., "Capacitance Calculation of VLSI Multilevel Wiring Structures," Proc. VPAD Workshop, pp.142-143, 1993.

[2] R. Bauer et al., "Calculating Coupling Capacitances of Three-Dimensional Interconnections," Proc. Solid State and Integrated Circuit Technology 92, pp.697-699, 1992.

[3] K. Hoshino et al., "Electromigration after Stress-induced Migration Test in Quarter-Micron Al Interconnects," Proc. IRPS, pp.252-255, 1994.

Fig. 1 Wiring size (um) of process A, B and C

Table 1 Comparison between measured and simulated data (fF/um)

1A1 (First Aluminum) 2A1 (Second Aluminum)

| TAT (TITSE ATAMITMAN) PAT (BECOME ATAMITMAN |          |           |          |           |  |  |

|---------------------------------------------|----------|-----------|----------|-----------|--|--|

|                                             | wire-gnd | wire-wire | wire-gnd | wire-wire |  |  |

| SENECA                                      | 0.0742   | 0.0510    | 0.0485   | 0.0564    |  |  |

| measured                                    | 0.0762   | 0.0561    | 0.0517   | 0.0607    |  |  |

| diff                                        | 3%       | 10%       | 7%       | 8%        |  |  |

Table 2 Capacitance of A, B and C (fF/um)

|   |   | wire-gnd | wire-wire | ratio |

|---|---|----------|-----------|-------|

|   | A | 0.1044   | 0.0145    | 13.8% |

| 1 | В | 0.0871   | 0.0399    | 45.8% |

| 1 | 3 | 0.0586   | 0.0385    | 65.7% |

Table 3 Capacitance of crossed wires (fF/um)

| wirel-ground | 0.5234 |

|--------------|--------|

| wire2-ground | 0.1508 |

| wire1-wire2  | 0.3419 |

Fig. 2 Crossed wires of 256K DRAM (um)

Fig.3 Current density distribution