# Ultra-Low-Power CMOS Technologies

G. Schrom and S. Selberherr

Institute for Microelectronics, TU Vienna Gußhausstraße 27–29, A-1040 Vienna, AUSTRIA Phone +43/1/58801-5239, FAX +43/1/5059224 email: schrom@iue.tuwien.ac.at

#### Abstract

The fast growing portable-electronics market as well as thermal dissipation, reliability, and scalability issues have launched a massive trend towards low-power and low-voltage technologies. This has lead to a new, reduced standard digital CMOS supply voltage of 3.3V reducing the power consumption by 70%. However, the power consumption can still be cut down substantially by reducing the supply and threshold voltages much further without compromising systems performance. A loss in device speed can be compensated on the systems level by appropriate parallel architectures. Based on this concept of ultra-low-power CMOS technologies we explore the lower limits of CMOS supply voltage and switching energy for a variety of circuit classes analytically and numerically. Ultra-low-power (ULP) process and device design, device modeling, performance evaluation, and the specific problems associated with ULP mixed-analog-digital technologies are discussed.

### 1 Introduction

During the past two decades CMOS has emerged as the main-stream VLSI technology, and downscaling has greatly increased the systems performance, doubling the raw computing power every two years. Industry has long followed a strategy of constant-voltage scaling mainly to sustain the traditional standard supply voltage of 5V and to increase the performance without changing circuit design styles and systems architectures too much. However, as the minimum feature sizes entered the sub-micron regime, not only have reliability and process complexity become a major concern, but, above all, power consumption has turned out to be the key factor in modern high-performance technologies. The increased speed and packing density, i.e., performance per chip area, has been accompanied by an increase of heat generation to a point where the total chip performance is limited by the thermal dissipation capability of the mounted IC package. At the same time, the booming market of portable electronics, where battery life time is a major issue, called for new high-performance low-power technologies [1, 2, 3, 4, 5, 6].

In a typical CMOS technology the total power consumption is dominated by the dynamic power consumption, which is a square function of the supply voltage  $V_{DD}$  [7]

$$P = N f C V_{DD}^2, \tag{1}$$

where N is the number of switching gates, f is the clock frequency, and C is the average capacitance per gate. Nf can be taken as a performance measure. The circuit speed, on the

other hand, (and thereby the maximum clock frequency) increases only linearly with the supply voltage. For sub-micron devices operating at higher voltages this increase is even less because of velocity saturation.

By decreasing the supply voltage and adapting the threshold voltages, a significant reduction of the power consumption can be achieved at the expense of an increase in gate delay. This can be compensated to a certain extent by employing parallelism in the systems design so that, for the same overall performance, the total power consumption is drastically reduced compared to conventional CMOS technologies [3, 8, 9, 10]. The feasibility of this concept of ultra-low-power CMOS has been shown also by numerical process and device simulation [11, 12], and by experiments [13, 14, 15]. Mixed-analog-digital systems need special attention due to the different requirements of the analog part [4, 16, 17]. Minimum signal-to-noise ratio and distortion force a higher supply voltage. Yet, there is a large potential in ULP mixed-analog-digital CMOS [18].

## 2 Analytical Lower Bounds

Early work in this field was based on a minimum-inverter-gain criterion, and a minimum supply voltage of 200mV was found for inverters operating in weak inversion [15]. To determine an absolute lower bound of the supply voltage we assume MOSFETs operating completely in the weak inversion mode. The drain current is then given by [16]

$$I_D = I_0 e^{\frac{V_{GS}}{nU_T}} \left( 1 - e^{-\frac{V_{DS}}{U_T}} \right). \tag{2}$$

$I_0$  is determined by the technology and the channel width-to-length ratio W/L. For the following, we assume also an ideal gate swing of  $S = \ln(10)U_T$ , thus, n = 1. Setting  $I_{Dn} + I_{Dp} = 0$  with  $I_{0n} = I_{0p}$  yields an implicit equation for the transfer curve  $V_{out}(V_{in})$  of a symmetric inverter [19]

$$\frac{\sinh\left(\frac{V_{in}-V_{out}}{U_T}\right)}{\sinh\left(\frac{V_{in}-V_{DD}/2}{U_T}\right)} = e^{\frac{V_{DD}/2}{U_T}} \tag{3}$$

and the critical points where the voltage gain  $A = dV_{out}/dV_{in} = -1$  are determined by [7]

$$\frac{2\cosh\left(\frac{V_{in,c}-V_{out,c}}{U_T}\right)}{\cosh\left(\frac{V_{in,c}-V_{DD}/2}{U_T}\right)} = e^{\frac{V_{DD}/2}{U_T}},\tag{4}$$

from which the noise margins  $NM_H = NM_L = NM$  are computed as

$$NM = \frac{V_{DD} - V_{out,c} - V_{in,c}}{V_{DD}} \quad [\% V_{DD}]. \tag{5}$$

The maximum voltage gain which occurs at  $V_{in} = V_{out} = V_{DD}/2$  (cf. (12)) is given by

$$-A_{max} = e^{\frac{V_{DD}/2}{U_T}} - 1. (6)$$

Solving the equations (3) and (4) numerically, together with (2) and (6) yields noise margins and maximum gain as a function of the supply voltage.

For the design of digital circuits we have to impose certain constraints, i.e., to specify minimum values for NM and  $A_{max}$  at a nominal and maximum temperature and to estimate the impact of an effective unsymmetry  $F_U = W_n/W_p$  as a consequence of minimum-transistor-size design.

This is accounted for by a shift of the input voltage  $\Delta V_{in} = -U_T \ln(F_U)/2$ . Minimum supply voltages for various constraints are compiled in Table 1. For static logic with a fan-in of 3 the minimum  $V_{DD}$  is 83mV at 300K or 3.22 times the thermal voltage. Note that these numbers are absolute lower bounds which cannot likely be achieved with any CMOS process technology. Achievable values for  $V_{DDmin}$  may be estimated by scaling the numbers from Table 1 by a factor of  $n = S/(U_T \ln(10))$  where S is an achievable average gate swing. Although this is not consistent with (3) and (4), it can be used as a worst-case estimate for sub-threshold operation.

Table 1: Ideal-case minimum supply voltage  $V_{DD}$  for given of circuit design constraints

| constraint              |               | $V_{DDmin}$       | $V_{DDmin}$ |

|-------------------------|---------------|-------------------|-------------|

|                         |               | (T = 300 K)       | $[U_T]$     |

| $A_{max} > 1$           | (ring osc.)   | $36 \mathrm{mV}$  | 1.40        |

| NM > 10%                | (inverter)    | 55 mV             | 2.13        |

| $A_{max} > 4$           | (std. design) | $83 \mathrm{mV}$  | 3.22        |

| $F_U > 9$               | (fan-in = 3)  | $83 \mathrm{mV}$  | 3.22        |

| $I_{on}/I_{off} > 10^4$ | (dyn. logic)  | $238 \mathrm{mV}$ | 9.22        |

To determine a lower bound for the switching energy we regard only the intrinsic channel charge of a turned-on transistor (still operating in weak inversion)

$$Q_{on} = \frac{L^2 I_{on}}{\mu U_T},\tag{7}$$

where L is the effective channel length and  $\mu$  is the effective carrier mobility, and the turn-on current  $I_{on}$  for a given supply voltage is adjusted by the channel doping. If we now consider an inverter chain with each output node connected to the two gates of the following stage, and we neglect all other parasitics, then the charge of this node is altered by  $4Q_{on}$  during one clock period, so that the switching energy is given by

$$E_{s} = 4 \frac{Q_{on} V_{DD}}{2} = 2 \frac{L^{2} I_{on} V_{DD}}{\mu U_{T}}.$$

(8)

This means that the mere device physics does not limit the switching energy, because  $I_{on}$  can be chosen almost arbitrarily (disregarding design rules and tunneling effects). However, if we require a node to be charged with at least, say, 10 electrons then (taking  $V_{DDmin}$  for  $A_{max} > 4$  from Table 1) the switching energy is at least 0.13aJ. Another limit comes from the error rate in digital systems subject to thermal noise [10]

$$R_E = \frac{M}{t_g} e^{-\frac{E_s}{kT}},\tag{9}$$

where M is the number of gates and  $t_g$  is the gate delay, which is larger than the inverter delay

$$t_d > 2\frac{Q_{on}}{I_{on}} = 2\frac{L^2}{\mu U_T}. (10)$$

If we assume, e.g., a deep sub-micron technology with  $L=50 \mathrm{nm}$  and  $\mu \approx 500 \mathrm{cm}^2/\mathrm{Vs}$ , and a system with  $10^7$  gates requiring less than one error per year, then we get  $t_d > 4 \mathrm{ps}$  and  $E_s > 0.25 \mathrm{aJ}$ .

Of course, these values cannot be reached because of the parasitics, most important the gatedrain overlap, junction, and interconnect capacitances, that were not accounted for. When they are included the circuit speed becomes a function of  $I_{on}$ , making higher currents necessary to keep up the performance and they also add to the switching energy by  $CV_{DD}^2$ . Because the parasitics are largely technology dependent a simple general analysis is not possible. However, what can be seen from (8) is that the power efficiency scales as  $1/L^2$ , i.e., the benefit of ULP CMOS increases with downscaling.

## 3 Ultra-Low-Power Process Technology

As a consequence of the low voltages, ultra-low-power processes differ from conventional CMOS processes in several points: Because of the low  $V_{DD}$ , the hot-carrier problem virtually does not exist, and therefore an LDD (lightly doped drain) process is not necessary. Also, no GIDL (gate induced drain leakage), DIBL (drain induced barrier lowering) or latch-up can occur. Furthermore, because of the lower electric field mobility degradation and velocity saturation are greatly reduced. As a result, ULP CMOS processes are much better scalable compared to conventional processes.

The processes under consideration are recessed-well dual-gate processes with a very thin gate oxide (below 6nm) to achieve a good subthreshold behavior and to obtain controllably low threshold voltages. The source/drain doping is formed by single shallow implants and a conventional furnace anneal. The G/S and G/D overlap capacitances are controlled with a spacer formed prior to the S/D implants.

As for very low  $V_{DD}$  the devices must operate in the weak inversion regime, the difference of the carrier mobilities  $\mu_n, \mu_p$  can be roughly compensated by adjusting the threshold voltages to achieve symmetric inverter transfer characteristics. This compensation does not work, however, in the transient case because the speed is mainly determined by the strong-inversion part of the input characteristics. The sub-threshold behavior is crucial because it determines the achievable ratio of  $I_{on}/I_{off}$ , which is limited by  $\exp(V_{DD}/nU_T)$  and decreases as  $V_{Tn,p}$  are made smaller. Therefore, "zero- $V_T$ " transistors are not desirable at a very low  $V_{DD}$  of a few 100mV. On the other hand, if  $V_{Tn,p}$  are too high the speed becomes unacceptably low. As a rule of thumb [13], to maximize the performance the ratio  $I_{on}/I_{off}$  should be kept at a minimum value by adjusting  $V_{Tn,p}$  as  $V_{DD}$  is increased. This will also result in increased leakage currents but that is no problem as long as the total power consumption is kept at a minimum. In other words: leakage is a systems issue.

A major challenge is to achieve controllably low threshold voltages. Although the adjustment of  $V_{Tn,p}$  with a bulk bias seems very attractive, this method is not practical (using a traditional layout) because of the significant overhead due to the additional lines for bulk biasing. There are, however, alternative biasing and layout methods to overcome this problem [14].

Another problem can arise from the very thin gate insulator. Although devices with ultra-thin oxides have been successfully fabricated [20] thin oxides are susceptible to boron penetration causing a threshold shift. On the other hand, there are several options for the gate insulator. Nitrides or oxinitrides may prove good alternatives to conventional (pure SiO<sub>2</sub>) gate oxides [21, 22]. For "higher" supply voltages the demands on the subthreshold slope and hence on the oxide thickness can be relieved. In the future, fully depleted SOI may be the better choice, as it offers intrinsically good subthreshold behavior and smaller parasitics [23].

# 4 Numerical Performance Analysis

To determine feasible lower values of the supply voltage, a set of tuned CMOS processes was numerically analyzed by means of process and device simulation. The resulting device data were used for performance analysis on the circuit level [11, 12]. Both process and device simulation were done using the VISTA Technology CAD framework to allow for quick process design and evaluation [24, 25, 26]. For the electrical characterization of the devices MINIMOS [27, 28] was used to calculate a matrix of drain currents  $I_D(V_G, V_D)$  over a range of  $V_G$  and  $V_D$  for the p-channel and n-channel transistors. Based on these data, a fast and accurate table-driven DC analysis of simple gates and inverters is possible [12]. The dynamic behavior was estimated from capacitance data obtained by AC analysis with MINIMOS.

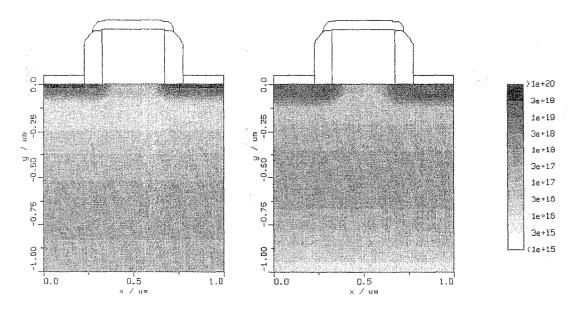

Figure 1: Doping profiles of ULP n-channel and p-channel transistors designed for digital operation at  $V_{DD} = 200 \text{mV}$  (process A)

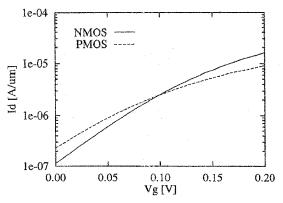

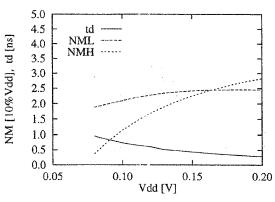

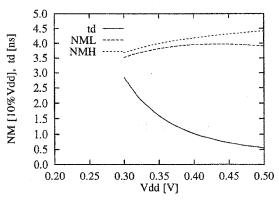

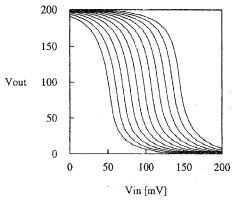

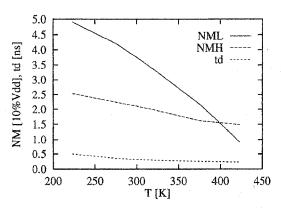

The simulated processes were a  $0.35\mu\mathrm{m}$  process (A) for static logic and a  $0.5\mu\mathrm{m}$  process (B) for dynamic logic. The processes were designed for proper DC characteristics but were not optimized for speed. The essential simulation results are compiled in Tables 2 and 3. The device characteristics for process A are shown in Figs. 2 and 3. Figs. 4 and 5 show the noise margins and the inverter delay as a function of the supply voltage. Figs. 6 and 7 show the inverter transfer curves and the temperature sensitivity of process A. It can be seen that a ring oscillator built with process A would work even at  $V_{DD} = 80\mathrm{mV}$ , and by using additional inverters at the gate inputs and outputs one could also design digital circuits for  $V_{DD} < 100\mathrm{mV}$ , but the overhead of the additional components would be considerable.

Table 2: Simulated device characteristics. The threshold voltage was defined as  $|I_D(V_T)| = 1\mu A/\mu m$ . All voltages are in V, all currents are in  $A/\mu m$

|     | process | $V_{DD}$ | $V_{T,n}$ | $V_{T,p}$ | $I_{off,n}$          | $I_{off,p}$         | $I_{on,n}$           | $I_{on,p}$           |

|-----|---------|----------|-----------|-----------|----------------------|---------------------|----------------------|----------------------|

|     | A       | 0.2      | 0.067     | -0.059    | $0.14 \cdot 10^{-6}$ |                     |                      | $9.4 \cdot 10^{-6}$  |

| - [ | В       | 0.5      | 0.26      | -0.24     | $0.7 \cdot 10^{-9}$  | $2.8 \cdot 10^{-9}$ | $25.6 \cdot 10^{-6}$ | $16.7 \cdot 10^{-6}$ |

Table 3: Noise margins (in  $\%V_{DD}$ ) for a simple inverter and a 3-input NAND gate, and inverter delay, leakage time, switching energy, and static power consumption

| process | $NM_{H,inv}$ | $\overline{NM_{L,inv}}$ | $NM_{H,gate}$ | $NM_{L,gate}$ | $t_d$              | $t_l$               | $E_s$              | $P_{stat}$        |

|---------|--------------|-------------------------|---------------|---------------|--------------------|---------------------|--------------------|-------------------|

| A       | 28           | 23                      | 13            | 39            | 0.29ns             | $7.2 \mathrm{ns}$   | $0.65 \mathrm{fJ}$ | 41nW              |

| В       | 38           | 44                      | 31            | 49            | $0.55 \mathrm{ns}$ | $1.3\mu \mathrm{s}$ | $4.3 \mathrm{fJ}$  | $0.88\mathrm{nW}$ |

To see how close the two processes are to the absolute lower limits for  $V_{DD}$  we define the factors  $X = V_{DD}/U_T$  and  $X_{crit} = V_{DDcrit}/U_T$ . Using (2) we get  $I_{on}/I_{off} = \exp(V_{DDeff}/U_T)$ , and we define

$$X_{eff} = \frac{V_{DDeff}}{U_T} = \ln \sqrt{\frac{I_{on,n}I_{on,p}}{I_{off,n}I_{off,p}}}.$$

(11)

20 18 16 14 [d [uA/um] 12 10 8 6 0.10 Vd [V] 0.15 0.00 0.05 0.20

$(V_{DD} = 200 \text{mV})$

Figure 2: Input characteristics, process A Figure 3: Output characteristics, process A  $(V_{DD} = 200 \text{mV})$

$V_{DD}$ , process A

Figure 4: Noise margins and delay time vs. Figure 5: Noise margins and delay time vs.  $V_{DD}$ , process B

Figure 6: Inverter transfer characteristics for Figure 7: Temperature sensitivity of process A  $W_n/W_p = 0.1...10$ , process A  $(V_{DD} = 200 \text{mV})$   $(V_{DD} = 200 \text{mV})$

These data are compiled for the two processes in Table 4: The ratio  $X/X_{crit}$  tells how close a technology is to the lower limit of  $V_{DD}$ , regardless of the circuit performance.  $X/X_{eff}$  tells the percentage of  $V_{DD}$  which is used up to fulfill the criterion (cf. Table 1); the remainder serves to increase the performance.  $X_{eff}/X_{crit}$  is an indirect measure for the sensitivity of a process (for process A the ratio is 1.31; a value below 1 would mean a violation of the criterion).

Table 4: Supply voltage utilization

| process | $V_{DD}$          | $V_{DDcrit}$      | X    | $X_{eff}$ | $X_{crit}$ |

|---------|-------------------|-------------------|------|-----------|------------|

| A       | 200mV             | $83 \mathrm{mV}$  | 7.8  | 4.2       | 3.2        |

| В       | $500 \mathrm{mV}$ | $238 \mathrm{mV}$ | 19.6 | 9.6       | 9.2        |

From these data we conclude that the limits for the supply voltage will be around 200mV for static logic and 500mV for dynamic logic with a fan-in of 3 at T = 300K.

## 5 Mixed-Analog-Digital Technology

The recent development of low-power CMOS technologies has brought up a growing discrepancy between analog and digital technologies, especially, concerning the supply and threshold voltages. Traditionally, analog micropower designs favor higher threshold voltages  $V_{Tn,p}$  and a supply voltage  $V_{DD} > 1 \text{V}$  [16], which is still higher than the end-of-discharge voltage of a single alkaline cell ( $\approx 0.9 \text{V}$ ) or the solar-cell voltage ( $\approx 0.4 \text{V}$ ). On the other hand, high-performance digital ultra-low-power technologies, requiring a comparatively small gain per stage, are optimized by lowering the supply voltage and the threshold voltages to a minimum.

For low-power mixed-analog-digital (MAD) systems it would be advantageous to have compatible ultra-low-voltage (ULV) analog components such as OPAMPs to keep the process technology simple. To find the lower limits of the supply voltage a set of basic circuits designed with dedicated digital ULP processes was simulated to determine the achievable performance.

To achieve an appropriate voltage gain almost all devices of ULV OPAMPs are operated in weak inversion (cf. (2)). An upper bound for the voltage gain of a single transistor loaded with an ideal current source can be derived as

$$A_{max} = \frac{1}{n} \left( e^{\frac{V_{DS}}{U_T}} - 1 \right). \tag{12}$$

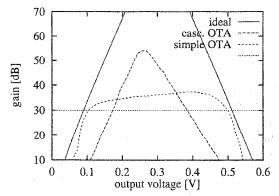

This means that the gain is mainly determined by the available voltage drop  $V_{DS}$  of the amplifying devices. Another limit to the gain originates from the (bipolar) Early effect of submicron devices:  $A \leq V_A/nU_T$ . Cascoding can reduce the Early conductance of sub-micron devices, but also decreases the available  $V_{DS}$ . For process B an improvement was found only for  $V_{DS} > 300 \text{mV}$ , i.e.,  $V_{DD} > 600 \text{mV}$ .

The MOSFET model used for circuit simulation is based on a physically motivated interpolation of the terminal currents and charges of the device [18]. These data are directly interfaced to a new circuit simulator, MINISIM [29], which uses charge conservative capacitance modeling. This approach avoids parameter fitting and rules out common problems like, e.g., discrepancies between the AC-model conductance parameters and the derivatives of the DC-model currents.

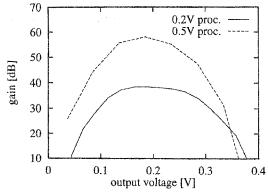

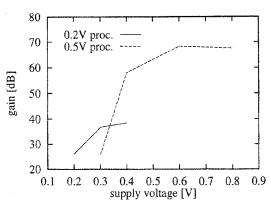

The simulation results of basic OPAMP types (OTA, folded-cascode OTA, and two-stage OPAMP) are shown in Figs. 8–13. We found that voltage gains of more than 60dB are possible at 0.5V and more than 38dB at 0.2V. The big advantage of this strategy is the compatibility of analog and digital devices which enables a simple ULP mixed-analog-digital process technology without compromizing performance on the systems level.

Figure 8: Voltage gain of two-stage ULV OPAMPs, operating at  $V_{DD}=0.4\mathrm{V}$  as a function of the output voltage (0.2V technology (a) and 0.5V technology (b))

Figure 9: Maximum gain of two-stage ULV OPAMPs, operating at  $V_{DD} = 0.4$ V as a function of the supply voltage (0.2V technology (a) and 0.5V technology (b))

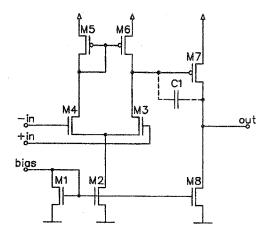

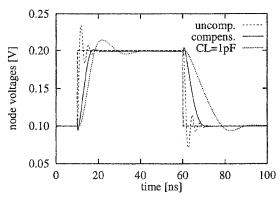

Figure 10: Two-stage OPAMP

Figure 11: Step response of a two-stage ULV OPAMP (0.2V ULP technology) operating as a unity gain buffer at  $V_{DD}=0.3\mathrm{V}$  (uncompensated (a), compensated (b), and with  $C_L=1\mathrm{pF}$ , compensated)

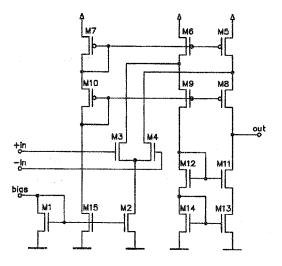

Figure 12: Folded-cascode OTA

Figure 13: Voltage gain of a simple OTA and a folded-cascode OTA (0.5V technology), operating at  $V_{DD}=0.6\mathrm{V}$  as a function of the output voltage

## 6 Conclusion

The possibilities to accomplish a substantial reduction of the power consumption of CMOS technologies without performance loss were discussed. Lower bounds for supply voltage and switching energy were found to be  $V_{DD} > 83 \,\mathrm{mV}$  and  $E_s > 0.25 \,\mathrm{aJ}$  at 300K. The feasibility of ULP CMOS technologies was demonstrated by numerical simulation. Also, analog components, implemented in a digital ULP technology, were shown to work well even below 0.5V. Considering the current standard low-power supply voltages and switching energies, as well as the excellent scalability of ULP CMOS technologies, power savings of several orders of magnitude can still be achieved.

### References

- [1] J. Borel. General Introduction, Motivation and Requirements for LV-LP IC's. In Borel et al. [30], pp 911-918.

- [2] D.P. Foty and E.J. Nowak. MOSFET Technology for Low-Voltage/Low-Power Applications. *IEEE Micro*, pp 68-77, 1994.

- [3] S. Malhi and P. Chatterjee. 1-V Microsystems-Scaling on Schedule for Personal Communications. *IEEE Circuits & Devices*, pp 13-17, 1994.

- [4] A. Matsuzawa. Low-Voltage and Low-Power Circuit Design for Mixed Analog/Digital Systems in Portable Equipment. *IEICE Trans. Electronics*, E77-C(5):800-810, 1994.

- [5] M.J. Riezenman. The Search for Better Batteries. IEEE Spectrum, pp 51-56, 1995.

- [6] Philips Semiconductors. Pager Applications Handbook, 1995.

- [7] N.H.E. Weste and K. Eshraghian. *Principles of CMOS VLSI Design*. Addison Wesley, second edition, 1993.

- [8] D. Liu and Ch. Svensson. Trading Speed for Low Power by Choice of Supply and Threshold Voltages. *IEEE J.Solid-State Circuits*, 28(1):10-17, 1993.

- [9] D. Liu. Low Power Digital CMOS Design. Dissertation, Dept. of Physics and Measurement Technology, Linköping University, 1994.

- [10] C. Svensson. High Speed and Low Power Techniques in CMOS and BiCMOS. In E.J.P. Santos and G.A.S. Machado, editors, *Proc. IV Brazilian Microelectronics School*, volume I, pp 265–287, Recife, 1995.

- [11] G. Schrom, D. Liu, Ch. Pichler, Ch. Svensson, and S. Selberherr. Analysis of Ultra-Low-Power CMOS with Process and Device Simulation. In C. Hill and P. Ashburn, editors, 24th European Solid State Device Research Conference ESSDERC'94, pp 679-682, Gifsur-Yvette Cedex, France, 1994. Editions Frontieres.

- [12] G. Schrom, D. Liu, C. Fischer, Ch. Pichler, Ch. Svensson, and S. Selberherr. VLSI Performance Analysis Method for Low-Voltage Circuit Operation. In G.L. Baldwin, Z. Li, C.C. Tsai, and J. Zhang, editors, Fourth Int. Conf. on Solid-State and Integrated-Circuit Technology, pp 328-330, Beijing, China, 1995.

- [13] J.B. Burr. Stanford Ultra Low Power CMOS. In Symposium Record, Hot Chips V, pp 7.4.1-7.4.12, 1993.

- [14] Jim Burr. High performance, low-voltage CMOS. In *IEEE Computer Elements Workshop*, pp 1.c.1-1.c.75, 1995. Vail, Co.

- [15] R.M. Swanson and J.D. Meindl. Ion-Implanted Complementary MOS Transistors in Low-Voltage Circuits. *IEEE J.Solid-State Circuits*, SC-7(2):146-153, 1972.

- [16] E.A. Vittoz. Design of Low-Voltage Low-Power IC's. In Borel et al. [30], pp 927-934.

- [17] J.E. Franca and Y. Tsividis, editors. Design of Analog-Digital VLSI Circuits for Telecommunications and Signal Processing. Prentice-Hall Inc., 2nd edition, 1994.

- [18] G. Schrom, A. Stach, and S. Selberherr. A Charge Based MOSFET Model for Low-Voltage Mixed-Signal Applications. In 26th European Solid State Device Research Conference ESSDERC'96, 1996. (To be published).

- [19] G. Schrom, Ch. Pichler, T. Simlinger, and S. Selberherr. On the Lower Bounds of CMOS Supply Voltage. Solid-State Electron., 39(4):425-430, 1996.

- [20] H.S. Momose, M. Ono, T. Yoshitomi, T. Ohguro, S. Nakamura, M. Saito, and H. Iwai. Tunneling Gate Oxide Approach to Ultra-High Current Drive in Small-Geometry MOSFETs. In *Int. Electron Devices Meeting*, pp 593–596, 1994.

- [21] T. Morimoto, H.S. Momose, S. Takagi, K. Yamabe, and H. Iwai. Ultrathin Nitride Gate MISFET Operating with Tunneling Gate Current. In Ext. Abstr. of the 22nd Conf. on Solid State Devices and Materials, pp 361-364, Sendai, 1990.

- [22] T. Morimoto, H.S. Momose, Y. Ozawa, K. Yamabe, and H. Iwai. Effects of Boron Penetration and Resultant Limitations to Ultra Thin Pure-Oxide and Nitrided-Oxide Gate-Films. In *Int. Electron Devices Meeting*, pp 429-432, 1990.

- [23] Y. Kado et al. Substantial Advantages of Fully-depleted CMOS/SIMOX Devices as Low-Power High-Performance VLSI Components Compared with its Bulk-CMOS Counterpart. In *Int. Electron Devices Meeting*, pp 635–638, 1995.

- [24] Ch. Pichler and S. Selberherr. Process Flow Representation within the VISTA Framework. In S. Selberherr, H. Stippel, and E. Strasser, editors, Simulation of Semiconductor Devices and Processes, volume 5, pp 25–28. Springer, 1993.

- [25] Ch. Pichler and S. Selberherr. Rapid Semiconductor Process Design within the VISTA Framework: Integration of Simulation Tools. In M.H. Hamza, editor, Proceedings of the IASTED International Conference, Modelling and Simulation, pp 147-150, Pittsburgh, PA, USA, 1993. The International Association of Science and Technology for Development.

- [26] S. Halama, Ch. Pichler, G. Rieger, G. Schrom, T. Simlinger, and S. Selberherr. VISTA— User Interface, Task Level, and Tool Integration. *IEEE Trans. Computer-Aided Design*, 14(10):1208-1222, 1995.

- [27] C. Fischer, P. Habaš, O. Heinreichsberger, H. Kosina, Ph. Lindorfer, P. Pichler, H. Pötzl, C. Sala, A. Schütz, S. Selberherr, M. Stiftinger, and M. Thurner. MINIMOS 6.0 User's Guide. Institute for Microelectronics, Technical University Vienna, 1994.

- [28] S. Selberherr and H. Kosina. Simulation of Nanometer MOS-Devices with MINIMOS. In 1990 VLSI Process/Device Modeling Workshop, pp 2-5, Kawasaki, Japan, 1990.

- [29] A. Stach. Simulation von MOSFET-Schaltungen. Diplomarbeit, Technische Universität Wien, 1995.

- [30] J. Borel, P. Gentil, J.P. Noblanc, A. Nouailhat, and M. Verdone, editors. Proc. 23rd European Solid State Device Research Conference - ESSDERC'93, Gif-sur-Yvette Cedex, France, 1993. Editions Frontieres.

# Acknowledgment

This work is supported by Austria Mikro Systeme AG, Unterpremstätten, Austria; Christian Doppler Gesellschaft, Vienna, Austria; Digital Equipment Corporation at Hudson, USA; Siemens Corporation at Munich, Germany; and Sony at Atsugi, Japan.