Microelectronics Journal 29 (1998) 529-534

Microelectronics

# An interpolation based MOSFET model for low-voltage applications

## Gerhard Schrom\*, Andreas Stach, Siegfried Selberherr

Institute for Microelectronics, TU Vienna, Gusshausstrasse 27-29, A-1040 Vienna, Austria

#### Abstract

The development towards lower voltages and even ultra-low power (ULP) technologies [J.B. Burr, Symposium Record, Hot Chips V, 1993, pp. 7.4.1–7.4.12; D. Liu, Ch. Svensson, IEEE J. Solid State Circuits 28(1)(1993) 10–17; G. Schrom et al., 24th European Solid State Device Research Conference—ESSDERC'94, 1994, pp. 679–682] makes ever higher demands on compact device model accuracy. We present a new approach to dynamic MOSFET modeling, which is especially suited for the simulation of low-voltage mixed analog digital circuits. The model is based on the interpolation of terminal charges and conductive currents which are determined from transient current/voltage data which can be obtained through measurement or simulation of the devices. Using this model, a variety of analog and digital circuits was simulated, and selected results were verified against device-level circuit simulations. © 1998 Elsevier Science Ltd. All rights reserved.

#### 1. Introduction

The concept of ultra-low power CMOS technology involves a substantial reduction of the supply and threshold voltages to reduce the power dissipation [11,13,14]. Parallel architectures are used to compensate for the speed reduction of individual gates, keeping up the overall systems performance. Going to very small voltages (well below 1 V), technology evaluation and optimization cannot just rely on traditional device parameters, but must be done at least on the circuit level. This requires very accurate device models for circuit simulation.

As a consequence of the low supply and threshold voltages, ULP devices operate in the transition region between weak and strong inversion, i.e. moderate inversion, which becomes predominant for the device behavior. Unfortunately though, this is a major weak point in most existing compact models. Similar problems arise when future VLSI technologies are to be investigated and the existing compact models are not yet refined to cover all relevant effects accurately.

The interpolation of terminal currents seems attractive, but very often the accuracy in the weak-inversion regime is insufficient. Early work in this field of so-called table look-up MOSFET modeling started with timing simulation [1,2], extending to general circuit simulation [3–5] and special techniques for scalability and data compression [6,7]. While these models serve well for strong inversion, no methods were given to handle the moderate and

weak-inversion regime with high accuracy, and capacitance modeling is essentially restricted to analytical models.

In this work, we follow a new approach based on a special interpolation of terminal currents and charges with physically motivated functions, i.e. piecewise polynomial and/or exponential splines. This method ensures that various physical effects are accounted for implicitly. Using a simple transient method for device characterization, the input data for the model can be obtained from measurements or simulations without any a priori knowledge and parameter fitting. The primary aim of the model is to render the behavior of a given device in a direct way to a circuit simulator to obtain accurate circuit performance data, which can then be related to process parameters. Consequently, physical interpretability is abandoned in favor of accuracy and generality of the model.

#### 2. Transient device characterization

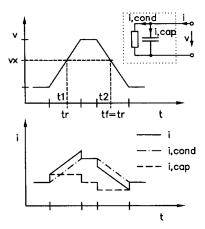

The input data to the model, i.e. terminal currents and charges for a set of terminal voltages, can be obtained either by measurements or process and device simulations. In this work we used VISTA with MINIMOS [8] to obtain the device data by simulation. All conductive currents can be obtained directly from DC measurements. The charge data are computed from transient simulations, as shown in Fig. 1 for the case of a two-pole: the device is modeled as a quasi static black box which is equivalent to a non-linear conductance parallel to a non-linear capacitance C(v) = dq/dv. Applying a symmetrical trapezoidal voltage v(t) to the

<sup>\*</sup> Author to whom correspondence should be addressed.

Fig. 1. Quasi-static black-box model of a two-pole: separation of capacitive and conductive currents

device will result in a current i(t) which can be separated into a conductive and capacitive component,

$$i_{\text{cond}}(v) = 1/2[i(t_1(v)) + i(t_2(v))];$$

(1)

$$i_{\text{cap}}(v) = 1/2[i(t_1(v)) - i(t_2(v))]$$

which is related to the charge by  $i_{cap}(v) = dq/dt = (dq/dv)$ . (dv/dt). Thus, the charge can be determined as

$$q(v) = q_0 + \int_{1^{V}}^{2_{V_0}} i_{\text{cap}}(u) du$$

(2)

The charge offset  $q_0$  can be determined from q(0) = 0. In the case of the MOSFET, we have a three-pole (assuming the source always grounded), one of the other terminals is ramped, and the currents at all terminals (including the ramped) are measured and subsequently converted to i/q-data.

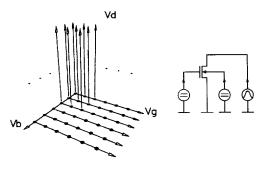

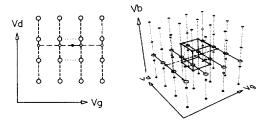

To obtain a complete field of charge data, including the charge offset, a series of transient measurements/simulations is required, as shown in Fig. 2. According to the desired ranges and step sizes of  $V_{\rm BS}$ ,  $V_{\rm GS}$  and  $V_{\rm DS}$ , one transient in the ' $V_{\rm B}$ -direction', n transients in the ' $V_{\rm G}$ -direction', and  $n \times m$  transients in the ' $V_{\rm D}$ -direction' are measured or simulated. The simulations in the ' $V_{\rm D}$ -direction' yield the main data set which is used for i/q extraction. The simulations in the ' $V_{\rm B}$ -direction' and ' $V_{\rm G}$ -direction' are required for the charge offset

Fig. 2. Transient MOSFET simulations/measurements

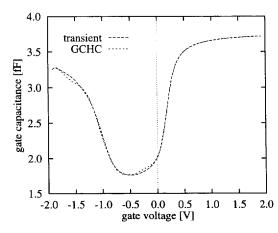

computation. The steepness of the ramp determines the accuracy of the charge data and the influence of non-stationary effects accordingly. Both can be verified with single transient measurements, using the i/q-extraction software. For the simulation with MINIMOS, the input decks are generated automatically according to the range settings which also control the computation of the current/charge data. Fig. 3 shows a comparison with gate capacitance data obtained from accurate gate charge simulations using MINIMOS. Typically, the number of required simulations is  $1 + n + nm = 1 + 5 + 5 \times 20 \sim O(100)$  with one simulation taking several minutes. The task can be run in parallel [8] so that characterization of one device requires less than 1 h.

#### 3. Model function and simulation environment

The model function is based on a physically motivated interpolation of the terminal currents and charges of the device. The interpolation also supplies the derivatives, i.e. the conductance and capacitance matrices of the device. These data are directly interfaced to a new circuit simulator, MINISIM [9], which uses charge conservative capacitance modeling.

This approach rules out common problems, e.g. discrepancies between the AC-model conductance parameters and the derivatives of the DC-model currents.

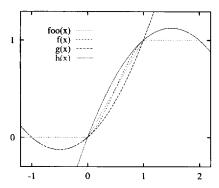

The interpolation uses piecewise polynomial and/or exponential splines in each dimension (e.g.  $V_{\rm B}$ ,  $V_{\rm D}$ : polynomial;  $V_{\rm G}$ : exponential) to account for the physical nature of the quantities (especially the exponential dependence of the currents). The interpolation functions have the following form:

$$x < 0: f(x) = g(x) \tag{3}$$

$$0 \le x \le 1$$

:  $f(x) = (1 - x).g(x) + x.h(x)$

$$x > 1 : f(x) = h(x)$$

where the interval [0, 1] is the transformed target interval.

Fig. 3. Gate capacitance of an ULP n-channel MOSFET ( $V_{\rm BS}=0~{\rm V}$ ) determined with the transient method ( $t_{\rm r}=3~{\rm ns}$ ) and computed through accurate gate charge integration using MINIMOS's 'GCHC' option

Fig. 4. Construction of the interpolation function f(x) from the functions g(x) and h(x) to interpolate the function f(x) in the interval [0, 1]

The functions g and h depend on the type of the interpolation (cf. also Fig. 4):

polynomial:

$$g(x) = a_0 + a_1 x + a_2 x^2$$

,  $h(x)$ : dto (4)

exponential:  $g(x) = a_0 + a_1 e^{a_2 x}$ , h(x): dto

This ensures a continuous derivative, which is essential for simulator convergency. The exponential splines exhibit excellent extrapolation properties in the subthreshold region.

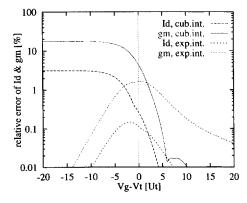

To determine the accuracy of the model, equation (5) was used as a test function (cf. the EKV model [10]). The worst-case interpolation error, i.e. the  $L_{\infty}$  norm of the relative error, was determined numerically as a function of the gate voltage (cf. Fig. 5). The modified exponential interpolation is clearly better than the cubic one, yielding an error of < 0.2% for the function value and < 2.0% for the derivative.

$$I_{\rm D} = I_{\rm s} \ln^2 \left( 1 + e^{\frac{V_{\rm GS} - V_{\rm T}}{2U_{\rm T}}} \right)$$

(5)

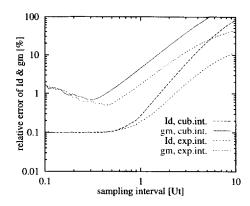

As can be seen, the moderate-inversion region  $(V_G \sim V_T)$  is most critical. Fig. 6 shows the influence of noisy data on the interpolation error depending on the sampling interval. For a very small data sampling interval,  $\Delta V$ , the error of the

Fig. 5. Worst-case interpolation error of  $I_{\rm D}$  and  $g_{\rm m}$  using  $I_{\rm D} = I_{\rm s} \ln^2 \left(1 + {\rm e} \frac{V_{\rm cs} - V_{\rm T}}{2U_{\rm T}}\right)$  as test function and a data sampling interval of  $1.U_{\rm T}$

Fig. 6. Worst-case interpolation error of  $I_D$  and  $g_m$  versus the data sampling interval for noisy data (n=0.1%)

derivative actually increases as  $1/\Delta V$ . In practice, optimum values for  $\Delta V$  are about 1-2 thermal voltages.

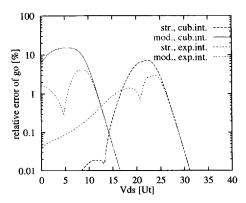

The maximum error of the output conductance  $g_0$  was determined numerically, using the following test expression:

$$I_{\rm D} = I_{\rm s} \left[ \ln^2 \left( 1 + e^{\frac{V_{\rm GS} - V_{\rm T}}{2U_{\rm T}}} \right) - \ln^2 \left( 1 + e^{\frac{V_{\rm GS} - V_{\rm T} - V_{\rm DS}}{2U_{\rm T}}} \right) \right] (1 + \lambda V_{\rm DS})$$

(6)

with  $\lambda = 1/100 \text{ V}$  for long-channel transistors. The results are shown in Fig. 7: in strong inversion, the critical range of  $V_{\rm DS}$  lies in the vicinity  $V_{\rm DS,sat}$ , i.e. the transition between the linear and saturation region. In moderate to weak inversion, where the output curve becomes exponential, the critical range is 0 V to several  $U_{\rm T}$ . In the critical  $V_{\rm DS}$  range, the modified exponential interpolation with a maximum error of 4% performs better than the polynomial one. This may be important for some devices in analog circuits.

It is important to note that, although the polynomial interpolation used here is generally not monotonic for monotonic samples, the maximum error of the derivatives is well below

Fig. 7. Worst-case interpolation error of  $g_0 = \partial I_D/\partial V_{DS}$  in moderate inversion  $(V_{GS} - V_T = 0 \text{ V})$  and strong inversion  $(V_{GS} - V_T = 20U_T)$  [sampling interval =  $1U_T$ ]

Fig. 8. Interpolation in two and three dimensions

100%. This is due to the fact that—apart from breakdown phenomena—terminal quantities of a MOSFET and their derivatives cannot quickly change arbitrarily with respect to the terminal voltages. Using equations (5) and (6), it can be shown that non-monotonicity cannot occur for a sampling interval of less than  $1.94U_{\rm T}$ .

These one-dimensional interpolations are then combined to a two- or three-dimensional interpolation by nesting as shown in Fig. 8. A full three-dimensional interpolation requires 64 supporting data points around the target interval. First, the data are interpolated in the bulk-direction for 16 points in the  $V_D$ - $V_G$  plane for the given  $V_B$ : second, the data are interpolated in the drain-direction for four points on the  $V_G$  line for the given  $V_D$ ; and last, an interpolation is performed in the gate-direction for the given  $V_G$ . This algorithm is also employed for the computation of the derivatives. Although the partial interpolation of the derivatives is generally not consistent with the exact computation, the relative errors were found to be marginal ( $< 10^{-4}$ ). The actual algorithm uses extensive pre-computation of polynomial coefficients to ensure high CPU efficiency of the program.

In the current implementation, one call to the model function takes  $76 \mu s$  on an HP-PA 735 workstation.

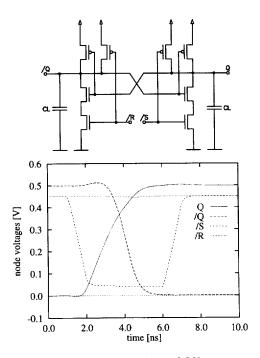

Fig. 9. RS flip-flop switching transients  $V_{\rm DD} = 0.5~{\rm V}$

The memory consumption, taking typical numbers of  $5 \times 20 \times 20 = 2000$  data points in  $V_{\rm BS}$ ,  $V_{\rm GS}$  and  $V_{\rm DS}$  directions, is about 80 kbytes per transistor type. Precomputed coefficients and decision flags could also be stored to speed up the execution at the expense of a higher memory consumption.

#### 4. Applications

Fig. 9 shows the simulated switching transients of an RS flip-flop designed in a 0.5 V ultra-low power technology [11]. The same technology can be used to build OPAMPs, operating at even lower supply voltages.

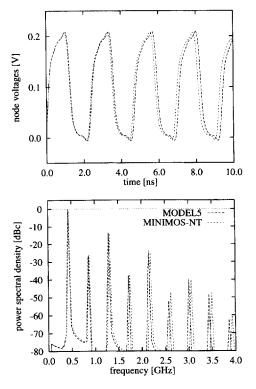

In Fig. 10, simulation results of a ring-oscillator obtained with this model are compared against device-level simulations of the circuit with MINIMOS-NT [12]. The frequency error is 1.7% and the amplitude error is  $< 2 \, \mathrm{dB}$  (1st-5th harmonic).

Due to its inherent accuracy, our new model could show the feasibility of ultra-low power OPAMPs working at supply voltages well below 1 V. To find the lower limits of the supply voltage, a set of basic circuits designed with dedicated digital ultra-low power (ULP) processes was simulated to determine the achievable performance.

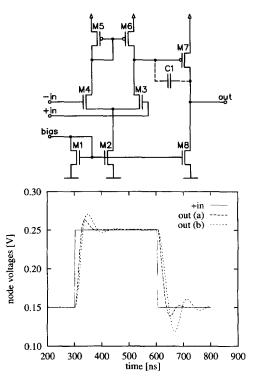

Fig. 11 shows the simulated large signal step response of a two-stage OPAMP operating as a follower at  $V_{\rm DD} = 0.4~\rm V$  for two different loads. The frequency compensation is accomplished by wider output transistors (M7, M8), utilizing their internal capacitances rather than a separate

Fig. 10. Five-stage ring oscillator 0.2 V ULP technology: circuit simulation MODEL5 versus device-level simulation MINIMOS-NT

Fig. 11. Large-signal step response of a two-stage ULP OPAMP with a self-compensating output stage operating as a follower at  $V_{\rm DD}=0.4~{\rm V}$  with (a)  $C_{\rm L}=0~{\rm pF}$  and (b)  $C_{\rm L}=1~{\rm pF}$

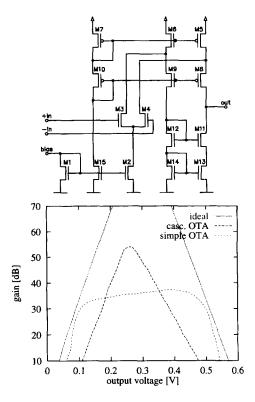

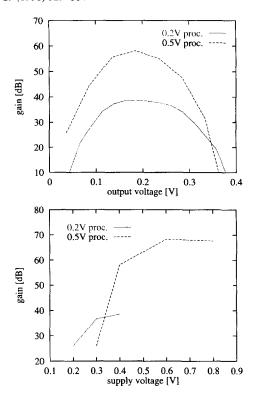

Fig. 12. Voltage gain of a simple OTA and a folded-cascode OTA (0.5 V technology), operating at  $V_{\rm DD}=0.6$  V as a function of the output voltage

Fig. 13. Voltage gain versus  $V_{\rm out}$  and maximum voltage gain versus  $V_{\rm DD}$  of two-stage ULV OPAMPs operating at  $V_{\rm DD}=0.4~{\rm V}$  as a function of the output voltage [0.2 V technology (a) and 0.5 V technology (b)]

capacitor (C1). The OPAMP is biased for medium speed, consuming a total of 4.0  $\mu$ W. Results from OTA simulations are shown in Fig. 12, indicating that cascoding is limited to  $V_{\rm DD} > 0.6$  V. Fig. 13 shows the achievable maximum voltage gain of two-stage OPAMPs, indicating that  $V_{\rm DD} = 0.5$  V could be a practical value for low-voltage mixed-analog-digital applications.

#### 5. Conclusion

Our new low-voltage MOSFET modeling approach, together with the supporting software, enables the accurate simulation of modern mixed-analog-digital circuits directly from measured or simulated data. This can be profitably used for process evaluation and optimization on the circuit level without intermediate parameter fitting.

### Acknowledgements

Our work is significantly supported by Intel Corp., Hillsboro, OR, USA; Austria Mikro Systeme AG, Unterpremstätten, Austria; Christian Doppler Gesellschaft, Vienna, Austria; and Siemens Corporation at Munich, Germany.

#### References

- [1] B.R. Chawla, H.K. Gummel, P. Kozak, MOTIS—an MOS timing simulator, IEEE Trans. Circuits and Systems CAS-22 (12) (1975)

- [2] S.P. Fan, M.Y. Hseuh, A.R. Newton, D.O. Pederson, MOTIS-C: a new circuit simulator for MOS LSI circuits, in: Proc. Int. Symp. Circuits and Systems, IEEE, 1977, pp. 700-703.

- [3] T. Shima, Ts. Sugawara, S. Moriyama, H. Yamada, Three-dimensional table look-up MOSFET model for precise circuit simulation, IEEE J. Solid-State Circuits CS-17 (3) (1982) 449-454.

- [4] T. Shima, H. Yamada, R.L.M. Dang, Table look-up MOSFET modeling system using a 2-D device simulator and monotonic piecewise cubic interpolation, IEEE Trans. Computer-Aided Design CAD-2 (2) (1983) 121-126.

- [5] W.M. Coughran, E. Grosse, D.J. Rose, CAzM: a circuit analyzer with macromodeling, IEEE Trans. Electron Devices ED-30 (9) (1983) 1207–1213.

- [6] M.G. Graham, J.J. Paulos, Interpolation of MOSFET table data in width length, and temperature, IEEE Trans. Computer-Aided Design 12 (12) (1993) 1880-1884.

- [7] M.G. Graham, J.J. Paulos, D.W. Nychka, Template-based MOSFET device model, IEEE Trans. Computer-Aided Design 14 (8) (1995) 924–933.

- [8] Ch. Pichler, S. Selberherr, Process flow representation within the VISTA framework, in: S. Selberherr, H. Stippel, E. Strasser (Eds.), Simulation of Semiconductor Devices and Processes, Vol. 5, Springer, Wien, 1993, pp. 25-28.

- [9] A. Stach, Simulation von MOSFET-Schaltungen. Diplomarbeit, Technische Universität Wien, 1995.

- [10] G.A.S. Machado (Ed.), Low-Power HF Microelectronics A Unified Approach. IEE, London, 1996.

- [11] G. Schrom, D. Liu, Ch. Pichler, Ch. Svensson, S. Selberherr, Analysis of ultralow-power CMOS with process and device simulation, in: C. Hill, P. Ashburn (Eds.), 24th European Solid State Device Research Conference—ESSDERC'94, Gif-sur-Yvette Cedex, France, 1994, Editions Frontieres, pp. 679-682.

- [12] T. Simlinger, H. Kosina, M. Rottinger, S. Selberherr, MINIMOS-NT: a generic simulator for complex semiconductor devices, in: H.C. de Graaff, H. van Kranenburg (Eds), ESSDERC'95—25th European Solid State Device Research Conference, Gif-sur-Yvette Cedex, France, 1995, Editions Frontieres, pp. 83–86.

- [13] J.B. Burr, Stanford ultra low power CMOS, in Symposium Record, Hot Chips V, 1993, pp. 7.4.1-7.4.12.

- [14] D. Liu, Ch. Svensson, Trading speed for low power by choice of supply and threshold voltages, IEEE J. Solid-State Circuits 28 (1) (1993) 10-17.