## EFFECTIVENESS OF SILICON NITRIDE PASSIVATION IN III-V BASED HBTS

V. Palankovski<sup>1</sup>, R. Schultheis<sup>2</sup>, A. Bonacina<sup>2</sup>, and S. Selberherr<sup>1</sup>

<sup>1</sup>Institute for Microelectronics, TU Vienna, Gusshausstr. 27–29, A-1040 Vienna, Austria

<sup>2</sup>Infineon Technologies AG, Otto-Hahn-Ring 6, D-81730 Munich, Germany

The quality of  $Si_3N_4$  thin film passivation is of crucial importance for the reliability of III-V based Heterojunction Bipolar Transistors (HBTs). Both theoretical and experimental studies have been conducted in order to minimize base leakage currents as a major source of degradation (e.g. see [1] and the references therein). In the present work we study the effectiveness of the passivation of devices before and after both electrical and thermal stress aging.

We focus on one of the few devices which, as an exception, showed an early degradation under conditions far beyond the normal device operating conditions. The strong increase in the base leakage current of the one-finger power InGaP/GaAs HBT was investigated by the means of two-dimensional numerical simulations. For that purpose, proper electrical and thermal models were implemented in our simulator MINIMOS-NT [2] allowing simulation of  $Si_3N_4$  as a wide bandgap semiconductor material.

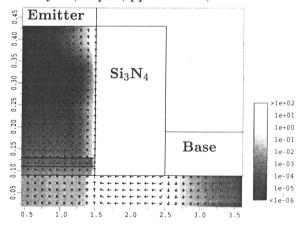

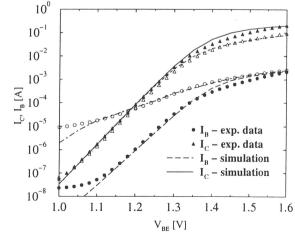

The simulation results suppose that during stress some of the electrons flowing in the emitter are injected in the insulator and get trapped. The negative charge at semiconductor/insulator interface and respectively the surface potential are increased. Thus, a leakage path for the holes occurs in the vicinity of the interface (see Fig. 1). In Fig. 2 a comparison of measured and simulated forward Gummel plots at  $V_{CB}=0$  V is shown. Filled and open symbols denote measured characteristics of the non-degraded and degraded device, respectively. The corresponding simulation results are shown with lines.

- [1] K. Christianson, "Reliability of III-V Based Heterojunction Bipolar Transistors," *Microelectronics Reliability*, vol. 38, no. 1, pp. 153–161, 1997.

- [2] V. Palankovski, S. Selberherr, and R. Schultheis, "Simulation of Heterojunction Bipolar Transistors on Gallium-Arsenide," in *Simulation of Semiconductor Processes and Devices*, Kyoto, Japan, pp. 227–230, 1999.

Figure 1: Hole current density  $[A/cm^2]$ . Leakage path near the  $Si_3N_4$  interface.

Figure 2: Forward Gummel plots at  $V_{CB} = 0$  V. Comparison with measurements.