## Analysis of Gate Dielectric Stacks Using the Transmitting Boundary Method

A. Gehring, H. Kosina, and S. Selberherr

Institute for Microelectronics, TU Vienna, Gusshausstrasse 27–29, Vienna, Austria Phone: +43-1-58801/36016, Fax: +43-1-58801/36099, Email: Gehring@iue.tuwien.ac.at

Gate stacks of high- $\kappa$  dielectrics have been proposed to enable MOSFET effective oxide thickness scaling below 2 nm. Simulation of such devices requires the calculation of tunneling through non-triangular energy barriers. The tunneling current through an energy barrier of arbitrary shape is

$$J_{g} = \frac{4\pi m_{\text{eff}} q}{h^{3}} \int_{0}^{\infty} TC(\mathcal{E}_{t}) \int_{0}^{\infty} \left[ f_{1}(\mathcal{E}_{t} + \mathcal{E}_{l}) - f_{2}(\mathcal{E}_{t} + \mathcal{E}_{l} + \Delta \mathcal{E}_{C}) \right] d\mathcal{E}_{l} d\mathcal{E}_{t}$$

(1)

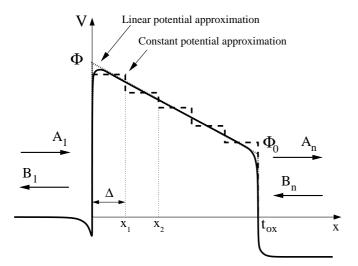

where  $TC(\mathcal{E}_t)$  is the transmission coefficient,  $\mathcal{E}_l$  and  $\mathcal{E}_t$  the longitudinal and transversal energy component,  $f_1$  and  $f_2$  the energy distribution functions in the gate and substrate, and  $\Delta \mathcal{E}_C$  the difference in the conduction band edges. The quantum-mechanical transmission coefficient can be derived using several techniques. While the WKB and Gundlach methods assume a triangular or trapezoidal barrier, the transfer-matrix method is based on a segmentation of an arbitrary-shaped energy barrier into a series of constant- or linear-potential segments as shown in Fig. 1. Alternatively, the quantum transmitting boundary method (QTBM) can be used, where open boundary conditions are introduced by [1]

$$\Psi_{1} = a_{1} + b_{1}, \quad \Psi_{0} = a_{1} \exp(-ik_{1}\Delta) + b_{1} \exp(ik_{1}\Delta)

\Psi_{n} = a_{n} + b_{n}, \quad \Psi_{n+1} = a_{n} \exp(-ik_{n}\Delta) + b_{n} \exp(ik_{n}\Delta)$$

(2)

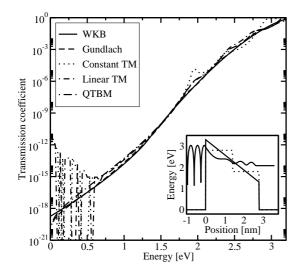

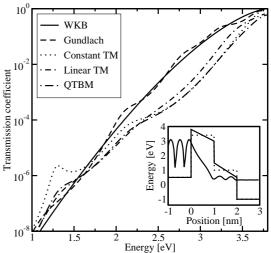

which allow Schrödinger's equation to be solved by standard techniques. The different numerical methods have been compared to study their applicability for the evaluation of high- $\kappa$  dielectric stacks. Fig. 2 shows the transmission coefficient of a typical 2 nm stack, with the shape of the barrier and the squared wave function at an energy of 2.8 eV in the inset. The WKB and Gundlach methods, which approximate the barrier with a straight line, overestimate the transmission coefficient as compared to the transfer-matrix based methods, which show good agreement with the transmitting boundary method. The transfer-matrix based methods, however, cannot be used for thicker dielectrics as shown in Fig. 3 for a 3 nm SiO<sub>2</sub> gate oxide due to numerical instabilities at low energies ( $\approx 0.6 \,\mathrm{eV}$  in this case). It was found that these methods become unstable due to rounding errors if the decay factor  $\sum k_j \Delta$  exceeds a certain value ( $\approx 20$  in our simulations).

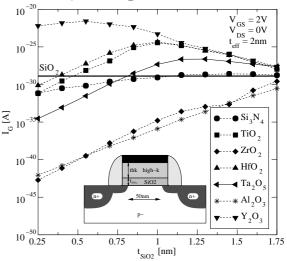

The transmitting boundary method, on the other hand, delivers accurate results and remains stable even for large stacks. It has therefore been implemented into the device simulator MINIMOS-NT and applied for the evaluation of gate dielectric stacks in a 50 nm 'well-tempered' MOSFET [2]. Retaining the effective gate oxide thickness of 2 nm we replaced the dielectric by a stack consisting of an underlying SiO<sub>2</sub> layer and a high- $\kappa$  dielectric on top. The electron concentration in the stack (see Fig. 4) was taken into account in the Poisson equation. Using the material parameters listed in Fig. 5 the gate current was calculated at the bias point  $V_{\rm DS}{=}0\,{\rm V}$  and  $V_{\rm GS}{=}2\,{\rm V}$  for different thicknesses of the SiO<sub>2</sub> layer, see Fig. 6. Most of the materials yield even an increased gate current which can be explained by the trade-off between barrier height and barrier thickness. Only ZrO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> show considerably lower leakage than SiO<sub>2</sub> and may therefore be considered as viable high- $\kappa$  dielectrics for future CMOS technologies.

## REFERENCES

- [1] W. R. Frensley, Superlattices & Microstructures 11, 347 (1992).

- [2] D. Antoniadis et al., "Well-Tempered" Bulk-Si NMOSFET Device Home Page, http://www-mtl.mit.edu/Well/.

- [3] J. Zhang et al., Solid-State Electron. 44, 2165 (2000).

- [4] J. D. Casperson et al., J.Appl.Phys. 92, 261 (2002).

**Figure 1:** The energy barrier for the linear and constant potential transfer-matrix method.

Figure 3: Transmission coefficient as a function of energy for a 3 nm thick layer of  $SiO_2$ .

|                                 | $\kappa$           | Band gap | Band offset |

|---------------------------------|--------------------|----------|-------------|

|                                 | $[\mathrm{As/Vm}]$ | [eV]     | [eV]        |

| Si                              | 11.9               | 1.17     |             |

| $\mathrm{SiO}_2$                | 3.9                | 9.00     | 3.18        |

| $\mathrm{Si}_{3}\mathrm{N}_{4}$ | 7.5                | 5.00     | 2.00        |

| $Ta_2O_5$                       | 25.0               | 4.40     | 1.40        |

| ${ m TiO_2}$                    | 40.0               | 3.50     | 1.10        |

| $Al_2O_3$                       | 7.9                | 5.60     | 3.50        |

| $\rm ZrO_2$                     | 25.0               | 7.80     | 1.90        |

| $HfO_2$                         | 25.0               | 5.80     | 1.13        |

| $Y_2O_3$                        | 18.0               | 5.50     | 1.30        |

**Figure 5:** Material parameters of commonly used dielectrics, compared to silicon [3, 4].

**Figure 2:** Transmission coefficient as a function of energy for a typical gate stack.

Figure 4: The electron concentration in a  $SiO_2$ - $Si_3N_4$ - $SiO_2$  gate stack.

Figure 6: Gate current as a function of  $SiO_2$  layer thickness at  $V_{DS} = 0 \text{ V}$  and  $V_{GS} = 2 \text{ V}$ .