# Direct S-Parameter Extraction by Physical Two-Dimensional Device AC-Simulation

V Palankovski, S Wagner, T Grasser, R Schultheis\*, and S Selberherr

Institute for Microelectronics, Technical University Vienna,

Gusshausstrasse 27-29, A-1040 Vienna, Austria

\*Infineon Technologies AG, Wireless Products, Technology and Innovations, Otto-Hahn-Ring 6, D-81730 Munich, Germany

**Abstract.** We present results from fully two-dimensional physical device simulation. Scattering parameters (S-parameters) are directly obtained from small-signal AC-analysis of real heterostructure devices. A comparison reveals very good agreement with measured data.

#### 1. Introduction

Heterojunction Bipolar Transistors (HBTs) are among the most advanced semiconductor devices today. Two-dimensional device simulation proved to be valuable for understanding the underlying device physics [1] and for improving the device reliability [2]. Bias-dependent S-parameters hold the full small-signal RF-information about the device behavior and allow process control beyond the information about the DC-quantities.

There are several approaches to compute bias-dependent S-parameters, e.g. [3,4], applying quasi-static or equivalent-circuit parameter models. These approaches employ transformations in the time domain to extract S-parameters. All these methods are both more CPU-time consuming (steady-state has to be reached for each bias and frequency) and more inaccurate (only a limited number of time-steps in reasonable CPU-time, equivalent-circuit approximation, etc.) compared to AC-analysis [5].

We implemented a feature for direct extraction of either extrinsic or intrinsic (deembedded) S-parameters from AC-simulation in the three-dimensional device simulator Minimos-NT [6]. Thus, we use a combination of rigorous III-V group and IV group semiconductor materials modeling and the ability to simulate in the frequency domain.

### 2. Physical models in Minimos-NT

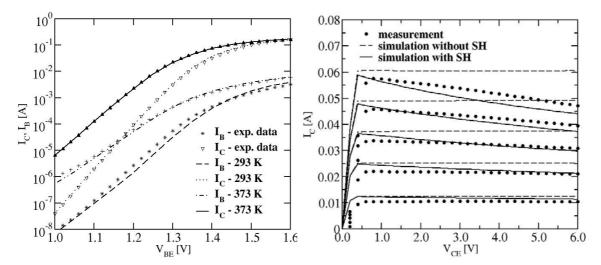

Minimos-NT deals with different complex structures and materials, such as Si, Ge, GaAs, AlAs, InAs, GaP, InP, their alloys and non-ideal dielectrics. Various important physical effects, such as bandgap narrowing, surface recombination, transient trap recombination, self-heating, and hot electron effects, are taken into account. The models are based on experimental or Monte Carlo simulation data and cover the whole material composition range. The model parameters in Minimos-NT are checked against several independent HEMT and HBT technologies to obtain one concise set used in all simulations. Efficiency is proven by hydrodynamic DC-simulations with self-heating, e.g. see Fig. 1.

**Figure 1**. Forward Gummel plots at  $V_{CB} = 0$  V for GaAs HBT (left): Comparison with measurement data at 293 K and 373 K. Output characteristics (right): Simulation with and without self-heating (SH) compared to measurement data at constant  $I_B$  stepped from 0.1 to 0.5 mA.

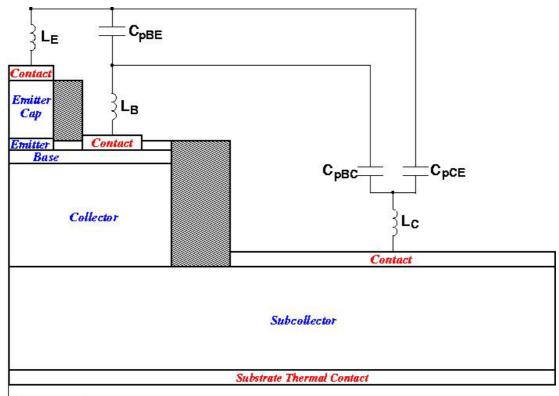

## 3. Simulation example

By means of two-dimensional device AC-simulation, we extracted the S-parameters for a one-finger InGaP/GaAs HBT with emitter area of 3  $\mu$ m  $\times$  30  $\mu$ m. Fig. 2 shows the simulated device structure and the pad parasitics (capacitances and inductances) in the two-port pad parasitic equivalent circuit, which is used to transform the intrinsic parameters to extrinsic ones. The parasitics result from measurements of open/short thru-test-structures [7]. Thus, the pad capacitances are  $C_{pBE} = 150$  fF,  $C_{pCE} = 75$  fF, and  $C_{pBC} = 24$  fF, while the parasitic inductance values are  $L_E = 1$  pH,  $L_B = 75$  pH, and  $L_C = 50$  pH. Any resistive parasitics are neglected, since we consider a rather small device and, therefore, only low currents.

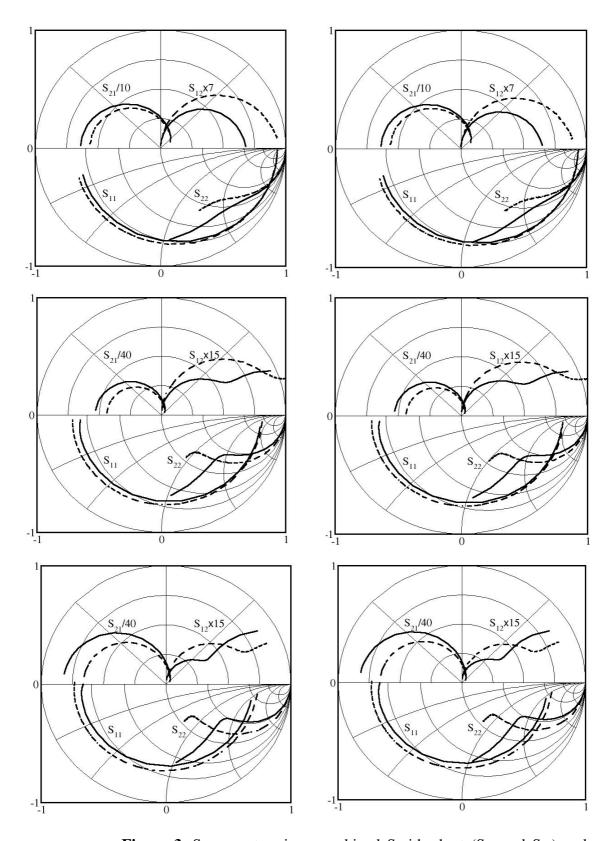

The combined smith/polar charts in Fig. 3 show a comparison of simulated and measured S-parameters at  $V_{CE} = 3$  V and  $V_{CE} = 3.5$  V, with current densities  $J_C = 2 \times 10^3$  A/cm<sup>2</sup>,  $J_C = 8 \times 10^3$  A/cm<sup>2</sup>, and  $J_C = 15 \times 10^3$  A/cm<sup>2</sup>, respectively, for the frequency range between 50 MHz and 10 GHz.

#### 4. Computational effort

The AC-simulation takes about 200 s CPU-time on a 2.4 GHz Linux Pentium machine for S-parameters computation with 20 frequency steps. For comparison, the conventional small-signal equivalent-circuit approach [3] takes about 590 s CPU-time at the same machine for 200 time steps at a given frequency. The time for post-processing of the transient simulation results to obtain the S-parameters at all frequencies is not included.

#### 5. Conclusion

The good agreement with measured data and the speed-up achieved demonstrate the quality and the efficiency of our approach. At this instance, the shown approach enables further extensive optimization tasks with hundreds of runs in a reasonable time. We expect almost perfect match between simulated and measured S-parameters, as it has already been demonstrated for such devices by applying the standard small-signal equivalent-circuit modeling approach [7]. In addition, the two-dimensional physical simulation allows for a direct relation between the material properties and the high-frequency device behavior.

Symmetry axis

**Figure 2**. Simulated device structure together with pad parasitics used for S-parameter calculation.

# Acknowledgment

The authors acknowledge inputs from R. Quay and K. Dragosits.

## References

- [1] Palankovski V, Selberherr S, Quay R, and Schultheis R, "Analysis of HBT Degradation After Electrothermal Stress", 2000 in Simulation of Semiconductor Processes and Devices (Seattle) p.245-248

- [2] Palankovski V, Schultheis R, and Selberherr S, "Simulation of Power Heterojunction Bipolar Transistors on Gallium Arsenide", 2001 IEEE Trans. Electron Devices, vol.48, no.6, p.1264-1269

- [3] Quay R, Reuter R, Palankovski V, and Selberherr S, "S-Parameter Simulation of RF-HEMTs", 1998 in EDMO (Manchester), p.13-18

- [4] Anholt R, "HBT S-Parameter Computations Using G-PISCES-2B", 1999 GaAs Simulation and Analysis News, no.4, p.1-4

- [5] Laux S, "Techniques for Small-Signal Analysis of Semiconductor Devices", 1986 IEEE Trans. Electron Devices, vol.ED-32, no.10, p.2028-2037

- [6] Palankovski V, Quay R, and Selberherr S, "Industrial Application of Heterostructure Device Simulation", 2001 IEEE J. Solid-State Circuits, vol.36, no.9, p.1365-1370 (invited)

- [7] Schultheis R, Bovolon N, Mueller J-E, and Zwicknagl P, "Modelling of Heterojunction Bipolar Transistors (HBTs) Based on Gallium Arsenide (GaAs)", 2000 Intl.J. of RF and Microwave Computer-Aided Engineering, vol.10, no.1, p.33-42

**Figure 3**. S-parameters in a combined Smith chart ( $S_{11}$  and  $S_{22}$ ) and a polar graph ( $S_{21}$  and  $S_{12}$ ) from 50 MHz to 10 GHz at  $V_{CE}=3$  V (left column) and  $V_{CE}=3.5$  V (right column),  $J_C=2\times10^3$  A/cm<sup>2</sup> (row 1),  $J_C=8\times10^3$  A/cm<sup>2</sup> (row 2), and  $J_C=15\times10^3$  A/cm<sup>2</sup> (row 3): Simulation (solid lines) vs. experiment (dashed lines).