# Modeling High Speed Semiconductor Devices of Modern Communication Systems

Vassil Palankovski and Siegfried Selberherr Institute for Microelectronics, TU Vienna Gusshausstrasse 27–29, A-1040 Vienna, Austria

### **ABSTRACT**

We present the state-of-the-art in simulation for industrial heterostructure devices based on SiGe/Si and III-V compound semiconductors. The work addresses critical modeling issues. Results from two-dimensional hydrodynamic analyses of Heterojunction Bipolar Transistors (HBTs) and High Electron Mobility Transistors (HEMTs) with Minimos-NT are presented in good agreement with measured data. The examples are chosen to demonstrate technologically important issues which can be addressed and solved by device simulation.

**Keywords:** Simulation, Simulation Software, Heterojunction Bipolar Transistors, High Electron Mobility Transistors, Semiconductor Device Modeling

#### 1. INTRODUCTION

Communication and information systems are subject to rapid and highly sophisticated changes. In this development semiconductor heterostructure devices, such as Heterojunction Bipolar Transistors (HBTs) and High Electron Mobility Transistors (HEMTs), are among the fastest and most advanced high-frequency devices. They meet well the requirements for low power consumption, mediumintegration, low cost in large quantities, and high-speed operation capabilities in circuits in the very high frequency range (recently beyond 500 GHz [1]) and for data rates higher than 100 Gbit/s for long range communication.

To cope with explosive development costs and strong competition in the semiconductor industry today, Technology Computer-Aided Design (TCAD) methodologies are extensively used in development and production. Several questions during device fabrication, such as performance optimization and process control, can be addressed by simulation. The choice of a given simulation tool or a combination of tools depends to a large extent on the complexity of the particular task, on the desired accuracy of the problem solution, and on the available human, computer, and time resources.

Optimization of geometry, doping, materials, and material composition profiles targets at high power, high breakdown voltage, high speed (high  $f_{\rm T}, f_{\rm max}$ ), low leakage, low noise, and low power consumption. This is a challenging

task that can be significantly supported by device simulation.

The paper discusses critical modeling issues regarding the simulation of advanced SiGe and III-V semiconductor devices and presents particular simulation results of such devices obtained with the same simulation tool, model set, and set of model parameters. We demonstrate by examples from industrial vendors how a well-calibrated tool can address technologically important issues, such as process variation or reliability.

### 2. CRITICAL ISSUES OF MODELING HETEROSTRUCTURE DEVICES

The continously increasing computational power of computer systems allows the use of TCAD tools on a very large scale. Several commercial device simulators, e.g. [2, 3, 4, 5, 6, 7], company-developed simulators, e.g. [8, 9], and University developed simulators, e.g. [10, 11, 12, 13, 14], have been employed for device engineering applications. However, most of them were focused on silicon devices. These simulators differ considerably in dimensionality (one-, /quasi-/two-, or /quasi-/three-dimensional), in choice of carrier transport model (drift-diffusion, energytransport, or Monte Carlo statistical solution of the Boltzmann equation), and in the capability of including electrothermal effects. The drift-diffusion transport model [15] is by now the most popular model used for device simulation. With down-scaling feature sizes, non-local effects become more pronounced and must be accounted for by applying an energy-transport or hydrodynamic transport model [16]. During the last two decades Monte Carlo methods for solving the Boltzmann transport equation have been developed [17, 18] and applied for device simulation [19]-[21]. However, reduction of computational time is still an issue and, therefore, Monte Carlo device simulation is still not feasible for industrial application on daily basis. An approach to preserve accuracy at lower computational cost is to calibrate lower order transport parameters to Monte Carlo simulation data.

In addition, quantum mechanical effects are often neglected or accounted for only by simple models for quantum corrections [22, 23], as solving the Schrödinger or the Wigner equation is extremely expensive in terms of computational resources.

A common drawback is the limited feedback from technological state-of-the-art process development to simulator development. The quality of the physical models can be questioned as the model parameters for SiGe are often simply inherited from parameters for Silicon. Modeling of the properties of AlGaAs, InGaAs, InAlAs was restricted to slight modifications of the GaAs material properties. Additional materials, such as InGaP and other InP-based materials are required for advanced device modeling, together with new material systems, such as the GaN or the GaSb systems, which have entered the III-V world with impressive device results.

We have addressed several critical modeling issues for heterostructure devices in our three-dimensional device simulator Minimos-NT [24], which can deal with different complex structures and materials, such as SiGe and various III-V binary and ternary compounds, with arbitrary material composition profiles in a wide temperature range.

The models are based on experimental or Monte Carlo simulation data and employ analytical functional forms which cover the whole material composition range. The model parameters are checked against several independent HEMT and HBT technologies to obtain a concise set used for all simulations. Reviewing simulation of HBTs and submicron HFETs with gate-lengths down to 100 nm used for mmwave devices, solutions of energy transport equations are necessary to account for non-local effects, such as velocity overshoot. A model for carrier temperature dependent energy relaxation times [25] has been developed as well as a model for lattice temperature dependent saturation velocities [26].

Heterointerface modeling is a key issue for devices which include abrupt junctions. Thermionic emission and field emission effects critically determine the current transport parallel and perpendicular to the heterointerfaces. Another critical issue for recessed HFETs and for III-V HBTs is the description of the semiconductor/insulator interface. Fermi-level pinning prevails especially for typical barrier materials such as AlGaAs or InAlAs, for ledge materials such as InGaP, and insulators such as SiN.

Modeling of strained SiGe is not a trivial task, since special attention has to be focused on the stress-dependent change of the bandgap due to Ge content [27]. This effect must be separated from dopant-dependent bandgap narrowing which for itself depends on the semiconductor material composition, the doping concentration, and the lattice temperature [28].

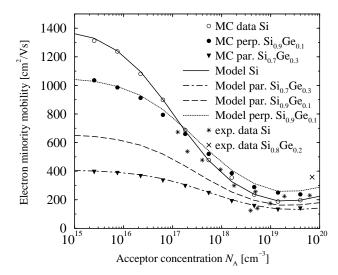

As the minority carrier mobility is of considerable importance for bipolar transistors, an analytical low field mobility model which distinguishes between majority and minority electron mobilities has been developed [28] using Monte Carlo simulation data for electrons in Si and SiGe. Monte Carlo simulation which accounts for alloy scattering and splitting of the anisotropic conduction band valleys due to strain in combination with an accurate ionized impurity scattering model [29] allowed us to obtain results for SiGe for the complete range of donor and acceptor con-

centrations and Ge contents x. The good agreement of the model with the measured and the Monte Carlo simulation data, both for in-plane and perpendicular to the surface directions, is illustrated in Fig. 1.

Figure 1: Minority electron mobility in  $Si_{1-x}Ge_x$  as a function of  $N_A$  and x: The model gives good agreement with measurements and Monte Carlo simulation data both for in-plane and perpendicular to the surface directions.

All the important physical effects, such as bandgap narrowing, anisotropic electron minority mobility in strained SiGe, Shockley-Read-Hall recombination, surface and Auger recombination, and impact ionization are taken into account. III-V materials and SiGe are known to have a reduced heat conductivity in comparison to Silicon [30]. Self-heating effects are accounted for by solving the lattice heat flow equation self-consistently with the energy transport equations. Examples are given in the next section for both HEMT and HBT devices.

Advanced device simulation allows a precise physics-based extraction of small-signal parameters [31, 32]. Measured bias dependent S-parameters serve as a valuable source of information when compared at different bias points to simulated S-parameters from a device simulator, such as Minimos-NT. This procedure reflects the full RF-information contained in the S-parameters and allows process control beyond the comparison of DC-quantities.

## 3. SELECTED RESULTS OF INDUSTRIALLY RELEVANT DEVICES

It is well known that GaAs-HBTs with an InGaP ledge have an improved reliability [33]. Power amplifiers with InGaP/GaAs HBTs are part of many cellular phones today. Two-dimensional device simulation allows the analysis of experimental data in cases which cannot be explained by simple analytical assumptions. This proved to be especially useful for explaining and avoiding device degradation which occurs as a result of electrothermal stress aging.

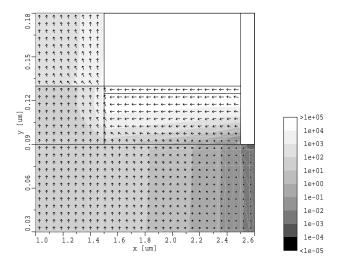

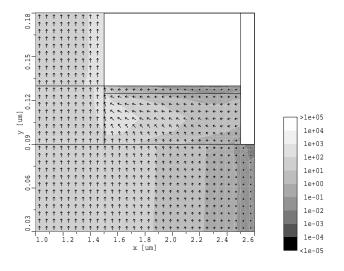

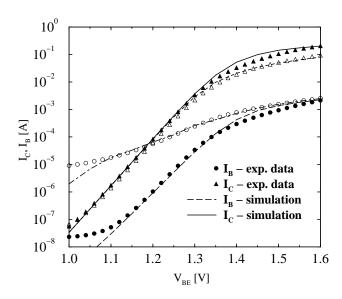

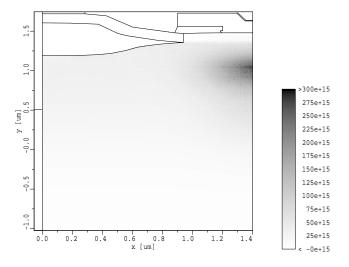

The impact of the ledge thickness and the negative surface charges existing at the ledge/nitride interface, was studied for a one-finger  $3\times30~\mu\text{m}^2$  InGaP/GaAs HBT with respect to reliability [34]. We found a surface charge density of  $\rho_{\text{surf}}=10^{12}~\text{cm}^{-2}$  to be sufficient to get good agreement with the measured Gummel plots at  $V_{\text{CB}}=0~\text{V}$ . Simulation results for the electron current density at  $V_{\text{BE}}=1.2~\text{V}$  without and with a surface charge density of  $10^{12}~\text{cm}^{-2}$ , respectively, are shown in Fig. 2 and Fig. 3. Based on these investigations it is possible to explain the base current degradation (see Fig. 4) of a strongly stressed device by a decrease in the effective negative surface charge density along the interface from  $10^{12}~\text{cm}^{-2}$  to  $4\times10^{11}~\text{cm}^{-2}$  due to compensation mechanisms [35].

Figure 2: Electron current density [A/cm $^2$ ] at  $V_{\rm BE}$  = 1.2 V: Simulation without surface charges.

Figure 3: Electron current density  $[A/cm^2]$  at  $V_{\rm BE} = 1.2$  V: Simulation with a surface charge density of  $10^{12}$  cm<sup>-2</sup>.

For HFET performance the very critical issues are process control and inverse modeling of geometrical structures. Various examples for high-power AlGaAs/InGaAs/GaAs

Figure 4: Comparison of measurements (symbols) and simulations (lines) before (filled) and after (open) HBT aging.

and high-speed InAlAs/InGaAs/InP HEMTs are demonstrated in [36].

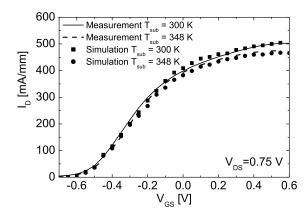

Two factors contribute to the gate currents in pseudomorphic GaAs HEMTs: thermionic field emission (TFE) effects and impact ionization are analyzed in detail in [37, 38]. For high-speed InAlAs/InGaAs HEMTs, the precise evaluation of low voltage or low power capabilities is useful for development of high-speed optical data transmission beyond 40 Gbit/s. The comparison of several lattice matched and metamorphic technologies gave consistent simulation parameters also for this material system [39]. Fig. 5 shows simulation and measurements for two different substrate temperatures for a composite channel In<sub>0.52</sub>Al<sub>0.48</sub>As/  $In_{0.66}Ga_{0.34}As/In_{0.53}Ga_{0.47}As/InP$  HEMT for  $l_q = 150$  nm. High field effects such as impact ionization are considered. This allows the analysis of both, optimized speed and limited gate current, when scaling  $\delta$ -doping and gateto-channel separation for the requirements of 80 Gbit/s operation.

Figure 5: Transfer characteristics of a composite channel InAlAs/InGaAs/InP HEMT with  $l_g=150~\rm nm$  for two different temperatures.

The investigated  $12\times0.4~\mu\text{m}^2$  SiGe HBT device structure is obtained by process simulation with DIOS [5] which reflects real device fabrication as accurately as possible. The implant profiles as well as the annealing steps are calibrated to one-dimensional SIMS profiles. To save computational resources the simulation domain covers only one half of the real device which is symmetric and the collector-sinker is not included in the structure (see Fig. 6).

Figure 6: Simulated device structure and Phosphorus collector implant [cm<sup>-3</sup>].

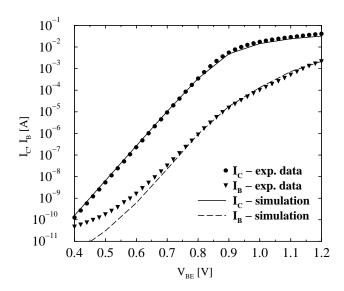

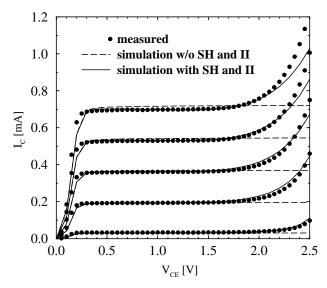

All important physical effects, such as surface recombination, generation due to impact ionization, and self-heating, are properly modeled and accounted for in the simulation in order to get good agreement with measured forward (Fig. 7) and output characteristics (Fig. 8) using a concise set of models and parameters. In contrast, simulation without including self-heating effects cannot reproduce the experimental data, especially at high power levels.

The contribution of doping-dependent bandgap narrowing to the conduction band (here about 80% and 20% for donor and acceptor doping, respectively), the concentration of traps in the Shockley-Read-Hall recombination model, the velocity recombination for holes in the poly-silicon contact model [40] used at the emitter contact, and the substrate thermal resistance are the only fitting parameters used in the simulation.

A closer look at the increasing collector current  $I_{\rm C}$  at high collector-to-emitter voltages  $V_{\rm CE}$  and constant base current  $I_{\rm B}$  stepped by 0.4  $\mu{\rm A}$  from 0.1  $\mu{\rm A}$  to 1.7  $\mu{\rm A}$  reveals the interplay between self-heating and impact ionization. While impact ionization leads to a strong increase of  $I_{\rm C}$ , self-heating decreases it. In fact, both  $I_{\rm C}$  and  $I_{\rm B}$  increase due to self-heating at a given bias condition. As the change is relatively higher for  $I_{\rm B}$ , in order to maintain it at the same level,  $V_{\rm BE}$  and, therefore,  $I_{\rm C}$  decrease.

Since advanced SiGe techniques exhibit competitive performance of high frequency devices in markets that were prior the domain of other materials, small-signal analysis by means of simulation of these devices becomes more

Figure 7: Forward Gummel plots at  $V_{\rm CB}=0$  V: Comparison between measurement data and simulation at room temperature.

Figure 8: Output characteristics: Simulation with and without self-heating (SH) and impact ionization (II) compared to measurement data.  $I_{\rm B}$  is stepped by 0.4  $\mu A$  from 0.1  $\mu A$  to 1.7  $\mu A$ .

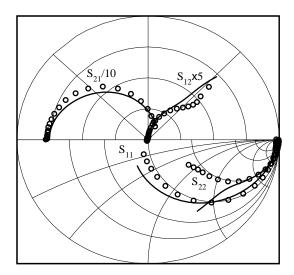

important. Fig. 9 shows a comparison between measured and simulated S-parameters in the frequency range between 50 MHz and 31 GHz at  $V_{\rm CE}$  =1 V and current density  $J_{\rm C}$  = 76 kA/cm<sup>2</sup>.

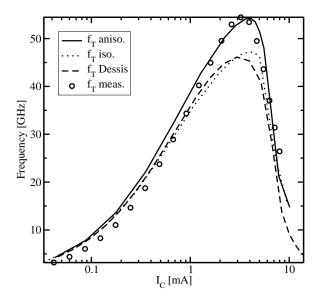

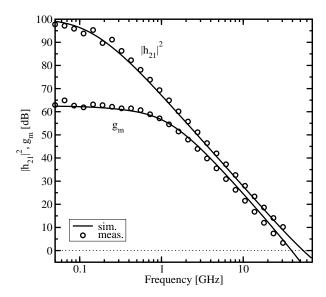

We calculated the matched gain  $g_m$  and the short-circuit current gain  $h_{21}$  in order to extract the figures of merit  $f_T$  (short-circuit cut-off frequency) and  $f_{\rm max}$  (maximum oscillation frequency) found at the unity gain point. Fig. 10 and Fig. 11 show the comparison of our results and the corresponding measurement data. While the measurement data ends at 31 GHz the simulation could be extended to frequencies beyond this intersection. The peak of the  $f_T$ -

Figure 9: S-parameters in a combined Smith chart (radius = 1) from 50 MHz to 31 GHz at  $V_{\rm CE}$  = 1 V and current density  $J_{\rm C}$  = 76 kA/cm<sup>2</sup> (measurements with circles).

curve in Fig. 10 corresponds exactly to the frequency at the respective intersection in Fig. 11. Fig. 10 shows also the effect of an anisotropic electron mobility. In addition, results obtained by a commercial device simulator (DESSIS [5]) using default models and parameters are included for comparison.

### 4. CONCLUSION

A brief overview of the state-of-the-art of simulation tools for heterostructure RF-devices has been given. We have presented experiments and simulations of SiGe and GaAs HBTs. Good agreement was achieved both with experimental DC-results (forward and output characteristics) and with high-frequency data. With an increasing number of stable and reliable heterostructure technologies available, a meaningful comparison between simulation results and statistically analyzed data is possible and delivers on the one hand side model verification, and on the other hand side valuable process information.

### **ACKNOWLEDGMENT**

The work is supported by the Austrian Science Fund (FWF), Project P14483-MAT, by austriamicrosystems AG, Unterpremstätten, Austria, by Infineon Technologies AG, Munich, Germany, and by the Fraunhofer Institute of Applied Solid-State Physics, Freiburg, Germany.

### REFERENCES

[1] Y. Yamashita, A. Endoh, K. Shinohara, K. Hikosaka, T. Matsui, S. Hiyamizu, and T. Mimura, "Pseudomorphic  $In_{0.52}Al_{0.48}As/In_{0.7}Ga_{0.3}As$  HEMTs with an ultrahigh  $f_{\rm T}$  of 562 GHz," in *IEEE Electron Device Lett.*, vol. 23, pp. 573–575, 2002.

Figure 10: Cut-off frequency  $f_{\rm T}$  versus collector current  $I_{\rm C}$  at  $V_{\rm CE}$  = 1 V.

Figure 11: Short-circuit current gain  $h_{21}$  and matched gain  $g_{\rm m}$  vs. frequency at  $V_{\rm CE}=1$  V and current density  $J_{\rm C}=76\,k\text{A/cm}^2$ .

- $[2] \ APSYS, http://www.crosslight.com/downloads/downloads.html \\$

- [3] ATLAS/Blaze, http://www.silvaco.com/products/vwf/atlas/

- [4] BIPOLE3, http://www.bipsim.com/mainframe.html

- [5] DESSIS and DIOS, http://www.ise.com/products/index.html

- [6] G-PISCES-2B, http://www.gateway-modeling.com/products.htm

- [7] MEDICI, http://www.synopsys.com/products/avmrg/device\_sim\_ds.html

- [8] E. Buturla, P. Cottrell, B. Grossman, and K. Salsburg, "Finite-Element Analysis of Semiconductor Devices: The FIELDAY Program," http://www.research.ibm.com/journal/rd/441/buturla.pdf

- [9] NEMO, http://www.cfdrc.com/nemo/

- [10] PISCES-ET, http://www-tcad.stanford.edu/tcad.html

- [11] C. Fischer, P. Habaš, O. Heinreichsberger, H. Kosina, P. Lindorfer, P. Pichler, H. Pötzl, C. Sala, A. Schütz, S. Selberherr, M. Stiftinger, and M. Thurner, *MINIMOS 6 User's Guide*. Institut für Mikroelektronik, Technische Universität Wien, 1994.

- [12] J. Geßner, F. Schwierz, H. Mau, D. Nuernbergk, M. Roßberg, and D. Schipanski, "Simulation of the Frequency Limits of SiGe HBTs," in *Proc. Modeling and Simulation of Microsystems*, Puerto Rico, pp. 407–410, 1999.

- [13] C.G. Morton and C.M. Snowden, "Comparison of Quasi-2D and Ensemble Monte Carlo Simulations for Deep Submicron HEMTs," in *Dig. MTT-S Intl. Microwave Symp.*, Boston, vol. 1, pp. 153–156, 1998.

- [14] D. Richey, J. Cressler, and A. Joseph, "Scaling Issues and Ge Profi le Optimization in Advanced UHV/CVD SiGe HBT's," *IEEE Trans. Electron Devices*, vol. 44, no. 3, pp. 431–440, 1997.

- [15] S. Selberherr, Analysis and Simulation of Semiconductor Devices. Wien, New York: Springer, 1984.

- [16] W. Hänsch, The Drift Diffusion Equation and its Application in MOSFET Modeling. Wien, New York: Springer, 1991.

- [17] C. Jacoboni and P. Lugli, The Monte Carlo Method for Semiconductor Device Simulation. Wien, New York: Springer, 1989.

- [18] K. Hess, ed., Monte Carlo Device Simulation: Full Band and Beyond. Boston, Dordrecht, London: Kluwer, 1991.

- [19] H. Kosina and S. Selberherr, "A Hybrid Device Simulator that Combines Monte Carlo and Drift-Diffusion Analysis," *IEEE Trans. Computer-Aided Design*, vol. 13, no. 2, pp. 201– 210, 1994.

- [20] W. Engl, A. Emunds, B. Meinerzhagen, H. Peifer, and T. Thoma, "Bridging the Gap between the Hydrodynamic and the Monte Carlo Model – An Attempt," in *Proc. VLSI Pro*cess/Device Modeling Workshop, Osaka, pp. 32–33, 1989.

- [21] S. Laux and M. Fischetti, "The DAMOCLES Monte Carlo Device Simulation Program," in *Computational Electronics* (K. Hess, J. Leburton, and U. Ravaioli, eds.), pp. 87–92, Kluwer, 1991.

- [22] W. Hänsch, T. Vogelsang, R. Kircher, and M. Orlowski, "Carrier Transport Near the  $Si/SiO_2$  Interface of a MOSFET," *Solid State Electron.*, vol. 32, no. 10, pp. 839–849, 1989

- [23] K. Dragosits, V. Palankovski, and S. Selberherr, "Two-Dimensional Modeling of Quantum Mechanical Effects in Ultra-Short CMOS Devices," Intl. Conf. on Nanoelectronics and Electromagnetic Compatibility, in N. Mastorakis, V. Kluev, and D. Koruga, eds., Advances in Simulation, Systems Theory and Systems Engineering, pp. 113–116, WSEAS Press, 2002.

- [24] Minimos-NT 2.0 User's Guide, Institut für Mikroelektronik, Technische Universität Wien, Austria, http://www.iue.tuwien.ac.at/software/minimos-nt.

- [25] B. Gonzales, V. Palankovski, H. Kosina, A. Hernandez, and S. Selberherr, "An Energy Relaxation Time Model for Device Simulation," *Solid-State Electron.*, vol. 43, pp. 1791–1795, 1999.

- [26] R. Quay, C. Moglestue, V. Palankovski, and S. Selberherr, "A Temperature Dependent Model for the Saturation Velocity in Semiconductor Materials," *Materials Science in Semicon-ductor Processing*, vol. 3, no. 1-2, pp. 149–155, 2000.

- [27] J. Eberhardt and E. Kasper, "Bandgap Narrowing in Strained SiGe on the Basis of Electrical Measurements on Si/SiGe/Si Hetero Bipolar Transistors," *Materials Science and Engineering*, vol. B89, pp. 93–96, 2002.

- [28] V. Palankovski, G. Kaiblinger-Grujin, and S. Selberherr, "Implications of Dopant-Dependent Low-Field Mobility and Band Gap Narrowing on the Bipolar Device Performance," *J.Phys.IV*, vol. 8, pp. 91–94, 1998.

- [29] H. Kosina and G. Kaiblinger-Grujin, "Ionized-Impurity Scattering of Majority Electrons in Silicon", *Solid State Electron.*, vol. 42, no. 3, pp. 331–338, 1998.

- [30] V. Palankovski and S. Selberherr, "Thermal Models for Semiconductor Device Simulation," in *Proc. European Con*ference on High Temperature Electronics, Berlin, pp. 25–28, 1999.

- [31] R. Quay, R. Reuter, V. Palankovski, and S. Selberherr, "S-Parameter Simulation of RF-HEMTs," in *Proc. High Performance Electron Devices for Microwave and Optoelectronic Applications EDMO*, Manchester, pp. 13–18, 1998.

- [32] S. Wagner, V. Palankovski, T. Grasser, R. Schultheis, and S. Selberherr, "Small-Signal Analysis and Direct S-Parameter Extraction," in *Proc. Intl.Symp. on Electron Devices for Microwave and Optoelectronic Applications EDMO*, Manchester, pp. 50–55, Nov. 2002.

- [33] T. Low, C. Hutchison, P. Canfi eld, T. Shirley, R. Yeats, J. Chang, G. Essilfi e, W. Whiteley, D. D'Avanzo, N. Pan, J. Elliot, and C. Lutz, "Migration from an AlGaAs to an In-GaP Emitter HBT IC Process for Improved Reliability," in *Tech.Dig. GaAs IC Symp.*, Atlanta, pp. 153–157, 1998.

- [34] V. Palankovski, S. Selberherr, R. Quay, and R. Schultheis, "Analysis of HBT Degradation After Electrothermal Stress," in *Proc. Intl.Conf. on Simulation of Semiconductor Processes and Devices*, Seattle, pp. 245–248, 2000.

- [35] N. Bovolon, R. Schultheis, J.-E. Müller, P. Zwicknagl, and E. Zanoni, "A Short-Term High-Current-Density Reliability Investigation of AlGaAs/GaAs Heterojunction Bipolar Transistors," *IEEE Electron Device Lett.*, vol. 19, no. 12, pp. 469–471, 1998.

- [36] R. Quay, Analysis and Simulation of High Electron Mobility Transistors, Dissertation, Technische Universität Wien, July 2001. http://www.iue.tuwien.ac.at/phd/quay

- [37] R. Quay, H. Massler, W. Kellner, T. Grasser, V. Palankovski, and S. Selberherr, "Simulation of Gallium-Arsenide Based High Electron Mobility Transistors," in *Proc. Intl.Conf. on Simulation of Semiconductor Processes and Devices*, Seattle, pp. 74–77, 2000.

- [38] R. Quay, V. Palankovski, M. Chertouk, A. Leuther, and S. Selberherr, "Simulation of InAlAs/InGaAs High Electron Mobility Transistors with a Single Set of Physical Parameters", in *IEDM Tech.Dig.*, San Francisco, pp. 186–189, 2000.

- [39] V. Palankovski, R. Quay, and S. Selberherr, "Industrial Application of Heterostructure Device Simulation," *IEEE J. Solid-State Circuits*, vol. 36, no. 9, pp. 1365–1370, (invited), Sept. 2001.

- [40] Z. Yu, B. Ricco, and R. Dutton, "A Comprehensive Analytical and Numerical Model of Polysilicon Emitter Contacts in Bipolar Transistors," *IEEE Trans. Electron Devices*, vol. 31, no. 6, pp. 773–784, 1984.