# **Optimization of Carbon Nanotube Field Effect Transistors**

E. Ungersboeck<sup>1</sup>, M. Pourfath<sup>1</sup>, A. Gehring<sup>1</sup>, H. Kosina<sup>1</sup>, B.H. Cheong<sup>2</sup>, and S. Selberherr<sup>1</sup>

<sup>1</sup>Institute for Microelectronics, TU Vienna, A-1040 Vienna, AUSTRIA, Ungersboeck@iue.tuwien.ac.at

<sup>2</sup>Computational Science Engineering Center, SAIT, Suwon 440-600, KOREA, Bhcheong@sait.samsung.co.kr

### **ABSTRACT**

The performance of Schottky barrier carbon nanotube field effect transisitors (CNTFETs) depends critically on the device geometry. Asymmetric gate contacts, the drainand source contact thickness, and nonhomogenous dielectrics above and below the nanotube influence the device operation. We use an optimizer with respect to the subthreshold slope, high  $I_{\rm on}/I_{\rm off}$  ratio, and large on-currents and show that the use of a thin needle-like source contact is favorable whereas large drain contacts can decrease the off-current. The best performance improvements can be achieved using asymmetric gates centered above the source contact, where the position and length of the gate contact varies with the oxide thickness, and high-κ materials on top of the CNT and low-κ materials below the tube. We demonstrate that by geometry optimization the subthreshold slope can be reduced by a factor of two reaching a value of 100 mV/dec for devices with oxide thicknesses of 5 nm.

*Keywords:* nanoelectronics, carbon nanotubes, field effect transistors, optimization

#### 1 INTRODUCTION

Semiconductor device technology using nanocarbon materials in semiconductor chip wiring is receiving accelerated development. Metallic nanotubes are a promising material for interconnects and vias in integrated circuits because of their high electrical and thermal conductivity, whereas semiconducting tubes have emerged as possible candidates for nanoscale field effect transistors (CNT-FETs).

Surprising effects regarding to the scaling of the performance of CNTFETs have been observed recently [1]. It was shown that these unexpected scaling trends can be well understood, assuming that the transistor action is caused by the modulation of Schottky barriers at the metal-nanotube contact. The barriers can be thinned by applying gate voltages sufficiently large to allow tunneling of electrons or holes.

A critical issue for CNTFET performance is the required scaling of the drain voltage  $V_d$  as the gate oxide thickness  $(T_{ox})$  is decreased [2]. The off-current  $(I_{off})$  rises significantly when the absolute value of the drain current is increased leading to a decrease of  $I_{\rm on}/I_{\rm off}$ . This effect can be understood within the Schottky band model, where the subthreshold characteristics of CNTFETs with symmetric geometries, i.e. symmetric gate, source, and drain contacts, is symmetric around the gate voltage  $V_g = V_d/2$ . At this point the barrier for electrons is the same as for holes and the minimum current will flow through the nanotube. The electron current rises with  $V_{\rm g}$ , whereas the hole current rises with  $V_{\rm d} - V_{\rm g}$ . For a large  $V_{\rm d}$  the resulting  $V_{\rm g}$  may be large enough to suppress the Schottky barriers at the nanotube contacts and enable large  $I_{\text{off}}$  currents. This will occur whenever the devices are scaled to smaller size, or high-κ gate oxides increase the electric field at the metal nanotube contacts.

It was shown recently that the use of dielectrics with different  $\kappa$  above and below the nanotube can enhance device performance [1]. Furthermore it was demonstrated that asymmetric geometries, with gate contacts located only in the vicinity of the source contact, can enhance device performance [3]. This is due to the fact that the performance is not linked to the gate capacitance but to the change in electrostatic potential at the source and drain contact.

In this work we use an optimization setup to be able to capture the impact of all the mentioned geometry related effects on the CNTFET performance at once and to extract geometries optimized for a steep subthreshold slope  $S = (\mathrm{dlog_{10}}\,I/\mathrm{d}V_\mathrm{g})^{-1}$ , a high  $I_\mathrm{on}/I_\mathrm{off}$  ratio, and high oncurrents.

# 2 DEVICE OPTIMIZATION

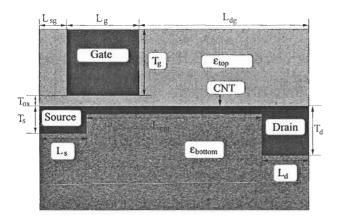

We concentrated on single-gated device geometries, comparable to conventional MOSFETs with the CNT replacing the silicon channel. We optimized the geometry (see inset of Figure 1) with respect to the following six parameters: the position and length of the gate contact (by varying  $L_{\rm dg}$ ,  $L_{\rm sg}$ ), the thickness of source and drain contact ( $T_{\rm s}$ ,  $T_{\rm d}$ ), and the permittivity of the top and bottom dielectric ( $\varepsilon_{\rm top}$ ,  $\varepsilon_{\rm bottom}$ ). We set the length of both source and

Figure 1: Device geometry with simulation parameters.

drain contacts to 10 nm, the length of the CNT to 120 nm. In our calculations the diameter of the nanotube is 1.4 nm with a band gap of 0.6 eV. We focus on mid-gap Schottky barriers, where the Fermi level of the metal contacts fall in the middle of the CNT bandgap.

## 2.1 Transport Modeling

Electrostatic simulations were performed using the Smart-Analysis-Package [4]. This software contains a finite element solver which uses a preconditioned conjugate gradient method to solve large linear systems in order to obtain the distributions of the potential and the electric field in the simulation domain. We neglected the charge on the nanotube which is a good approximation for the off-state and the turn-on regime [1]. The nonuniform triangular grid is refined at the metal-nanotube interface, where the Schottky barriers control the current through the tube. The resulting potential profile along the tube is used for the calculation of the transmission coefficient in a postprocessing step.

To account for coherent transport in the nanotube the Landauer-Büttiker formula was used. The drain current through the nanotube is given by an integration in the energy domain [5]

$$I_{\rm d} = \frac{4q}{h} \int [f_{\rm s}(E) - f_{\rm d}(E)] TC(E) dE, \qquad (1)$$

where  $f_{\rm s,d}$  are equilibrium Fermi functions at the source and drain contacts, and TC(E) is the transmission coefficient. Even if TC(E)=1, the resistance of the tube is given by  $h/(4q^2)\approx 6.5\,{\rm k}\Omega$ , when assuming two conduction channels in the tube. This quantum mechanical resistance stems from the difference of possible conduction channels in the tube and the macroscopic metal contact.

Accounting for an idealized CNT band structure [6] in the vicinity of the Fermi level, the transmission coefficient is estimated within the commonly used Wentzel-Kramers-Brillouin (WKB) approximation.

$$\ln TC(E) = -2 \int \frac{\mathcal{E}_{g}}{\sqrt{3} a \gamma_{0}} \sqrt{1 - \left(\frac{E + qV(x)}{\mathcal{E}_{g}/2}\right)^{2}} dx \quad (2)$$

Here a = 0.246 nm denotes the lattice constant,  $\mathcal{E}_g$  is the band gap energy,  $\gamma_0 = 2.5\,\mathrm{eV}$  is the transfer integral, and V(x) is the electrostatic potential along the CNT.  $\mathcal{E}_g$  is related to the tube radius R via  $\mathcal{E}_g = \sqrt{3}a\gamma_0/3R$  [7]. The integration is performed within the classical turning points.

### 2.2 Simulation Setup

The simulation framework SIESTA provides various optimizers that can be chosen to fit best for the current problems. The optimizer used for this work is a genetic optimizer that relies on the theory of evolutionary computation and genetic algorithms. The population of the n-tuples of free parameters are chosen randomly with respect to a Gaussian normal distribution where a large set of distribution and generation parameters can be configured and tuned for special kinds of problems. Furthermore, the simulation of the population was distributed on a computer cluster to significantly decrease the optimization time.

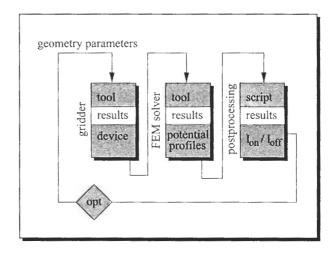

Figure 2: Diagram of the optimization tool flow.

At start time SIESTA provides the initial values of the free geometry parameters ( $T_{\rm s}$ ,  $T_{\rm d}$ ,  $T_{\rm ox}$ ,  $L_{\rm sg}$ ,  $L_{\rm dg}$ ,  $\epsilon_{\rm top}$ , and  $\epsilon_{\rm bottom}$ ) as shown in Figure 2. These values are passed to the electrostatic solver, which calculates the potential profile for a device in the on-state and in the off-state. Afterwards a script is called, which extracts the potential along the nanotube for the two regimes and calculates  $I_{\rm on}$  and  $I_{\rm off}$ . The  $I_{\rm on}/I_{\rm off}$  ratio is submitted to the optimizer which generates corresponding to the last value the next n-tuple of free parameters to improve the  $I_{\rm on}/I_{\rm off}$  ratio that will be evaluated after the next simulation run with the currently extracted values.

### 3 RESULTS

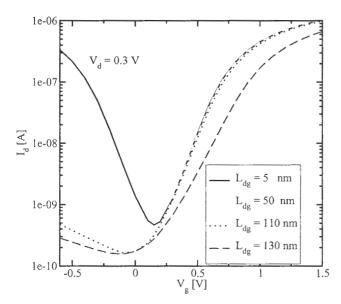

Using asymmetric structures with the gate contact located in the vicinity of the source contact, we find a clear improvement of  $I_{\rm on}/I_{\rm off}$  compared to symmetric geometries (see Figure 3). It can be seen that  $I_{\rm on}$  and the subthreshold slope are hardly influenced by this geometry modification. However, if the overall gate length is reduced too much, the device can no longer be turned on by the gate, leading to a strong reduction of  $I_{\rm on}$  and the subthreshold slope.

The performance enhancement when using different  $\kappa$  materials above and below the carbon nanotube can be explained from the refraction law for electric field lines at interfaces of materials with different permittivities:

$$\frac{\tan \alpha_{\text{top}}}{\varepsilon_{\text{ton}}} = \frac{\tan \alpha_{\text{bottom}}}{\varepsilon_{\text{bottom}}},$$

(3)

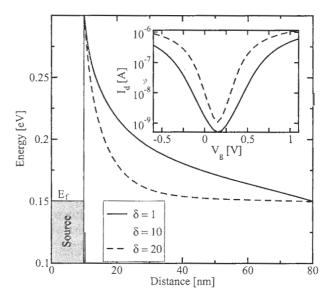

where  $\alpha_{top}$  and  $\alpha_{bottom}$  are the angles between the field lines and normal to the interface in the top and bottom dielectric. This law is valid within our approximation neglecting the charge on the tube and results in a lowering of the barrier when using materials with different permittivity above and below the tube. The effect is more pronounced for thick gate oxides and becomes stronger as the ratio  $\delta = \epsilon_{top}/\epsilon_{bottom}$  is increased (see Figure 4). From the inset of Figure 4 it can be seen that the reduction of the barrier results in higher drain currents. However, for symmetric gate geometries this approach results in high  $I_{off}$  currents at large  $V_d$  and requires a proper scaling of  $V_d$ .

Figure 3: Subthreshold characteristics for different gate contact geometries. The solid line shows the drain current  $I_d$  for a symmetric geometry with  $L_{dg} = L_{sg} = 5 \, \text{nm}$ , whereas the other lines correspond to geometries with an increased distance between the gate and the drain contact.

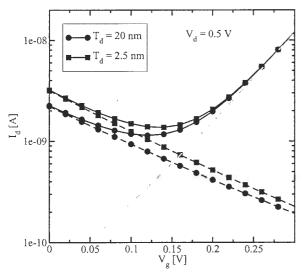

We demonstrated that asymmetric geometries and non-homogenous dielectrics can improve device characteristics. Next we focus on the impact of the source and drain thickness. To achieve low  $I_{\rm off}$  it is necessary to have large barriers for both electrons and holes at the source and drain contact in the off-state. The barriers can be reduced using thin needle-like contacts which result in a high electric field at the contact. Thus large drain contacts have higher energy barrier for holes than small contacts. In Figure 5 it can be seen how the hole current is reduced for a device with  $I_{\rm off} = 20\,{\rm nm}$  as compared to a device with a needle like drain contact, whereas the electron current remains unchanged. In the same manner as  $I_{\rm off}$  can be pushed to lower values by increasing the drain thickness,  $I_{\rm on}$  can be increased using a thinner source contact.

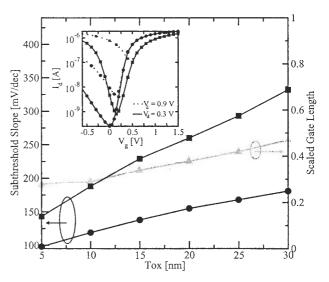

Finally we present the results of our device optimization for different gate oxide thicknesses ( $T_{\rm ox}$ ). In our optimization setup we fixed  $T_{\rm ox}$  and varied the other geometry parameters in order to find optimized structures for a given  $T_{\rm ox}$ . We found that devices with nonhomogenous dielectrics, thin source contacts, and thick drain contacts yield the best subthreshold slope (see Figure 6). The length of the gate contact leading to the optimum device performance depends on  $T_{\rm ox}$ . It steadily decreases when reducing the gate oxide thickness. It can be seen that the subthreshold slope of the optimized geometry scales approximately as  $T_{\rm ox}$ . For comparison in Figure 6 also the subthreshold slope of a symmetric CNTFET ( $L_{\rm dg} = L_{\rm sg} = 5\,{\rm nm},\ T_{\rm s} = T_{\rm d} = 10\,{\rm nm},$

Figure 4: Conduction band edge near the source contact for a device with  $T_{\rm ox}=10\,{\rm nm}$ , plotted for three different ratios  $\delta=\epsilon_{\rm top}/\epsilon_{\rm bottom}$ . For higher  $\delta$  the energy barrier is thinned. The inset shows the impact of nonhomogenous dielectrics on the subthreshold characteristics at  $V_{\rm d}$ =0.3 V.

Figure 5: Drain current as a function of  $V_{\rm g}$  for a drain thickness  $T_{\rm d}$  of 20 nm (circles) and 2.5 nm (squares). Solid lines are used for the total current and dashed lines for the hole current which is reduced in the case of large  $T_{\rm d}$  (circles). The electron current (dash-dotted line) is the same for both cases.

$\varepsilon_{\rm top} = \varepsilon_{\rm bottom} = 3.9$ ) is given. Beside the improvement of the subthreshold slope for asymmetric CNTFETs, the  $I_{\rm on}/I_{\rm off}$  ratio stays above  $10^4$  independently of the gate oxide thickness, whereas  $I_{\rm off}$  rises for symmetric CNTFETs when decreasing  $T_{\rm ox}$ . This also holds for large  $V_{\rm d}$  above 0.7 V. In the inset of Figure 6 the simulated transfer characteristics for the symmetric and asymmetric structure are plotted for  $V_{\rm d}=0.3\,{\rm V}$  and 0.9 V. It can be observed that large drain voltages merely increase  $I_{\rm off}$  while  $I_{\rm on}$  remains almost unchanged. Hence CNTFETs should not be operated at high drain voltages.

### 4 CONCLUSION

The subthreshold slope can be significantly improved by optimizing a simple CNTFET structure using nonhomogenous dielectrics above and below the tube, thin source and wide drain contacts, and an asymmetric gate contact located near the source contact. A subthreshold slope below 100 mV/dec was found for optimized geometries with  $T_{\rm ox}=5$  nm, which is significantly closer to the thermal limit of about  $k_{\rm B}T\ln 10\sim 60\,{\rm mV/dec}$  at room temperature than previously reported values for conventional geometries [2].

In contrast to symmetric devices these structures retain a high  $I_{\rm on}/I_{\rm off}$  ratio above  $10^4$  regardless of the gate oxide thickness, whereas the  $I_{\rm on}/I_{\rm off}$  ratio steadily decreases with  $T_{\rm ox}$  for symmetric devices.

Figure 6: Subthreshold slope for optimized (circles) and conventional (squares) geometries for  $V_{\rm d}=0.3\,\rm V$ . The gate length leading to the optimized structures was scaled to the overall device length(triangles). The inset shows the subtreshold characteristics of a symmetric (squares) and an optimized (circles) structure at two values of  $V_{\rm d}$ .

#### REFERENCES

- [1] S. Heinze, M. Radosavljevic, J. Tersoff, and P. Avouris, "Unexpected Scaling of the Performance of Carbon Nanotube Transistors," *Physical Review B*, vol. 68, p. 235418, 2003.

- [2] M. Radosavljevic, S. Heinze, J. Tersoff, and P. Avouris, "Drain Voltage Scaling in Carbon Nanotube Transistors," *Appl. Phys. Lett.*, vol. 83, no. 12, pp. 2435–2437, 2003.

- [3] S. Heinze, J. Tersoff, and P. Avouris, "Electrostatic Engineering of Nanotube Transistors for Improved Performance," *Appl.Phys.Lett.*, vol. 83, no. 24, pp. 5038–5040, 2003.

- [4] R. Sabelka, "A Finite Element Simulator for Three-Dimensional Analysis of Interconnect Structures," *Microelectronics Journal*, vol. 32, no. 2, pp. 163–171, 2001.

- [5] S. Datta, *Electronic Transport in Mesoscopic Systems*. Cambridge University Press, 1995.

- [6] E. Ungersboeck, A. Gehring, H. Kosina, S. Selberherr, B.-H. Cheong, and W. B. Choi, "Simulation of Carrier Transport in Carbon Nanotube Field Effect Transistors," *Proceedings ESSDERC 2003*, pp. 411–414, 2003.

- [7] T. Nakanishi, A. Bachtold, and C. Dekker, "Transport Through the Interface between a Semiconducting Carbon Nanotube and a Metal Electrode," *Physical Review B*, vol. 66, p. 073307, 2002.