## MICROELECTRONICS RELIABILITY

Microelectronics Reliability 44 (2004) 889-897

www.elsevier.com/locate/microrel

# Introductory Invited Paper

# Rigorous modeling of high-speed semiconductor devices

Vassil Palankovski, Siegfried Selberherr \*

Institute for Microelectronics, TU Wien, Gusshausstrasse 27–29, A-1040 Vienna, Austria

Received 13 February 2004

Available online 15 April 2004

#### Abstract

We present a review of industrial heterostructure devices based on SiGe/Si and III–V compound semiconductors analyzed by means of numerical simulation. A comparison of device simulators and current transport models is given and critical modeling issues are addressed. Results from two-dimensional hydrodynamic analyses of heterojunction bipolar transistors (HBTs) are presented in good agreement with measured data. The examples are chosen to demonstrate technologically relevant issues which can be addressed by device simulation.

© 2004 Elsevier Ltd. All rights reserved.

#### 1. Introduction

Communication and information systems are subject to rapid development regarding, in particular, speed. Semiconductor heterostructure devices, such as heterojunction bipolar transistors (HBTs) and high electron mobility transistors (HEMTs), are among the fastest and most advanced high-frequency devices [1]. They meet well the requirements for low power consumption, medium-scale integration, low cost in large quantities, and high-speed operation capabilities in circuits in the very high frequency range (recently beyond 500 GHz [2]) and for data rates higher than 100 Gbit/s for long range communication.

To cope with explosive development costs and strong competition in the semiconductor industry, technology computer-aided design (TCAD) methodologies are extensively used in development and production. Several highly relevant topics, such as performance optimization and process control, can be addressed by simulation. The choice of a given simulation tool or a combination of tools depends to a large extent on the complexity of the particular task, on the desired accuracy of the

problem solution, and on the available human, computer, and time resources.

Optimization of geometry, doping, materials, and material composition profiles targets at high power, high breakdown voltage, high speed (high  $f_{\rm T}$ ,  $f_{\rm max}$ ), low leakage, low noise, and low power consumption. This is a challenging task that can be significantly supported by device simulation.

The paper gives a short review of state-of-the-art device simulators, discusses critical modeling issues regarding the simulation of advanced SiGe and III–V semiconductor devices, and concludes with particular simulation results of such devices. We demonstrate by examples from industrial vendors how a well-calibrated tool can address technologically important issues.

#### 2. Critical modeling issues for heterostructure devices

There are several problems which are specific for modeling and simulation of heterostructure devices.

A generic device simulator must not only be capable to account for various semiconductor materials but also for different complex geometrical structures and material sequences in multiple dimensions. The physical properties of SiGe and III–V compounds must be modeled for wide ranges of material compositions, temperatures, doping concentrations, etc. The model

E-mail address: selberherr@tuwien.ac.at (S. Selberherr).

<sup>\*</sup>Corresponding author.

parameters have to be verified against several independent HEMT and HBT technologies to obtain one concise set to be used for all simulations [3]. Reviewing simulation of HBTs and submicron HFETs with gatelengths down to 100 nm, solutions of energy transport equations are necessary to account for non-local effects, such as velocity overshoot.

Modeling of strained SiGe is not a trivial task, since special attention has to be focused on the stress-induced change of the bandgap as a function of germanium content [4]. This effect must be separated from doping-induced bandgap narrowing which in turn depends on the semiconductor material composition, the doping concentration, and the lattice temperature [5]. As the minority carrier mobility is of considerable importance for bipolar transistors a distinction between majority and minority electron mobilities is required [1].

Heterointerface modeling is a key issue for devices which include abrupt junctions. Thermionic emission and field emission effects critically determine the current transport parallel and perpendicular to the heterointerfaces [6].

Another critical issue for recessed HFETs and for III–V HBTs is the description of the semiconductor/insulator interfaces, especially with respect to the treatment of the interfaces during the manufacturing process. Fermi-level pinning prevails for typical barrier materials such as AlGaAs or InAlAs and for ledge materials such as InGaP. Active surface states can influence significantly the current gain in bipolar devices [7].

All the important generation/recombination effects, such as Shockley–Read–Hall recombination, surface recombination, direct recombination, Auger recombination, band-to-band tunneling processes, and impact ionization must be taken into account. III–V semiconductors and SiGe are known to have a reduced heat conductivity in comparison with silicon [1]. Self-heating effects must be accounted for by solving the lattice heat flow equation self-consistently with the energy transport equations [8].

Advanced device simulation allows a precise physics-based extraction of small-signal parameters [1]. Measured bias-dependent S-parameters serve as a valuable source of information when compared at different bias points to simulated S-parameters from a device simulator. This procedure reflects the full RF information contained in the S-parameters and allows process control beyond the comparison of DC quantities [9].

A physics-based large-signal extraction is critical due to the typical problems of compact large-signal models. These are: the accurate treatment of parasitic elements, e.g. inductances for multi-finger devices [10]; the thermal problem, which is generically three-dimensional [11]; and frequency dispersion due to fast traps in III–V semiconductors [12].

#### 3. Heterostructure device simulators

The continuously increasing computational power of computer systems allows the use of TCAD tools on a very large scale. Several commercial device simulators (such as APSYS [13], ATLAS [14], BIPOLE3 [15], DESSIS [16], G-PISCES [17], and MEDICI [18]), company-developed simulators (like FIELDAY [19] and NEMO [20]), and university-developed simulators (such as DEVICE [21], FLOODS [22], GALENE [23], MINIMOS-NT [24], NEXT-NANO3 [25], PISCES [26], and PROSA [27]) have been successfully employed for device engineering applications. These simulators differ considerably in dimensionality (one, quasi-two, two, quasi-three, or three), in choice of carrier transport model (drift-diffusion, energytransport, or Monte Carlo (MC) statistical solution of the Boltzmann transport equation), and in the capability of including electrothermal effects. The drift-diffusion transport model [28] is by now the most popular model used for device simulation. With down-scaling of the feature sizes, non-local effects become more pronounced and must be accounted for by applying an energy-transport model or a hydrodynamic transport model [29]. During the last two decades, Monte Carlo methods for solving the Boltzmann transport equation have been developed [30,31] and applied for device simulation [32– 34]. However, reduction of computational time is still an issue, and therefore MC device simulation is still not feasible for industrial application on daily basis. An approach to preserve accuracy at lower computational cost is to calibrate lower order transport parameters to MC simulation data [1].

Quantum mechanical effects gain increased importance with the scaling of the feature size. These effects are often neglected in device simulation or only accounted for by simple analytical models for quantum corrections [35,36], since solving the Schrödinger or the Wigner equation [37] is extremely expensive in terms of computational resources.

Most device simulators focus on silicon devices, and the model parameters for SiGe are often simply inherited from the parameters for silicon. The database available for properties of III-V semiconductors has been limited for a long time due to the large number of materials and material compositions. Moreover, a thorough approach of modeling has been lacking. The quality of the physical models can be questioned, since modeling of the properties of AlGaAs, InGaAs, InAlAs is often restricted to slight modifications of the GaAs material properties. Physical parameters for InGaP and other phosphides are required for advanced device modeling, together with new material systems, such as the GaN or the GaSb systems, which have entered the III-V world with impressive device results. A severe problem is the limited feedback from statistically-based technological process development to device simulator development. Therefore published application examples will also be mentioned here in the course of the discussion.

Critical issues concerning simulation of heterostructures, such as interface modeling at heterojunctions, silicon/poly-silicon interfaces for SiGe devices and insulator surfaces for III–V devices are frequently not considered. The importance of high-energy and high-field effects, such as carrier energy relaxation, impact ionization, and self-heating, is sometimes underestimated.

The two-dimensional device simulator PISCES [26] developed at Stanford University incorporates modeling capabilities for Si, GaAs, and InP-based devices. One of its versions, PISCES-HB, includes harmonic balance for large-signal simulation. It has been applied to LDMOS devices [38] and to MESFETs [39]. Another version, G-PISCES from Gateway Modeling [17], has been extended by a full set of III-V models. Examples of MESFETs, HEMTs, and HBTs for several material systems, e.g. InAlAs/InGaAs, AlGaAs/InGaAs, AlGaAs/GaAs, and InGaP/GaAs, are demonstrated. However, in comparison with the original version of PISCES, this simulator lacks an energy-transport model which is necessary to describe high-field effects. G-PISCES also demonstrated the simulation of AlGaN/GaN HEMTs [40].

The device simulator MEDICI from Synopsys [18], which is also based on PISCES, offers simulation capabilities for SiGe/Si HBTs and AlGaAs/InGaAs GaAs HEMTs. It has been used for the simulation of AlGaAs/GaAs HBTs [41] and for the evaluation of properties of GaN HBTs [42]. Advantages of this simulator are hydrodynamic simulation capabilities and the rigorous approach to generation/recombination processes. In addition, it includes a module which considers anisotropic material properties in SiGe. In a recent version, an interface model including carrier tunneling is included in the III–V simulation module.

The two and three-dimensional device simulator DESSIS from ISE [16] has demonstrated a rigorous approach to semiconductor physics including extensive trap modeling and a variety of mobility models. The capabilities to model Si and SiC are extended by a heterojunction framework to III–V materials [43]. Interface tunneling is included in a thermionic field emission model. The density-gradient method is used to model quantum effects in heterostructure devices [44].

At the quantum level a one-dimensional Schrödinger-Poisson solver, NEMO [20], based on non-equilibrium Green's functions is offered for sub-0.1 µm SiGe structures. POSES [17] from Gateway Modeling is another Schrödinger-Poisson solver proposed for process control by charge analysis in HEMTs. In the program SIMBA a link between a one-dimensional Schrödinger solver and a two-dimensional Poisson solver is demonstrated. SIMBA also provides drift-diffusion transport simulation

of GaN HEMTs [45]. Recently the three-dimensional version of SIMBA has been used for thermal optimization of GaN HEMT layouts [46].

Quasi-two-dimensional approaches using a simplified one-dimensional current equation are demonstrated by several simulators, including BIPOLE3 from BIPSIM [15] which features good models for poly-silicon. A similar approach which couples a full hydrodynamic transport model with a Schrödinger solver has been developed at the University of Leeds [47,48]. This with regard to computation time efficient approach has been verified against MC simulations for devices with gatelengths down to 50 nm [47]. Fast Blaze [14] from Silvaco is a commercial tool based on the code from Leeds. Simulations of S-parameters of AlGaAs/GaAs and pseudomorphic AlGaAs/InGaAs/GaAs HEMTs have been presented.

A software interface between the device model and the compact root large-signal model within the microwave design system (MDS and ADS) has been offered by Agilent. Fast Blaze can be combined with the advanced design system (ADS) and the microwave circuit simulator. An extraction with subsequent multitone excitation calculations has been presented in [49].

The two and three-dimensional simulator ATLAS [14] from Silvaco has also claimed the simulation of AlGaAs/GaAs and AlGaAs/InGaAs/GaAs PHEMTs. Simulations of SiGe HBTs have also been announced, based on the simulator PROSA, developed at the University of Ilmenau [27]. However, the latter lacks heterointerface modeling. Several good optimization results for SiGe HBTs have been achieved with another university-developed simulator, SCORPIO [50].

We tried to address most of the critical modeling issues for heterostructure devices in the three-dimensional device simulator MINIMOS-NT [24], which was used for preparing the following examples.

### 4. Selected results of industrially relevant devices

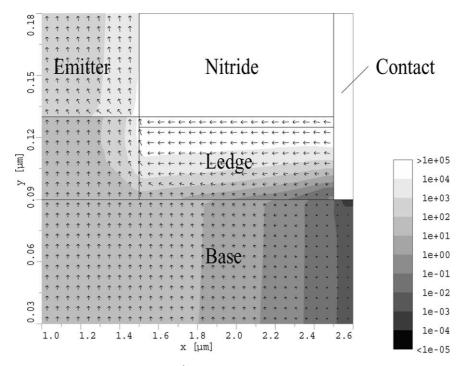

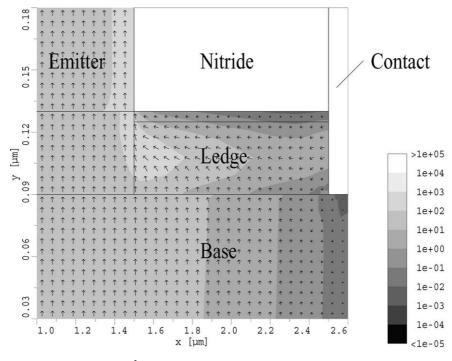

It is well known that GaAs HBTs with an InGaP ledge exhibit an improved reliability [51]. Power amplifiers with InGaP/GaAs HBTs are part of many cellular phones today. Two-dimensional device simulation allows the analysis of experimental data in cases which cannot be explained by simple analytical assumptions. This proved to be especially useful for explaining and avoiding device degradation which occurs as a result of electrothermal stress aging. The impact of the ledge thickness and the negative surface charges existing at the ledge/nitride interface, was studied for a one-finger  $3\times30~\mu m^2$  InGaP/GaAs HBT with respect to reliability [52]. We found a surface charge density of  $\rho_{\rm surf}=10^{12}~{\rm cm}^{-2}$  to be sufficient to get good agreement with the measured Gummel plots at  $V_{\rm CB}=0~{\rm V}$ . Simulation results for the

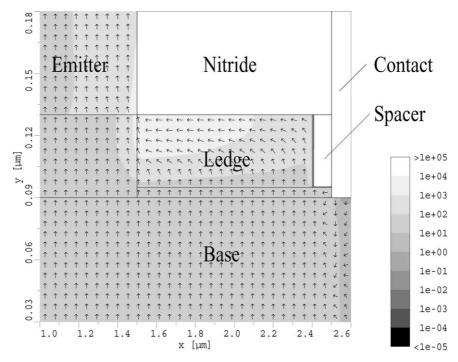

Fig. 1. Electron current density (A/cm<sup>2</sup>) at  $V_{CE} = V_{BE} = 1.2$  V: simulation without surface charges.

Fig. 2. Electron current density (A/cm<sup>2</sup>) at  $V_{\rm CE} = V_{\rm BE} = 1.2$  V: simulation with a surface charge density of  $10^{12}$  cm<sup>-2</sup>.

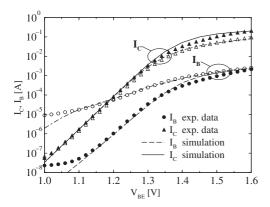

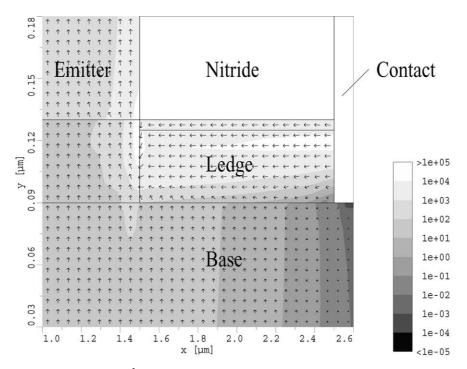

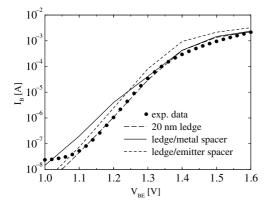

electron current density at  $V_{\rm BE}=1.2~{\rm V}$  without and with a surface charge density of  $10^{12}~{\rm cm}^{-2}$ , respectively, are shown in Figs. 1 and 2. Based on these investigations it is possible to explain the base current degradation (see Fig. 3) of a strongly stressed device by a decrease in the effective negative surface charge density along the interface from  $10^{12}~{\rm cm}^{-2}$  to  $4\times10^{11}~{\rm cm}^{-2}$  due to compensation mechanisms [53]. Fig. 4 shows simulation result for the electron current density at  $V_{\rm BE}=1.2~{\rm V}$ .

Fig. 3. Comparison of measurements (symbols) and simulations (lines) before (filled) and after (open) HBT aging.

Once the possible reason for device degradation is known, it is straightforward to search for solutions. Some ways to avoid degradation were analyzed, assuming the worst case when the negative surface charges at the ledge/nitride interface of a device with 40 nm ledge thickness are completely compensated due to stress. A possible solution is to avoid the electron leakage path in the ledge by means of electrically isolated base contacts, e.g. by introducing a nitride spacer between the ledge and the base metals.

The simulation analysis shows that the depth of such a spacer is of importance. On the one hand, there is the constraint not to exceed the ledge thickness in order to avoid surface recombination in the base. On the other hand, the spacer has to have a sufficient depth to prevent the electron current. Fig. 5 shows the electron current density at  $V_{\rm BE} = V_{\rm CE} = 1.2$  V in a device with a distance of 10 nm between the spacer and the base layer. As can be seen in Fig. 5 a current path still exists under the spacer, if the surface charges are compensated. Unfortunately it is technologically challenging to control the exact spacer depth which has to be about 95% of the ledge thickness in order to solve the reliability problem.

Fig. 6 shows the simulated forward Gummel plots for 40 nm ledge devices with 35 nm deep spacers on the base contact side or on the emitter side of the ledge, respectively. In addition, simulation results for a device with 20 nm ledge thickness are included for comparison in Fig. 6. Measured data for a non-stressed device

Fig. 4. Electron current density (A/cm<sup>2</sup>) at  $V_{\text{CE}} = V_{\text{BE}} = 1.2 \text{ V}$ : simulation with a surface charge density of  $4 \times 10^{11} \text{ cm}^{-2}$ .

Fig. 5. Electron current density (A/cm<sup>2</sup>) at  $V_{\text{CE}} = V_{\text{BE}} = 1.2 \text{ V}$ : simulation with a surface charge density of  $4 \times 10^{11} \text{ cm}^{-2}$  and a spacer between ledge and base contact.

Fig. 6. Base current  $I_B$  in a stressed device using spacer between the ledge and the base contact, between the ledge and the emitter, and device with a thinner ledge. Comparison with measured data for non-stressed device.

Fig. 7. SiGe HBT output characteristics: Simulation with and without self-heating (SH) and impact ionization (II) compared to measurement data.  $I_B$  is stepped by 0.4  $\mu$ A from 0.1 to 1.7  $\mu$ A.

(symbols) is included as a reference. Note that the device with the 20 nm ledge not only has better device characteristics, but is also easier to manufacture.

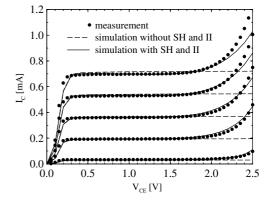

The methodology for characterization and optimization of SiGe HBTs involves process calibration, device calibration employing two-dimensional device simulation, and automated technology computer aided design (TCAD) optimization. The investigated  $0.4 \times 12~\mu m^2$

SiGe HBT structure is obtained by process simulation with DIOS [16], which reflects real device fabrication as accurately as possible.

All important physical effects, such as surface recombination, generation due to impact ionization, and self-heating, are properly modeled and accounted for in the simulation in order to get good agreement with measured forward and output characteristics (Fig. 7)

using a concise set of models and parameters. Simulation neglecting self-heating effects cannot reproduce the experimental data, especially at high power levels.

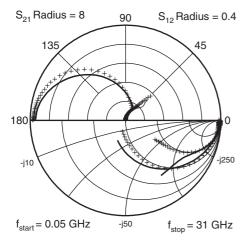

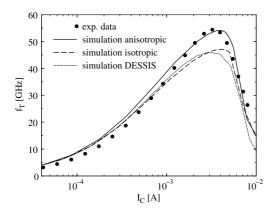

Since advanced SiGe techniques exhibit competitive performance of high frequency devices in markets that were prior the domain of other materials, small-signal analysis by means of simulation of these devices becomes more important. Fig. 8 shows a comparison between measured and simulated S-parameters in the frequency range between 50 MHz and 31 GHz at  $V_{\rm CE}=1$  V and current density  $J_{\rm C}=76$  kA/cm². We calculated the matched gain  $g_{\rm m}$  and the short-circuit current gain  $h_{21}$  in order to extract  $f_{\rm T}$  and  $f_{\rm max}$ . Fig. 9 compares  $f_{\rm T}$  vs.  $I_{\rm C}$  from simulation and measurement. It shows also the effect of an anisotropic electron mobility.

Fig. 8. Simulated (–) and measured (+) S-parameters in a combined Smith-polar chart from 50 MHz to 31 GHz at  $V_{\rm CE}=1~{\rm V}$  and  $J_{\rm C}=76~{\rm kA/cm^2}$ .

Fig. 9. Cut-off frequency  $f_{\rm T}$  versus collector current  $I_{\rm C}$  at  $V_{\rm CE}=1~{\rm V}$ .

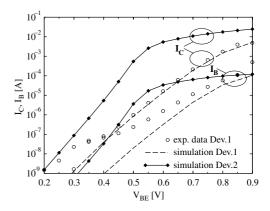

Fig. 10. Forward Gummel plot of a  $1\times8~\mu m^2$  InP/GaAsSb/InP DHBT in comparison to a conventional InP/InGaAs/InGaAsP/InP design.

In addition, results obtained by a commercial device simulator (DESSIS [16]) using default models and parameters are included for comparison.

Using the model for the InP/InGaAs/InGaAsP/InP HBT given in [1], the following study is performed. In this device the In<sub>0.53</sub>Ga<sub>0.47</sub>As base layer is replaced by GaAs<sub>0.49</sub>Sb<sub>0.51</sub> which is also lattice-matched to the InP substrate, and the InGaAsP launcher is removed. Fig. 10 compares the simulated forward Gummel plots of the conventional InP/InGaAs/InGaAsP/InP DHBT (Dev. 1) and the novel InP/GaAsSb/InP DHBT (Dev. 2). Measured data for the conventional device are included as a reference.

#### 5. Conclusion

A brief overview of the state-of-the-art of simulation tools for heterostructure RF-devices has been given. We have presented experiments and simulations of GaAs, SiGe, and InP HBTs. Good agreement was achieved both with experimental DC-results and with high-frequency data. With an increasing number of stable and reliable heterostructure technologies available, a meaningful comparison between simulation results and statistically analyzed data is possible and delivers on the one hand side model verification, and on the other hand side valuable process information.

#### Acknowledgements

The work is supported by austriamicrosystems AG, Unterpremstätten, Austria, by Infineon Technologies AG, Munich, Germany, and by the Fraunhofer Institute of Applied Solid-State Physics, Freiburg, Germany.

#### References

- Palankovski V, Quay R. Analysis and simulation of heterostructure devices. Wien, New York: Springer; 2004.

- [2] Yamashita Y, Endoh A, Shinohara K, Hikosaka K, Matsui, T, Hiyamizu S, et al. Pseudomorphic In<sub>0.52</sub>-Al<sub>0.48</sub>As/In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMTs with an ultrahigh f<sub>T</sub> of 562 GHz. IEEE Electron Dev Lett 2002;23:573–5.

- [3] Quay R., Palankovski V., Chertouk M., Leuther A., Selberherr S. Simulation of InAlAs/InGaAs high electron mobility transistors with a single set of physical parameters. In: IEDM Tech. Dig., San Francisco, 2000. p. 186–9.

- [4] Eberhardt J, Kasper E. Bandgap narrowing in strained SiGe on the basis of electrical measurements on Si/SiGe/ Si hetero bipolar transistors. Mater Sci Eng B 2002;89: 93-6.

- [5] Palankovski V, Kaiblinger-Grujin G, Selberherr S. Implications of dopant-dependent low-field mobility and bandgap narrowing on the bipolar device performance. J Phys IV 1998;8:91–4.

- [6] Quay R, Hess K, Reuter R, Schlechtweg M, Grave T, Palankovski V, et al. Nonlinear electronic transport and device performance of HEMTs. IEEE Trans Electron Dev 2001;48(2):210–7.

- [7] Philippov P, Dimitrov G, Gospodinova M. Studying the influence of the surface on the base current and current gain of bipolar transistor structures. In: Acta Polytechnica Ceske Vysoke Uceni Technicke III, vol. 1. 1987 p. 69– 74.

- [8] Knaipp M. Modellierung von temperatureinflüssen in halbleiterbauelementen. Dissertation. Technische Universität Wien, 998. www.iue.tuwien.ac.at/phd/knaipp.

- [9] Quay R. Analysis and simulation of high electron mobility transistors. Dissertation. Technische Universität Wien, 2001. www.iue.tuwien.ac.at/phd/quay.

- [10] Ma Z, Mohammadi S, Bhattacharya P, Katehi L, Alterovitz SA, Ponchak GE. A high-power and high-gain X-band Si/SiGe/Si heterojunction bipolar transistor. IEEE Trans Microwave Theory Tech 2002;50(4):1101–8.

- [11] d'Alessandro V, Rinaldi N. A critical review of thermal models for electro-thermal simulation. Solid-State Electron 2002;46(4):487–96.

- [12] Filicori F, Vannini G, Santarelli A, Sanchez AM, Tazon A, Newport Y. Empirical modeling of low-frequency dispersive effects due to traps and thermal phenomena in III–V FETs. IEEE Trans Microwave Theory Tech 1995;43(12): 2972–81.

- [13] APSYS, www.crosslight.com/downloads/.

- [14] ATLAS/Blaze, www.silvaco.com/products/vwf/.

- [15] BIPOLE3, www.bipsim.com/mainframe.html.

- [16] DESSIS and DIOS, www.ise.com/products/.

- [17] G-PISCES-2B, www.gateway-modeling.com/.

- [18] MEDICI, www.synopsys.com/products/avmrg/.

- [19] Buturla E, Cottrell P, Grossman B, Salsburg K. Finiteelement analysis of semiconductor devices: the FIELDAY program. IBM J Res Develop 2000;44(1–2):142–56.

- [20] NEMO, www.cfdrc.com/nemo/.

- [21] DEVICE, www.uv.ruhr-uni-bochum.de/.

- [22] FLOODS and FLOOPS, www.tec.ufl.edu/flooxs/.

- [23] Meinerzhagen B, Engl W. The influence of the thermal equilibrium approximation on the accuracy of classical two-dimensional numerical modeling of silicon submicrometer MOS transistors. IEEE Trans Electron Dev 1988;ED-35(5):689–97.

- [24] Binder T, Cervenka J, Dragosits K, Gehring A, Grasser T, Klima R, et al. MINIMOS-NT device and circuit simulator, User's Guide, Release 2.0. Institut für Mikroelektronik, Technische Universität Wien, 2002. www.iue. tuwien.ac.at/software/minimos-nt.

- [25] NEXTNANO3, www.webplexity.de/nextnano3.php.

- [26] PISCES-ET, http://www-tcad.stanford.edu/tcad.html.

- [27] Geßner J, Schwierz F, Mau H, Nuernbergk D, Roßberg M, Schipanski D. Simulation of the frequency limits of SiGe HBTs. In: Proceedings of the International Conference on Modeling and Simulation of Microsystems. San Juan, 1999. p. 407–10.

- [28] Selberherr S. Analysis and simulation of semiconductor devices. Wien, New York: Springer; 1984.

- [29] Hänsch W. The drift diffusion equation and its application in MOSFET modeling. Wien, New York: Springer; 1991.

- [30] Jacoboni C, Lugli P. The Monte Carlo method for semiconductor device simulation. Wien-New York: Springer; 1989.

- [31] Hess K, editor. Monte Carlo device simulation: full band and beyond. Boston, Dordrecht, London: Kluwer; 1991.

- [32] Kosina H, Selberherr S. A hybrid device simulator that combines Monte Carlo and drift-diffusion analysis. IEEE Trans Comput Aided Des 1994;13(2):201–10.

- [33] Engl W, Emunds A, Meinerzhagen B, Peifer H, Thoma T. Bridging the gap between the hydrodynamic and the Monte Carlo Model—an attempt. In: VLSI Process/Device modeling Workshop, Osaka, 1989. p. 32–3.

- [34] Laux S, Fischetti M. The DAMOCLES Monte Carlo device simulation program. In: Hess K, Leburton J, Ravaioli U, editors. Computational electronics. Kluwer; 1991. p. 87–92.

- [35] Hänsch W, Vogelsang T, Kircher R, Orlowski M. Carrier transport near the Si/SiO<sub>2</sub> interface of a MOSFET. Solid-State Electron 1989;32(10):839–49.

- [36] Dragosits K, Palankovski V, Selberherr S. Two-dimensional modeling of quantum mechanical effects in ultrashort CMOS devices. In: Mastorakis N, Kluev V, Koruga D, editors. International Conference on Nanoelectronics and Electromagnetic Compatibility. Skiathos: WSEAS Press; 2002. p. 113–6.

- [37] Nedjalkov M, Kosina H, Selberherr S, Dimov I. A backward Monte Carlo method for simulation of the electron quantum kinetics in semiconductors. VLSI Des 2001;13(1-4):405-11.

- [38] Rotella F, Ma G, Yu Z, Dutton R. Modelling, analysis, and design of RF LDMOS devices using harmonic-balance device simulation. IEEE Trans Microwave Theory Tech 2000;48(6):991–9.

- [39] Sato-Iwanaga J, Fujimoto K, Masato H, Ota Y, Inoue K, Trojyanovsky B, et al. Distortion analysis of GaAs MESFETs based on physical model using PISCES-HB. In: IEDM Tech. Dig. San Francisco, 1996. p. 163–6.

- [40] Anholt R. Simulating AlGaN/GaN HEMTs using G-PISCES-2B and PETs. GaAs Simulation and Analysis News 2000.

- [41] Liou J. Principles and analysis of AlGaAs/GaAs heterojunction bipolar transistors. Boston: Artech House; 1996.

- [42] Pulfrey D, Fathpour S. Performance predictions for N– P–N Al<sub>x</sub>Ga<sub>1-x</sub>N/GaN HBTs. IEEE Trans Electron Dev 2001;48(3):597–602.

- [43] Lyumkis E, Mickevicius R, Penzin O, Polsky B, Sayed K. Numerical analysis of electron tunneling through heterointerfaces and schottky barriers in heterostructure devices. In: GaAs IC Symp. Tech. Dig.. Seattle, 2000. p. 129–132, Updated version.

- [44] Lyumkis E, Mickevicius R, Penzin R, Polsky B, Sayed K, Wettstein A, et al. Simulations of quantum transport in HEMT using density gradient model. In: GaAs IC Symp. Tech. Dig., Monterey, 2002. p. 233–6.

- [45] Stenzel R, Pigorsch C, Klix W, Vescan A, Leier H. Simulation of AlGaN/GaN-HFETs including spontaneous and piezoelectric polarization charges. In: Proceedings of the International Symposium on Compound Semiconductors. Berlin, 1999. p. 511–4.

- [46] Dietrich R, Wieszt A, Vescan A, Leier H, Stenzel R, Klix W. Power handling limits and degradation of large area AlGaN/GaN RF-HEMTs. Solid-State Electron 2003; 47(1):123–5.

- [47] Morton C, Snowden C. Comparison of quasi-2D and ensemble Monte Carlo simulations for deep submicron HEMTs. In: IEEE Int. Microwave Symp. Dig., Boston, 1998. p. 153–6.

- [48] Morton C, Snowden C, Howes M. HEMT physical model for MMIC CAD. In: Proceedings of European Microwave Conference, Bologna, 1995. p. 199–204.

- [49] Johnson R, Kachwalla Z, Snowden C. Multi-tone microwave simulation of HEMTs using a physics-based electro-thermal CAD model. In: Proceedings European Microwave Conference, Munich, 1999. p. 107–10.

- [50] Richey D, Cressler J, Joseph A. Scaling issues and Ge profile optimization in advanced UHV/CVD SiGe HBTs. IEEE Trans Electron Dev 1997;44(3):431–40.

- [51] Low T, Hutchison C, Canfield P, Shirley P, Yeats R, Chang J, et al. Migration from an AlGaAs to an InGaP emitter HBT IC process for improved reliability. In: Tech. Dig. GaAs IC Symp., Atlanta, 1998. p. 153–7.

- [52] Palankovski V, Selberherr S, Quay R, Schultheis R. Analysis of HBT degradation after electrothermal stress. In: Proceedings of the International Conference on Simulation of Semiconductor Processes and Devices, Seattle, 2000. p. 245–8.

- [53] Bovolon N, Schultheis R, Müller J-E, Zwicknagl P, Zanoni E. A short-term high-current-density reliability investigation of AlGaAs/GaAs heterojunction bipolar transistors. IEEE Electron Dev Lett 1998;19(12):469–71.