# MICROELECTRONICS RELIABILITY

Microelectronics Reliability 44 (2004) 1473-1478

www.elsevier.com/locate/microrel

# Enhancement of breakdown voltage for Ni-SiC Schottky diodes utilizing field plate edge termination

T. Ayalew\*†, A. Gehring°, T. Grasser†, and S. Selberherr°

<sup>†</sup>Christian-Doppler-Laboratory for TCAD in Microelectronics at the Institute for Microelectronics °Institute for Microelectronics, TU Vienna, Gußhausstraße 27–29, A-1040 Wien, Austria

## **Abstract**

In this work the improvement in breakdown voltage of Ni-SiC Schottky diodes utilizing field plate edge termination is presented. We have performed numerical investigations on how the addition of the field plate affects the relationship between the device structure, performance, and reliability. The key parameters that alter the overall device performance have been optimized using the device simulator MINIMOS-NT. This structure with a high barrier height metal such as Ni results in Schottky diodes with breakdown voltages in excess of 35% compared to the Schottky diodes without edge termination. The ratio of the maximum field under the anode corner to the field under the center of the contact at the same depth is reduced by a factor of two for edge terminated diodes for a wide range of doping levels. The leakage current in reverse biased operation is lowered by two orders of magnitude at room temperature and nearly by an order of magnitude at 500 K.

© 2004 Elsevier Ltd. All rights reserved.

# 1. Introduction

SiC has been projected to have tremendous potential for high voltage solid state power devices with very high voltage and current ratings because of its high electric breakdown field of  $1.5-4\times10^6$  V/cm and high thermal conductivity of 2.5-5 W/cm K, depending on the doping level [1]. The high breakdown field allows the use of much higher doping and thinner layers for a given voltage than required in Si devices, resulting in specific onresistances for SiC unipolar devices that can be  $1/300^{th}$  that of the equivalent Si devices.

Schottky barrier diodes (SBDs) are attractive, because they provide rectification without significant switching loss. Although SBDs are desirable because of their low switching loss, it is not feasible to build high voltage SBDs in silicon. The main reason in addition to an extremely large specific on-resistance is the relatively low barrier height between common metals and

E-mail address: Ayalew@iue.tuwien.ac.at (T. Ayalew).

silicon. However, with SiC due to its wide bandgap energy, it is easy to fabricate SBDs with barrier heights as high as 1.5 eV [2].

For high-voltage Schottky diodes it is necessary to have an edge termination around the periphery of the diodes to reduce the electric field crowding at the diode edges. Several techniques have been shown to reduce the field crowding at the edges, thus resulting in higher breakdown voltages. These include:

- i. a resistive termination extension (RTE) [3];

- ii. a junction termination extension (JTE) by implantation at the periphery of the diode to form an amorphous area around the periphery of the device [4,5]; and

- iii. a p-n junction guard-ring termination by a local oxide process (LOCOS) [6].

In most of these structures the SiC surface is unpassivated and there is no dielectric isolation between devices on the chip. In this work we used a simple metal

<sup>\*</sup>Corresponding author. Tel.: +43-1-58801/36025; fax: +43-1-58801/36099

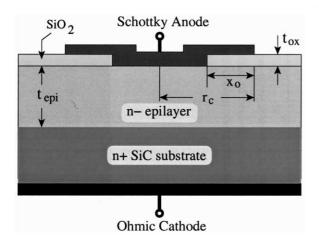

Figure 1. Schematics of the cross section of a field plate terminated Ni-SiC Schottky barrier diode.

field plate structure as shown Fig. 1, in which the Schottky contact overlaps a thermally grown  $SiO_2$  layer so that the maximum electric field at any applied bias is at the  $SiO_2$ -metal interface. In addition, the oxide layer grown serves two other purposes: a) surface passivation; and b) removal of surface defects from the SiC layer which upon oxidation is etched off from the areas where the Schottky contact is to be formed.

We have performed numerical investigations using the general-purpose device simulator MINIMOS-NT [7] on how the addition of the field plate affects the relationship between the device structure, performance, and reliability. The key parameters that alter the overall device performance have been optimized. This structure with a high barrier height metal such as Ni results in Schottky diodes with breakdown voltages in excess of 35% compared to the Schottky diodes without edge termination. The ratio of the maximum field under the anode corner to the field under the center of the contact at the same depth is reduced to 50%. The leakage current is minimized by two orders of magnitude at room temperature and nearly by an order at 500 K.

# 2. Device Structure

Schottky barrier diodes (SBDs) in SiC are often made of an n-type material because of the higher electron mobility [8], and 4H-SiC is preferred because its electron mobility is about twice that of 6H-SiC. The cross section of a field plate edge terminated SBD in SiC shown in Fig. 1 consists of an n-type SiC epitaxial layer with a doping concentration of  $2\times10^{16}~\rm cm^{-3}$  grown over an n+ SiC substrate. The method of edge termination of the SBD has been found to be of importance for obtaining acceptable reverse blocking characteristics.

The barrier height of the metal-Schottky contact plays a critical role in the leakage current and the onstate voltage drop of the Schottky diodes. Selection of the metal to be used for the Schottky contact is thus based on the power loss of the diode which depends on the temperature at which the diode is to be operated. In forward bias, since the on-resistance of SiC Schottky diodes is low, the dominant component of the voltage drop occurs across the metal-SiC Schottky barrier.

Thus diodes utilizing metals with a larger Schottky barrier to SiC experience a larger on-state voltage drop. However, for high-temperature operation of SiC power rectifiers, such metals are still preferable because they also result in lower leakage currents [9]. Thus, the overall on/off ratio of the Schottky diode is higher if we use metals that form a larger Schottky barrier. To determine the optimum barrier height of the Schottky contact, the static power-loss analysis can be performed for rectifiers operating at a 50% duty cycle. Under these conditions, the maximum sum of static power loss dissipated during the on-state and the off-state per unit area is given by (1)

$$P_{\rm loss} = \frac{1}{2} \left( J_{\rm F} V_{\rm F} + J_{\rm R} V_{\rm R} \right), \tag{1}$$

where  $J_{\rm F}$  and  $J_{\rm R}$  are the forward and reverse current densities, while  $V_{\rm F}$  and  $V_{\rm R}$  are the forward and reverse voltages, respectively. The calculated power losses for 1.2 kV SiC Schottky diodes as a function of metal barrier height and temperature show [10] that it is more efficient to use metals that form large barrier heights ( $\geq 1.5\,{\rm eV}$ ) if operation of diodes at higher temperatures is desired. Several reports (see Table 2) have shown that Ni results in suitably large barrier heights  $(1.5-1.7\,{\rm eV})$  to SiC. Thus, we have utilized this metal to study high-voltage Schottky rectifiers on 4H-SiC for high-temperature applications.

The epitaxial layer thickness  $t_{\rm epi}$ , oxide thickness  $t_{\rm ox}$ , and the lateral metal overlap  $x_{\rm o}$  were varied to study their effects on the electric field, the breakdown voltage, and the leakage current. In particular,  $t_{\rm epi}$  was varied to ensure that there is no punch-through up to the breakdown voltage. The optimum value of  $x_{\rm o}$  by which

Table 1 Optimized device parameters for a field plate edge terminated Ni/4H-SiC SBD.

| parameter                                  | value                                |  |  |

|--------------------------------------------|--------------------------------------|--|--|

| epilayer thickness $t_{ m epi}$            | 11 μm                                |  |  |

| epilayer doping $N_{\mathrm{D}}$           | $2 \times 10^{16}  \mathrm{cm}^{-3}$ |  |  |

| oxide thickness $t_{\rm ox}$               | 50 nm                                |  |  |

| lateral metal overlap $x_{\rm o}$          | $11\mu\mathrm{m}$                    |  |  |

| contact radius $r_{\rm c}$ 22 $\mu{\rm m}$ |                                      |  |  |

the breakdown voltage should not be affected by electric field crowding is found to be approximately equal to the thickness of the SiC epilayer  $t_{\rm epi}$ . The symbol  $r_{\rm c}$  denotes the radius of the metal contact. Optimized device parameters for a field plate edge terminated Ni/4H-SiC SBD are listed in Table 1.

# 3. Schottky Contact Formation and Modeling

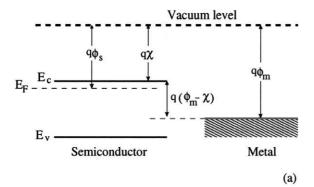

A Schottky barrier refers to a metal-semiconductor contact having a large barrier height (i.e.  $\phi_{\rm B} > {\rm k_B}T_{\rm L}$ ) and a low doping concentration that is less than the density of states in the conduction or valence band. The potential barrier between the metal and the semiconductor can be identified on an energy band diagram. To construct such a diagram we first consider the energy band diagram of the metal and the semiconductor, and align them using the same vacuum level as shown in Fig. 2 (a). As the metal and semiconductor are brought together, the Fermi energies of the two materials must be equal at thermal equilibrium Fig. 2 (b).

The barrier height  $\phi_B$  is defined as the potential difference between the Fermi energy of the metal and the band edge where the majority carriers reside.

Figure 2. Energy band diagram of a metal adjacent to an n-type semiconductor under thermal nonequilibrium condition (a), metal-semiconductor contact in thermal equilibrium (b).

From Fig. 2 one finds that for n-type semiconductors the barrier height is obtained from

$$\phi_{\rm Bn} = \phi_{\rm m} - \chi,\tag{2}$$

where  $\phi_m$  is the work function of the metal and  $\chi$  is the electron affinity of the semiconductor.

A metal-semiconductor junction will therefore form a barrier for electrons if the Fermi energy of the metal is located between the conduction and the valence band edge.

In addition, we define the work function difference as the difference between the work function of the metal and that of the semiconductor. For n-type material it reads

$$\phi_{\rm wf} = \phi_{\rm m} - \chi - \frac{E_{\rm c} - E_{\rm F,n}}{q},$$

(3)

The work function difference energy becomes

$$E_{\mathbf{w}} = \mathbf{q}\phi_{\mathbf{wf}}.\tag{4}$$

The work function measured in vacuum and the barrier height for selected metal/4H-SiC junctions are listed in Table 2 [11–13]. These experimental barrier heights depend on the surface polarity of SiC (Si- and C-face), and often differ from the ones calculated using (2). This is due to the detailed behavior of the metal-semiconductor interface [13, 14]. The ideal metal-semiconductor theory assumes that both materials are pure and that there is no interaction between the two materials nor any interfacial layer [15]. Chemical reactions between the metal and the semiconductor alter the barrier height as do interface states at the surface of the semiconductor and interfacial layers. Furthermore, one finds the barrier heights reported in the literature to vary widely due to different surface cleaning procedures [11, 16].

The current density is calculated according to the thermionic emission condition [17] neglecting tunneling currents:

$$\mathbf{J}_n = -q v_n (n - n_{\rm s}),\tag{5}$$

where n and  $n_s$  are the electron carrier concentrations at quasi-equilibrium and at the surface, respectively.

Table 2 Work function of selected metals and their measured and calculated barrier height on n-type 4H-SiC.

|                             | Al   | Ti   | Ni   | Au   | Pt   |

|-----------------------------|------|------|------|------|------|

| $\phi_{ m m}$               | 4.28 | 4.33 | 5.10 | 5.15 | 5.65 |

| $\phi_{\rm B}$ : Si-face    | =    | 1.12 | 1.69 | 1.81 | -    |

| $\phi_{\rm B}$ : C-face     | =    | 1.25 | 1.87 | 2.07 | -    |

| $\phi_{\rm B}$ : calculated | 1.01 | 1.06 | 1.63 | 1.68 | 2.08 |

The thermionic recombination velocity  $v_n$  for electrons is given by [17]

$$v_n = \sqrt{\frac{k_B T_L}{2\pi m_n}} = \frac{4\pi m_n (k_B T_L)^2}{N_c h^3}.$$

(6)

Equation (6) is usually represented by the expression

$$v_n = A^* \frac{T_{\rm L}^2}{qN_{\rm c}},\tag{7}$$

where

$$A^* = \frac{4\pi q m_n k_B^2}{h^3}$$

(8)

is known as the effective *Richardson constant*. It depends on the electron effective mass and has a theoretical value of 146 and 72 Acm<sup>-2</sup>K<sup>-2</sup> for n-type 4H- and 6H-SiC, respectively [11].

The electron carrier concentration at quasiequilibrium is given by

$$n = N_{\rm c} \exp\left(-\frac{\phi_{\rm Bn}}{k_{\rm B}T_{\rm L}}\right),\tag{9}$$

and at the surface

$$n_{\rm s} = N_{\rm c} \exp\left(\frac{-E_{\rm c} - E_{\rm w}}{k_{\rm B}T_{\rm L}}\right). \tag{10}$$

Note that (5) is equivalent to the most commonly used expression [17]

$$J_{n} = A^{*}T_{L}^{2} \exp\left(\frac{q\phi_{m} - E_{c}}{k_{B}T_{L}}\right)$$

$$\times \left[\exp\left(\frac{q\phi_{Bn} - q\phi_{m}}{k_{B}T_{L}}\right) - 1\right]. \quad (11)$$

To make the numerical investigation more realistic, a model that takes the effect of an oxide/SiC interface charge density on the reverse voltage operation into account has been incorporated [18].

# 4. Simulation Results and Discussion

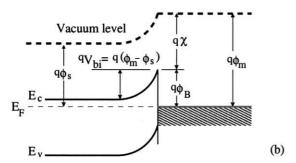

From numerous simulation results on diodes with different epilayer doping concentration, Fig. 3 shows the on-state characteristics of the Ni/4H-SiC SBD at different temperatures for an epilayer thickness of 11  $\mu$ m with a doping concentration of  $2\times 10^{16}~{\rm cm}^{-3}$ .

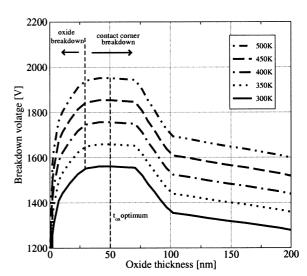

The optimum value of the oxide thickness  $t_{\rm ox}$  is predicted to be  $\sim 50\,\mathrm{nm}$  as depicted in Fig. 4. For extremely thick oxide layers, the field plate is so far away from the semiconductor that it does not have much influence on the electric field distribution. In this case, there is also not much improvement in breakdown voltage.

Figure 3. Forward biased characteristics of Ni/4H-SiC schottky barrier diode.

Hence, the optimum thickness of the field plate oxide is that which will be sufficiently thick that the peak electric field inside the oxide will not exceed the breakdown strength of the oxide; and will be sufficiently thin that the field plate can influence the electric field distribution inside the semiconductor and provide sufficient field relief at the corner. Fig. 4 also illustrates the influence of  $t_{\rm ox}$  on the breakdown voltage caused by the presence of the peak electric field either in the oxide or inside the semiconductor under the corner.

Simulation results show that the optimum field plate

Figure 4. Relation between breakdown voltage and oxide thickness for an epilayer thickness of  $11 \,\mu m$  with a doping concentration of  $2 \times 10^{16} \, \text{cm}^{-3}$ .

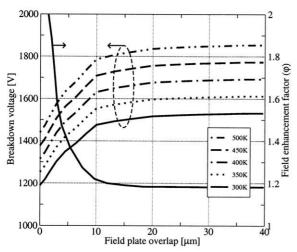

Figure 5. Effect of metal overlap on breakdown voltage and field enhancement factor.

overlap  $x_0$  for achieving the maximum breakdown voltage of a given doping concentration is roughly equivalent to the optimized epilayer thickness (which is determined by the depletion overlap at breakdown). Fig. 5 shows how the breakdown voltage and field enhancement factor  $\varphi$  (the ratio of the maximum field under the anode corner to the field under the center of the contact at the same depth) varies as a function of the metal overlap. It is clear that increasing the field plate overlap up to a certain limit will raise the breakdown voltage. Beyond that limit the breakdown voltage becomes almost independent of this overlap. The value of  $\varphi$  decreases

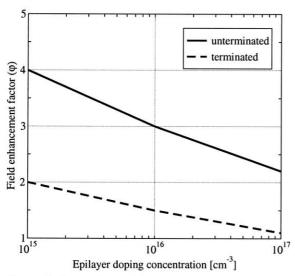

Figure 6. Comparison of field enhancement factor as a function of epilayer doping concentration at a depth of  $1 \mu m$  under the anode.

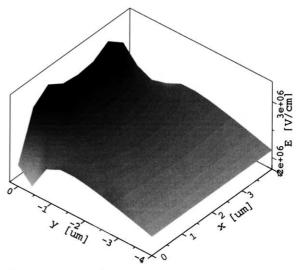

Figure 7. Electric field profile at the breakdown voltage.

progressively from the value for the unterminated diode with increasing field plate overlap until  $x_0$  is approximately equal to the depletion width at breakdown.

The field enhancement factor for unterminated Schottky diodes varies from approximately 2 for highly doped devices ( $\sim 10^{17}$  cm<sup>-3</sup>) to approximately 4 for diodes with a doping level of  $\sim 10^{15}$  cm<sup>-3</sup>. For diodes with edge termination the field enhancement factor varies from approximately 1.2 to 2.0 over the same range of doping levels as shown in Fig. 6.

From the electric field profile shown in Fig. 7 one can

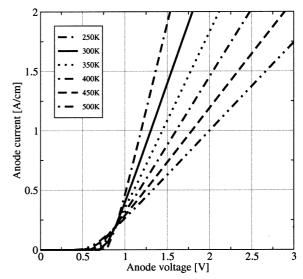

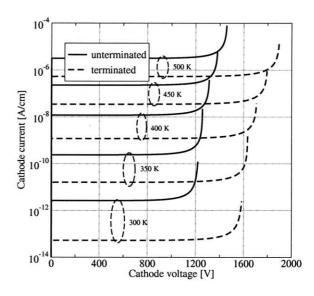

Figure 8. Comparison of unterminated and field terminated reverse voltage characteristics at different temperatures.

see that the peak electric field in the epitaxial layer occurs directly under the corner of the Schottky contact. The electric field directly under the center of the Schottky contact is smaller than the value under the corner.

Fig. 8 shows that the field plate edge terminated Ni-SiC Schottky barrier diodes improve the breakdown voltage by 35% while simultaneously reducing the leakage current by two orders of magnitude at room temperature and nearly by a factor of 10 at 500 K compared to the unterminated Schottky barrier diodes.

## 5. Conclusion

A new device structure that improves the breakdown voltage of Ni-SiC Schottky diodes by utilizing field plate edge termination is proposed. Numerical investigations on how the addition of the field plate affects the relationship between the device structure, performance, and reliability have been performed. The key parameters that alter the overall device performance are optimized using the general-purpose device simulator MINIMOS-NT. This structure improves the breakdown voltage by 35% compared to Schottky diodes without edge termination. The ratio of the maximum field under the anode corner to the field under the center of the contact at the same depth is reduced to 50% for an edge terminated diode compared with an unterminated counter part. The leakage current during the reverse biased operation for edge terminated structure is reduced by a factor of 100 at room temperature and nearly by a factor of 10 at 500 K.

# Acknowledgment

This work has been partly supported by *Infineon Technologies*, Villach, and *austriamicrosystems*, Unterpremstätten, Austria.

# References

- [1] J. W. Palmour, R. Singh, R. Glass, O. Kordina, and C. H. Carter, Jr., "Power Semiconductor Devices and IC's," in *Proceedings of the International Symposium on Power Semiconductor Devices and ICs*, pp. 25–32, 1997.

- [2] P. G. Neudeck, "SiC Technology," in The VLSI Handbook, The Electrical Engineering Handbook Series, W.-K. Chen, Ed. Boca Raton, Florida: CRC Press and IEEE Press, pp. 6.1–6.24, 2000.

- [3] V. A. K. Temple, "Junction Termination Extension (JTE), A New Technique for Increasing Avalanche Breakdown Voltage and Controlling Surface Electric Fields in p-n Junctions," in *Technical Digest.*, International Electron Devices Meeting, pp. 423–426, 1977.

- [4] D. Alok, B. J. Baliga, and P. K. McLarty, "A simple Edge Termination for Silicon Carbide Devices With

- Nearly Ideal Breakdown Voltage," *IEEE Electron Device Lett.*, vol. 15, no. 10, pp. 394–395, 1994.

- [5] A. Itoh, T. Kimoto, and H. Matsunami, "Excellent Reverse Blocking Characteristics of High Voltage 4H-SiC Schottky Rectifiers With Boron-Implanted Edge Termination," *IEEE Electron Device Lett.*, vol. 17, no. 3, pp. 139–141, 1996.

- [6] K. Ueno, T. Urushidani, K. Hashimoto, and Y. Seki, "The Guard-Ring Termination for the High-Voltage SiC Schottky Barrier Diodes," *IEEE Electron Device Lett.*, vol. 16, no. 7, pp. 331–332, 1995.

- [7] Institute for Microelectronics, TU Vienna, Austria, *Minimos-NT, Device and Circuit Simulator, User's Guide*, 2002. http://www.iue.tuwien.ac.at/mmnt/.

- [8] T. Ayalew, SiC Semiconductor Devices Technology, Modeling, and Simulation. Dissertation, TU Vienna, 2004. http://www.iue.tuwien.ac.at/phd/ayalew/.

- [9] J. Crofton and S. Sriram, "Reverse Leakage Current Calculations for SiC Schottky Contacts," *IEEE Trans. Electron Devices*, vol. 43, no. 12, pp. 2305–2307, 1996

- [10] A. Itoh, T. Kimoto, and H. Matsunami, "Efficient Power Rectifiers of 4H-SiC," in *Proceedings of the 7th Interna*tional Symposium on Power Semiconductor Devices and ICs, ISPSD'95, pp. 101–105, 1995.

- [11] M. J. Bozack, "Surface Studies on SiC as Related to Contacts," *Phys. stat. sol.* (b), vol. 202, no. 1, pp. 549– 580, 1997.

- [12] A. Itoh, O. Takemura, T. Kimoto, and H. Matsunami, "Barrier Height Analysis of Metal/4H-SiC Schottky Contacts," *Inst. Phys. Conf. Series*, no. 142, pp. 685–688, 1996.

- [13] D. Defives, O. Durand, F. Wyczisk, O. Noblanc, C. Brylinski, and F. Meyer, "Electrical Behaviour and Microstructural Analysis of Metal Schottky Contacts on 4H-SiC," *Microelectronic Engineering*, vol. 55, no. 1-4, pp. 369–374, 2001.

- [14] C. M. Zetterling, Process Technology for Silicon Carbide Devices. EMIS series, no. 2, INSPEC, IEE, UK, 2002.

- [15] S. M. Sze, Semiconductor Devices: Physics and Technology. John Wiley & Sons, Inc., 2nd ed., 2002.

- [16] M. Bhatnagar, B. J. Baliga, H. R. Kirk, and G. A. Rozgonyi, "Effect of Surface Inhomogeneities on the Electrical Characteristics of SiC Schottky Contacts," *IEEE Trans. on Electron Devices*, vol. 43, no. 1, pp. 150–156, 1996.

- [17] D. Schroeder, Modeling of Interface Carrier Transport for Device Simulation. Springer, 1994.

- [18] T. Ayalew, A. Gehring, J. M. Park, T. Grasser, and S. Selberherr, "Improving SiC Lateral DMOSFET Reliability Under High Field Stress," *Journal of Microeectronics Reliability*, vol. 43, no. 9-11, pp. 1889–1894, 2003.