# Numerical Simulation and Optimization for 900V 4H-SiC DiMOSFET fabrication

S. C. Kim<sup>1, a</sup>, W. Bahng<sup>1,b</sup>, N. K. Kim<sup>1,c</sup>, E. D. Kim<sup>1,d</sup> T. Ayalew<sup>2,e</sup>, T. Grasser<sup>2,f</sup>, and S. Selberherr<sup>3,g</sup>

<sup>1</sup>Power Semiconductor Research Group, Korea Electrotechnology Research Institute (KERI), Sung-ju dong 28-1, ChangWon-city, Gyungnam 641-120 Korea

<sup>2</sup>Christian Doppler-Laboratory for TCAD in Microelectronics at the Institute for Microelectronics, TU Vienna, Gusshausstrasse 27-29, A-1040 Vienna, Austria

<sup>3</sup>Institute for Microelectronics, TU Vienna, Gusshausstrasse 27-29, A-1040 Vienna, Austria

<sup>a</sup>sckim@keri.re.kr, <sup>b</sup>bahng@keri.re.kr, <sup>c</sup>nkkim@keri.re.kr, <sup>d</sup>edkim@keri.re.kr, <sup>e</sup>ayalew@iue.tuwien.ac.at, <sup>f</sup>grasser@iue.tuwien.ac.at, <sup>g</sup>selberherr@iue.tuwien.ac.at

Keywords: DiMOSFET, Edge Termination, Silicon Carbide, MINIMOS-NT

**Abstract.** We report the simulation results of 25µm half cell pitch vertical type 4H-SiC DiMOSFET using the general-purpose device simulator MINIMOS-NT. The best trade-off between breakdown voltage and on-resistance in terms of BFOM is around 19MW/cm² with a p-well spacing 5µm. The specific on -resistance,  $R_{ON, sp}$ , simulated with  $V_{GS}$ =10V and  $V_{DS}$ =1V at room temperature, is around 22.76m $\Omega$ cm². An 900V breakdown voltage is simulated with ion-implanted edge termination.

## Introduction

In power switching devices, Silicon was approached their theoretical limits in late 1980s [1]. Therefore many research works has been done using wideband gap semiconductor materials, especially Silicon Carbide or semiconducting diamond. Silicon Carbide has been around for over a century. However, only in the past two or three decades its semiconducting properties have been sufficiently studied and applied, especially for high-power and high-frequency devices. In this paper, we present numerical simulation-based optimization results of DiMOSFET with various edge termination using the general-purpose device simulator MINIMOS-NT [2].

# **Device Design**

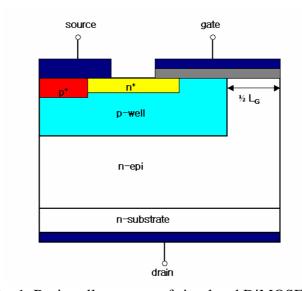

A cross section of the simulated DiMOSFET cell is shown in Fig. 1. The DiMOSFET structure is formed in SiC using a double implantation with two separate implantation masks. The initial wafer specification, which is commecially available wafer, is  $10\mu m$  thick drift layer with doping concentration of  $5\times10^{15} cm^{-3}$ . P-well, with a surface concentration of around  $5\times10^{17} cm^{-3}$ , is formed by boron multiple implantation. We use experimental data of multiple energy boron implants for simulation and p-well junction depth is  $0.6\mu m$ . Generally aluminum is used for p-well region, but we use boron impurities as p-well region to compare the experimental device which we will fabricate. Then a  $0.2\mu m$  deep p+ region for an ohmic contact was formed with a box profile concentration of  $5\times10^{19} cm^{-3}$ . Nitrogen implants are used for n+ source region, and the peak concentration and junction depth are  $5\times10^{19} cm^{-3}$  and  $0.15\mu m$ , respectively. Finally a 50nm gate oxide is formed. The ion-implanted edge termination has been realized in the same way, but with a lower dose, to achieve a box profile at about  $1.5\times10^{16} cm^{-3}$ .

For device simulation, we have utilized published material data in Table 1. Impact ionization is a typical non-equibrium process which requires large electric fields. It is modified by the reciprocal of the mean free path which is denoted the impact ionization coefficient. A review of measured data on impact ionization coefficients in  $\alpha$ -SiC has been first published by Ruff et. al. and later by Bakowsky st. at., but most recently measured data compiled by Raghunathanr and Baliga at different temperatures show an about 20% higher critical electric field compared to the previous reports. It seems that the impact ionization coefficients are decreasing with increasing temperature. This implies the increase of the breakdown voltage, which is a desirable property for SiC power devices. The average impact ionization coefficients  $a_n$  and  $a_p$  are summarized in Table 1.

The mobility commonly measured is perpendicular to the c-axis. It is different from the mobility parallel to the c-axis. The difference between the two mobilities has been stuided experimentally. In 4H-SiC, ratio between perpendicular and parallel mobility is generally 0.8.

Fig. 1. Basic cell structure of simulated DiMOSFET.

Table 1. Model parameter used for simulating 4H-SiC DIMOSFET

| Electron mobility                    | Hole mobility                   | Donors &                 | Acceptors &           | Saturated Electron        |

|--------------------------------------|---------------------------------|--------------------------|-----------------------|---------------------------|

| l *                                  | $\mu_{\rm p}$                   | Ionization Energy        | Ionization Energy     | Velocity                  |

| $N_{\rm D} = 10^{16}  {\rm cm}^{-3}$ | $N_A = 10^{16} \text{ cm}^{-3}$ | [meV]                    | [meV]                 | $v [10^7 \text{ cm / s}]$ |

| c-axis : 900                         | 115                             | N:50,92                  | Al: 200               | 2                         |

| ⊥ c axis : 800                       | 113                             | P: 54, 93                | B: 285                | 2                         |

| $\alpha_n$ [cm <sup>-1</sup> ]       | b <sub>n</sub> [V/cm]           | $\alpha_p$ [cm $^{-1}$ ] | b <sub>p</sub> [V/cm] | ←ω <sub>op</sub> [meV]    |

| $3.44 \times 10^6$                   | $2.58 \text{x} 10^7$            | $3.5 \times 10^6$        | 1.7x10 <sup>7</sup>   | 106                       |

#### **Simulation Results and discussion**

In order to achieve acceptable device performance, the maximum electric field in the oxide layer must be limited. For the desired breakdown voltage of 900V, the proposed device structure is optimized to have a  $25\mu m$  half cell pitch and a  $10\mu m$  thick n-drift region doped at  $5x10^{15}cm^{-3}$ . The doping

concentration and the thickness of the p-well region are very important. If we decrease the p-well doping concentration below  $3x10^{17} \text{cm}^{-3}$ , the blocking voltage decreases because of a punchthrough. If we increase it further, the maximum operating voltage becomes limited by the maximum oxide field. The best trade-off between these relations has been achieved by setting the p-well doping concentration to  $5x10^{17} \text{cm}^{-3}$ .

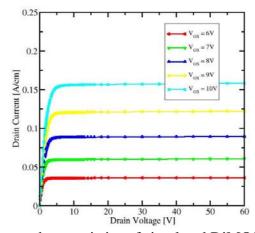

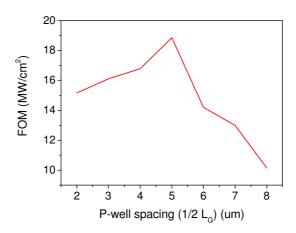

Fig. 2 shows the on-state characteristics of simulated DiMOSFET at room temperature. The specific on-resistance,  $R_{ON,sp}$ , simulated with  $V_{GS}$ =10V and  $V_{DS}$ =1V at room temperature, is around  $22.76 \text{m}\Omega\text{cm}^2$ . The specific on-resistance depends on the gate bias. A high gate bias was required to turn the device fully on. This means that the on-resistance is dominated by the MOS channel resistance at room temperature[2]. So that reducing the on-resistance results in increasing high channel mobility. In this simulation, the device has an MOS channel mobility of  $84 \text{cm}^2/\text{V}s$  and a threshold voltage of around 6V. These specific-on resistance simulation results are introduced into Baliga's Figure of Merit (BFOM) as the criterion for structure optimization and comparision[3,4]. Fig. 3 shows the simulated results of BFOM depending on the p-well spacing. As shown in Fig. 3, the best trade-off relation between breakdown voltage and on-resistance in terms of BFOM is achieved with a p-well spacing 5µm.

Fig. 2. Drain current characteristics of simulated DiMOSFET devices.

Fig. 3. Effects of p-well (1/2 L<sub>G</sub>) spacing on the Baliga's Figure of Merit.

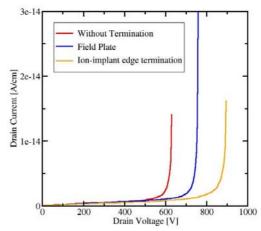

Fig 4. shows the breakdown voltage characteristics according to the termination structures. The two types of edge termination are simulated at 400K. One clear difference among the three structures is a higher breakdown voltage for the ion-implanted edge termination structure. In this figure, an ion-implanted edge termination structure improved the breakdown voltage from 720V to 900V

compared with the field plate structure. The no edge termination, field plate and ion-implanted edge termination structures feature 600, 720, and 900V breakdown voltages, respectively. The breakdown voltages are approximately 35, 45 and 53% of the ideal breakdown voltage in this DiMOSFET devices, respectively. In this simulation, the maximum electric field in the bulk region is 2.69MV/cm, which is 89% of the breakdown field in 4H-SiC. And also, the maximum electrical field in the gate oxide is 20% lower than the bulk electrical field, i.e. 2.16MV/cm.

Fig. 4. Comparison of the breakdown voltage depending on the termination structures.

# **Summary**

In this study, vertical DiMOSFET was simulated, and electrical characteristics were presented using the general-purpose device simulator MINIMOS-NT. The best trade-off between breakdown voltage and on-resistance is achieved with a p-well spacing 5 $\mu$ m. The specific on -resistance, R<sub>ON, sp</sub>, simulated with V<sub>GS</sub>=10V and V<sub>DS</sub>=1V at room temperature, is around 22.76m $\Omega$ cm<sup>2</sup>. As the spacing between the p-well regions is increased to reduce the JFET resistance, the area of the device also increase, resulting larger R<sub>ON, sp</sub>. The devices have an MOS channel mobility of 84cm<sup>2</sup>/V·s and a threshold voltage of 6V. The on-resistance is dominated by the MOS channel resistance, therefore, high channel mobility is necessary to improve device performance. We compare the termination structures. Among three types, ion-implanted edge termination structure has best blocking capability. The breakdown voltage of around 900V is simulated in ion-implanted edge termination structure.

### Acknowledgement

This work was done as a part of SiC Device Development Program (SiCDDP) supported by MOCIE(Ministry of Commerce, Industry and Energy) Korea.

## References

- [1] Institute for Microelectronics, Vienna University of Technology, MINIMOS-NT User's Guide, 2002. <a href="http://www.iue.tuwien.ac.at/mmnt/">http://www.iue.tuwien.ac.at/mmnt/</a>.

- [2] Sei-Hyung Ryu, Anant Agarwal, James Richmond, John Palmour, Nelson Saks, and John Williams, IEEE Electron Device Letters, Vol. 23, No. 6(2002), 321-323

- [3] B. J. Baliga, Power Semiconductor Devices, PWS Publishing Company, 1996.

- [4] Handoko Linewih, Sima Dimitrijev, IEEE Transaction on Electron Devices, Vol. 48, No. 8(2001), pp.1711-1717