## Negative Bias Temperature Instability Modeling for High-Voltage Oxides at Different Stress Temperatures

R. Entner\*, T. Grasser\*, H. Enichlmair°, and R. Minixhofer°

\*Christian Doppler Laboratory for TCAD in Microelectronics at the Institute for Microelectronics, TU Wien, Gusshausstrasse 27–29/E360, 1040 Wien, Austria

°austriamicrosystems, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria

Phone: +43/1/58801/36050, Fax: +43/1/58801/36099, E-mail: entner@iue.tuwien.ac.at

Negative bias temperature instability (NBTI) of pMOS structures is a critical reliability concern for modern semiconductor devices. We propose and evaluate an enhanced NBTI model with the following additions to the standard reaction-diffusion (RD) model [1] (a) coupling to the semiconductor device equations to self-consistently include the oxide field, surface hole concentration, charged carriers, fast interface states (Fermi-level dependent charges), and slow oxide charges, (b) fully dynamic dispersive multiple trapping transport equations [2], in contrast to the commonly used non-equilibrium approximation [3, 4] or standard diffusion equations [1, 5], (c) generalized equations suitable to describe transport and trapping of either  $H^0$  or  $H_2$ , (d) distributed oxide charges with different dynamics, in contrast to a fixed relation between interface and oxide traps. The oxide charges are generated by the diffusing species at oxide defects (E' centers [6]) forming slow positive charges ( $H_2$  is cracked first [7] while  $H^0$  is trapped right away) turning them into hydrogen complexed E' centers [8]. Although for ultra-thin oxides the importance of oxide charges is controversial [9, 10], for thicker oxides, as used in power and high-voltage devices, they are fundamental [11].

Coupling the RD model to the semiconductor equations requires some care. Most importantly, the concentration of amphoteric  $P_{\rm b}$  centers needs to be translated to the electrically active interface density-of-states where in addition to the band-tail states,  $P_{\rm b}$  centers introduce two dynamically changing distinct peaks in the Si bandgap [12,13]. Furthermore, since at least a complete 2D geometry has to be considered, the computational effort increases considerably. However, the advantages are manifold. First, the feedback of the various charges on the RD model is considered and, most importantly,  $V_{\rm th}$  shifts can be extracted by mimicking the dynamics of the measurement process (stress interruption, unavoidable relaxation,  $V_{\rm G}$  sweep, and  $I_{\rm D}$  monitoring) instead of relying on relations like  $\Delta V_{\rm th} \approx -{\rm q}(N_{\rm it}+N_{\rm ot})/C_{\rm ox}$ .

To evaluate the model we consider a high-voltage pMOS structure with a gate oxide thickness of 48 nm which was stressed at  $V_{\rm G}=-25\,\rm V$  at four different temperatures ( $T_{\rm L}=100,\,125,\,150,\,$  and 175 °C). For such thick oxides, a strongly reduced recovery is observed as compared to thinner oxides [14], which is challenging to model. In standard RD models, this partial recovery can be described by allowing an outflow and therefore a loss in the mobile particles. In our more realistic model, particles cannot simply disappear, they either diffuse away more quickly, for instance into the poly, or they are trapped in various defects. However, this requires an accurate trap density-of-states to cover the dynamics of the process.

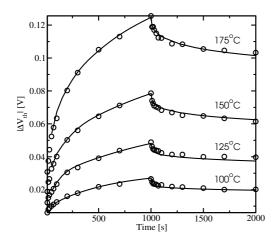

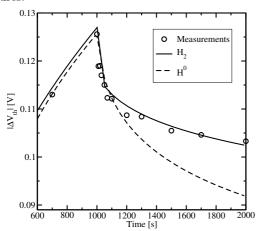

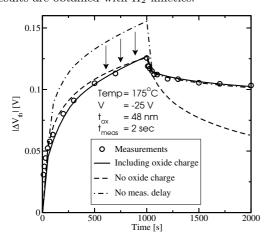

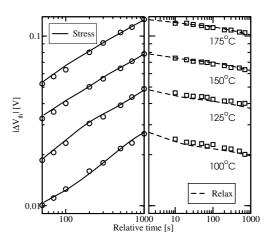

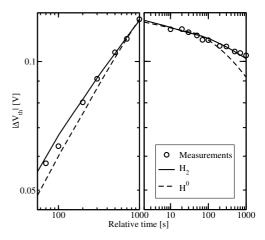

Fig. 5 depicts the simulation results for a  $1000\,\mathrm{s}$  stress and relaxation cycle with and without the inclusion of oxide traps in the  $\mathrm{H}_2$  model, while Fig. 3 and 4 also show the results for the  $\mathrm{H}^0$  model. A fast and slow contribution can be observed during the relaxation phase which can be best described with the  $\mathrm{H}_2$  model. In Fig. 1 and 2 the agreement for a wide range of temperatures can be seen, which can be achieved with a single set of model parameters. During the faster process within the first few seconds the annealing is attributed to re-passivation of dangling  $\mathrm{Si/SiO}_2$  interface bonds. This process is governed by the availability of mobile hydrogen near the interface. After the consumption of all available hydrogen new hydrogen can only be provided by de-trapping in the oxide bulk. To properly capture both phases, the density-of-states used in the dispersive transport equation is modeled by an exponential tail for the shallow traps (as used in analytical approximations [3,4,15]) while the slow process is governed by deep traps given by an additional Gaussian peak well below the hydrogen conduction band.

**Figure 1:** Comparison of the measurements to the simulation results at different temperatures. One set of model parameters fits nicely to a wide range of temperatures.

**Figure 3:** Comparison of the measurements to simulation results using the  $H_2$  and the  $H^0$  model. Best results are obtained with  $H_2$  kinetics.

Figure 5: Comparison of the measurements to simulation results ( $H_2$  model). The measurements can only be described by properly accounting for the measurement delays during the stress phase and by including the generation of oxide charges.

**Figure 2:** Comparison of the measurements to the simulation results at different temperatures in log-log scale.

**Figure 4:** Comparison of the measurements to simulation results in log-log scale.

- K. Jeppson and C. Svensson, J.Appl.Phys. 48, 2004 (1977).

- [2] J. Noolandi, Phys.Rev.B  ${\bf 16},\,4466$  (1977).

- [3] V. Arkhipov and A. Rudenko, Philos.Mag.B 45, 189 (1982).

- [4] B. Kaczer et al., Appl.Phys.Lett. 86, 1 (2005).

- [5] S. Ogawa and N. Shiono, Phys.Rev.B 51, 4218 (1995).

- [6] P. Lenahan and J. Conley Jr., J.Vac.Sci.Technol.B 16, 2134 (1998).

- [7] A. Edwards, Phys.Rev.B 44, 1832 (1991).

- [8] K. L. Brower, Appl.Phys.Lett. 53, 508 (1988).

- [9] S. Mahapatra et al., Microelectronic Engineering 80, 114 (2005).

- $[10]\,$  V. Huard et~al., Microelectron. Reliab. 46, 1 (2006).

- [11] N. Stojadinović et al., Microelectron.Reliab. 45, 1343 (2005).

- [12] E. Poindexter et al., J.Appl.Phys. 56, 2844 (1984).

- [13] A. Haggag et al., in High-performance Chip Reliability from Short-Time-Tests (2001), pp. 271–279.

- [14] M. Alam and S. Mahapatra, Microelectron.Reliab. 45, 71 (2005).

- [15] S. Zafar, J.Appl.Phys.  $\bf 97$ , 1 (2005).