# **Three-Dimensional Transient Interconnect Analysis With Regard to Mechanical Stress**

S. Holzer<sup>1</sup>, C. Hollauer<sup>1</sup>, H. Ceric<sup>1</sup>, M. Karner<sup>1</sup>, T. Grasser<sup>2</sup>, E. Langer<sup>1</sup>, and S. Selberherr<sup>1</sup>

Institute for Microelectronics, TU Wien, Gußhausstraße 27-29/E360, 1040 Wien, Austria

Christian Doppler Laboratory for TCAD in Microelectronics at the Institute for Microelectronics, TU Wien Phone: +43-1-58801-36015 Fax: +43-1-58801-36099 Email: Holzer@iue.tuwien.ac.at

### 1. Introduction

The complexity of today's semiconductor devices is increasing steadily and, in particular, the involved interconnecting structures are becoming one of the dominantly straining factors for the global performance and reliability due to rising thermal effects [1]. Shrinking of device feature sizes requires a significant reduction of the interconnect geometries, which enhances the electrical and mechanical stress burden. In addition, the presence of high temperature gradients in interconnect structures is known as a significant electromigration promoting factor [2]. Furthermore, thermal expansion mismatch between the involved materials causes additional mechanical stresses which contribute an important part for rising electromigration failure [3, 4].

Our analysis of interconnect behavior under certain operating conditions combines three-dimensional electro-thermal transient investigations with thermo-mechanical analysis of back end of line (BEOL) structures. This requires a rigorous development of thermal models to predict the transient thermal behavior of complex structures, especially, since reliability issues are investigated.

## 2. Electro-Thermal and Thermo-Mechanical Models

For the electro-thermal investigations we perform a transient analysis with self-heating using EULER's equation

$$\nabla \cdot (\sigma(T)\nabla \varphi) = 0 \tag{1}$$

and the heat conduction equation

$$\nabla \cdot (\lambda(T)\nabla T) = c_p \rho_m \partial_t T - H_{TH}$$

(2)

to obtain the electrical potential  $\varphi$  and the temperature T. Here, (1) represents the continuity equation with the electrical conductivity  $\sigma$  and the electrical potential as intrinsic quantities of interconnect structures. The temperature T is determined by the thermal conductivity  $\lambda$ , the specific heat capacitance  $c_p$ , the specific mass density, and the heat source term  $H_{TH}$ . The heat source term  $H_{TH}$  in (2) is modeled as the JOULE's power loss, which remains valid for analysis of interconnect materials [5] over wide temperature ranges

$$H_{TH} = \sigma(T) \|\nabla \varphi\|^2. \tag{3}$$

The material parameters for the electrical and thermal conductivity are modeled with a polygonal approach as

$$\sigma(T) = \frac{\sigma_0}{1 + \alpha_{\sigma}(T - T_0) + \beta_{\sigma}(T - T_0)^2} \tag{4}$$

and

$$\lambda(T) = \frac{\lambda_0}{1 + \alpha_{\lambda}(T - T_0)},\tag{5}$$

respectively. Both models have a certain initial value  $\sigma_0$  and  $\lambda_0$  at a reference temperature  $T_0$ . The coefficients  $\alpha_{\sigma}$  and  $\alpha_{\lambda}$  denote the first order temperature coefficients of the conductivity models. For the electrical conductivity model, a second order temperature coefficient  $\beta_{\sigma}$  is necessary. For the specific heat capacitance, SHOMATE's model [6] has been chosen to determine the temperature dependence.

As solution we obtain the temperature distribution on the whole interconnect structure from the electro-thermal investigations. The mechanical subsystem in conjunctions with the previously obtained temperature distribution yields to a thermo-mechanical equation system [7, 8], where the temperature-dependent stress development due to thermal expansion and mismatch can be formulated as

$$\varepsilon_{ij} = \frac{1}{2} \left( \frac{\partial u_i}{\partial x_j} + \frac{\partial u_j}{\partial x_i} \right) \tag{6}$$

$$\sigma_{ij}(T) = B\alpha(T - T_0)\delta_{ij} + \varepsilon_{kk}\delta_{ij} + 2\mu\varepsilon_{ij}$$

(7)

$$\frac{\partial \sigma_{ij}}{\partial x_i} = 0. ag{8}$$

Here,  $u_i$  represents the components of the displacement vector and the bulk modulus is denoted by B. The thermal volume expansion coefficient is represented by  $\alpha$ , and  $\mu$  and  $\lambda$  determine LAME's constants. The strain tensor  $\widetilde{\mathcal{E}}$  and the stress tensor  $\widetilde{\sigma}$  are determined by their components  $\varepsilon_{ij}$  and  $\sigma_{ij}$ , respectively. To determine the mechanical load inside the structure we calculate the hydrostatic pressure p by

$$p = -\frac{trace(\widetilde{\sigma})}{3} = -\frac{\sum \sigma_{ij} \delta_{ij}}{3}.$$

(9)

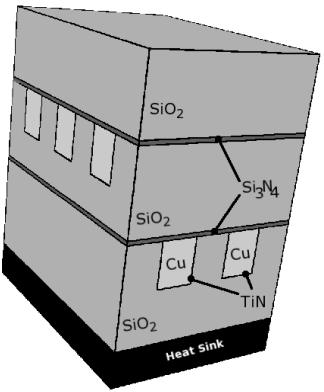

<u>Fig. 1</u>: The material composition of the investigated interconnect structure.

## 3. Simulation Results

The interconnect structure depicted in Fig. 1 has been investigated electro-thermally by using the presented models with the three-dimensional interconnect simulator STAP [9] and with the diffusion and oxidation simulator FEDOS [10] using the stress calculation mode for the thermo-mechanical investigation.

The presented interconnect structure (cf. Fig. 1) consists of several interconnect lines made of copper which are embedded in SiO<sub>2</sub> as inter layer dielectrics (ILD), TiN as barrier material for copper, and Si<sub>3</sub>N<sub>4</sub> passivation layers. At the bottom of the structure, a silicon substrate acts as a stabilized heat sink at 350 K to reflect typical operation conditions.

For the investigated structure, the electro-thermal equation system (1)-(3) is solved using the appropriate thermal models for the material parameters obtained from literature [11, 12] and presented in Tab. 1 and 2. Additional parameters and their ranges of validity can be found in [13-17].

<u>Tab. 1</u>: Mechanical material parameters

| Quantity                    |         | Si     | U. U =  | Si3N4  | TiN    |

|-----------------------------|---------|--------|---------|--------|--------|

| E [GPa]                     | 115     | 180    | 73      | 380    | 600    |

| E [GPa]<br>v [1]<br>α [1/K] | 0.34    | 0.22   | 0.17    | 0.27   | 0.25   |

| α [1/K]                     | 17.7E-6 | 2.7E-6 | 0.55E-6 | 3.3E-6 | 9.4E-6 |

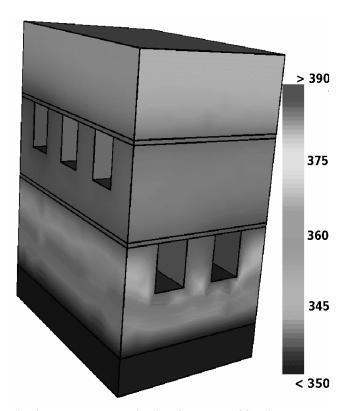

<u>Fig. 2</u>: Temperature distribution [K] at 90μs in the ILD, barrier, and passivation layers.

At t = 0, a positive voltage has been applied at the lower interconnect line. The upper copper lines have been grounded to 0V in order to observe the transient heating of the structure. Furthermore, the characteristics of the line resistance as well as the maximum temperature are of interest for investigations on stress and electromigration.

As a result of the electro-thermal simulation, we obtain the temperature distribution in the ILD, barrier, and passivation layers, as shown in Fig. 2, and the current density and the temperature distribution inside the copper lines as a direct result of the applied biases. Due to the high thermal conductivity of copper, the temperature gradient inside of one copper line is negligible. Therefore, Fig. 2 shows the temperature distribution outside of the metallization for the ILD, barrier, and passivation layers at  $t = 90\mu s$ . The figure clearly depicts high temperature gradients between the heat sink and the first heated metal layer.

Tab. 2: Electrical material parameters

| Quantity                         | Cu     | Si     | SiO2    | Si3N4  | TiN    |

|----------------------------------|--------|--------|---------|--------|--------|

| σ₀ [S/m]                         | 5.2E+7 | 0.01   | 0.0     | 0.0    | 1.6E+5 |

| α <sub>σ</sub> [1/K]<br>λ [W/Km] | 4.2E-3 | 0.0    | 0.0     | 0.0    | 0.4E-3 |

| λ [W/Km]                         | 400    | 119    | 1.39    | 12.07  | 48.2   |

| αλ [1/K]                         | 0      | 4.7E-3 | -0.9E-3 | 2.0E-3 | 5.8E-3 |

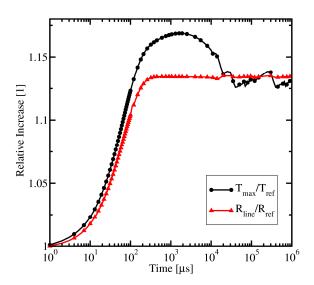

<u>Fig. 3</u>: The transient evolution of the maximum temperature inside the interconnect structure and the corresponding line resistance. The reference resistance  $R_{\rm ref}=0.2\Omega$  at the reference temperature  $T_{\rm ref}=350K$

The ILDs in both the lower and the higher metallization layer show a global heat up due to the high thermal conductivity of the surrounding metal lines. This observed effect of global warming causes heat-up of regions that are not electrically stressed. However, these regions get also thermally and mechanically stressed.

An overview of the transient evolution of the maximum temperature and the corresponding lines resistance is presented in Fig. 3. for a large time scale. Obviously, an exponential increase of the temperature and of the overall resistance of the interconnect structure has been observed at the beginning of the electrical stressing. At approximately 150µs after applying the bias, the line resistance saturates and reaches a maximum value, but the temperature shows a further increase, if overshoots the expected stationary value and reaches the stationary value after a decaying oscillation.

With the obtained temperature distribution, we setup the mechanical sub problem as described in Section 2. For the simulation, the parameter values shown in Tab. 1 are used to determine the stress distribution inside the interconnect structure.

The heat sink has been assumed to be fixed at the bottom for the mechanical subsystem while the other surfaces of the structure are not constricted.

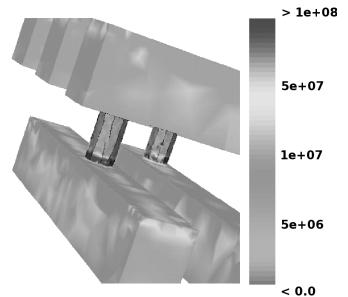

As a result of the thermo-mechanical simulation with FEDOS, we obtained the stress distribution for the presented interconnect structure in Fig. 1. In order to depict the result, the hydrostatic pressure is calculated according to (9). Fig. 4 shows the hydrostatic pressure in Pa of the different parts of the presented structure. As expected, the barrier layers in the

Fig. 4: Hydrostatic pressure distribution [Pa] for the vias and interconnect lines. Large gradients are shown at material interfaces and surfaces.

vias represent the regions where the highest mechanical stresses occur. This can be explained by the different thermal expansion coefficients. As the barrier layer TiN has a three times larger volume expansion coefficient than the passivation layer  $Si_3N_4$ , the occurring stress is positive as well as at the interface Cu and ILD.

The difference of the mechanical properties between the interfaces of the copper lines and the barrier layer inside the vias is that the materials inside the interconnect material have a different space to relax. Due to the large volume of copper, the mechanical stress can decay by diffusion and relaxation processes.

These indicated regions as well as interfaces with edges and corners present the high risk areas inside of interconnect structures for electromigration.

Further promoting factors for electromigration are high temperature and stress gradients [2-4], weak material adhesion, and impurities which decrease the activation energy for diffusion [18-21].

## 4. Conclusion

We presented a transient electro-thermal analysis with STAP considering self-heating. Thermo-mechanical simulators, e.g. FEDOS, are coupled to provide appropriated input data for electromigration analysis to obtain predictive results.

The presented electro-thermal results depict the high temperature gradients close to heat sources and heat sinks. Further regions of high risk of electromigration are presented as results of thermo-mechanical simulations. The vias as well as edges and corners of interconnects in general are highly stressed regions due to the mismatch of thermal volume expansion coefficients and due to weak material adhesion of material interfaces.

In addition, areas with large current densities have to be well considered. The activation energy for diffusion in copper can be drastically enhanced in conjunction with high temperature gradients inside the metal lines. Hence, the higher diffusion rate of copper results in a large vacancy concentration as well as in a high ion current density which reduces the time to failure due to electromigration because of the high mass fluxes of copper atoms.

Therefore, rigorous electro-thermal as well as thermomechanical investigations have to be carried out in advance to predict the transient behavior and to reduce the promoting factors for electromigration.

In general, the mechanical simulations in conjunction with electrical and thermal analysis within a TCAD framework enable the prediction of the influence of the heat flux. The results show how global warming affects the intended performance of the device structures and their reliability.

#### References

- K. Banarjee and A. Mehrotra, "Coupled Analysis of Electromigration Reliability and Performance in ULSI Signal Nets", Proc. 2001 International Conference on Computer-Aided Design, pp. 158–164, 2001.

- [2] R. Kircheim, "Stress and Electromigration in Al-Lines of Integrated Circuits", Acta Metallurg. ET Mater., vol. 40, no. 2, pp. 309–323, 1992.

- [3] D. Dalleau and K. Weide-Zaage, "Three-Dimensional Voids Simulation in Chip Metallization Structures: A Contribution to Reliability Evaluation, "Microelectron. Reliab., vol. 41, no. 9-10, pp. 1625–1630, 2001.

- [4] X. Yu and K. Weide, "A Study of the Thermal, Electrical, and Mechanical Influence on Degradation in an Aluminum-Pad Structure", Microelectron. Reliab., vol. 37, no. 10-11, pp. 1545–1548, 1997.

- [5] G. Wachutka, "Rigorous Thermodynamic Treatment of Heat Generation and Conduction in Semiconductor Device Modeling", IEEE Trans. Computer-Aided Design, vol. 9, pp. 1141–1149, Nov. 1990.

- [6] C. H. Shomate, "Method for Evaluating and Correlating Thermodynamic Data", J.Phys.Chem, vol. 58, no. 4, pp. 368-372, 1954.

- [7] O. C. Zienkiewicz, "The Finite Element Method: Basic Formulation and Linear Problems." England: McGraw-Hill, 1987.

- [8] F. Ziegler, "Mechanics of Solids and Fluids", Springer, New York, 1995.

- [9] R. Sabelka and S. Selberherr, "Finite Element Simulator for Three-Dimensional Analysis of Interconnect Structures", Microelectronics Journal, vol. 32, no. 2, pp. 163–171, 2001.

- [10] Ch. Hollauer, H. Ceric, and S. Selberherr, "Three-Dimensional Simulation of Thermal Oxidation and the Influence of Stress", in "ECS Transactions: Physics and Chemistry of SiO<sub>2</sub> and the Si-SiO<sub>2</sub> Interface-5 vol. 1 no. 1", Eds. H.Z. Massoud, J.H. Stathis, T. Hattori, D. Misra, and I. Baumvol, pp. 103–113, 2005.

- [11] S. Holzer, R. Minixhofer, C. Heitzinger, J. Fellner, T. Grasser, and S. Selberherr, "Extraction of Material Parameters Based on Inverse Modeling of Three-Dimensional Interconnect Fusing Structures", Microelectronics Journal, vol. 35, no. 10, pp. 805–810, 2004

- [12] C. Hollauer, S. Holzer, H. Ceric, S. Wagner, T. Grasser, and S. Selberherr, "Investigation of Thermo-Mechanical Stress in Modern Interconnect Layouts", in Proc. The Sixth International Congress on Thermal Stresses, Schriftenreihe der Technischen Universität Wien, vol. 2, pp. 637–640, 2005.

- [13] R. Sabelka, "Dreidimensionale Finite Element Simulation von Verdrahtungsstrukturen auf integrierten Bauelementen", PhD Thesis, Institute for Microelectronics, TU Wien, Austria, 2001.

- [14] S. Selberherr, "Analysis and Simulation of Semiconductor Devices", Springer, Wien, New York, 1984.

- [15] K. Yamaguchi and K. Itakagi, "Measurements of High Temperature Heat Content of Silicon by Drop Calorimetry", Journal of Thermal Analysis and Calorimetry, vol. 69, pp. 1059-1066, 2002.

- [16] M. Case, "NIST-JANAF Thermochemical Tables, Forth Edition", J.Phys.Chem.Ref.Data, pp. 1-1951, 1988.

- [17] A. Cezairliyan, "Specific Heat of Solids", Hemisphere Publishing Corp., 1988.

- [18] H. Ceric, Ch. Hollauer, and S. Selberherr, "Microstructure and Stress Aspects of Electromigration Modeling", in Proc. Eight International Workshop on Stress Induced Phenomena in Metallization, pp. 17-23, Dresden, 2005.

- [19] J. Noguchi, T. Oshima, U. Tanaka K. Sasajima, H. Aoki, K. Sato, K. Ishikawa, T. Saito, K. Konishi, S. Hotta, S. Uno, and K. Kikushima, "Integration and Reliability Issues of Cu/SiOC Interconnect for ArF Node SoC Manufacturing, IEDM Tech.Dig., pp. 21.6.1-21.6.4, 2003

- [20] O. Aubel, "Ultrahochbeschleunigte Lebensdauertests an modernen Kupfer-Leiterbahnsystemen in höchstintegrierten Schaltungen, PhD Thesis, University Hannover, 2004.

- [21] H. Ceric, "Numerical Techniques in Modern TCAD", PhD Thesis, TU Wien, 2005.

## Acknowledgements

This work has been partly supported by the European Commission with the projects MULSIC, IST-2000-30133 and PROMENADE, IST-2002-2312.