# Optimizing the Performance of Carbon Nanotube Transistors

M. Pourfath, H. Kosina, and S. Selberherr Institute for Microelectronics, TU Wien Gußhausstraße 27–29/E360, A-1040 Wien, Austria

Phone: +43-1-58801/36014, Fax: +43-1-58801/36099, Email: Pourfath@iue.tuwien.ac.at

Abstract—A numerical study of carbon nanotube field effect transistors is presented. The non-equilibrium Green's function formalism was employed to investigate the static response. Based on the quasi-static approximation, the dynamic response has been determined. The effect of the gate-source and gate-drain spacers on the static and dynamic response of the device was studied. Simulation results suggest that both the dynamic and static characteristics of the device can be improved by appropriately designing the gate-source and gate-drain spacers.

#### I. Introduction

Exceptional electronic and mechanical properties together with nanoscale diameter make carbon nanotubes (CNTs) promising candidates for nanoscale field effect transistors (FETs). In short devices (less than 100 nm) carrier transport through the device is nearly ballistic [1,2]. We employed the Non-Equilibrium Green's Function (NEGF) formalism to study the static response of CNTFETs. The Quasi Static Approximation (QSA) was used to investigate the dynamic response of these devices.

Depending on the work function difference between the metal contact and the CNT, carriers at the metal-CNT interface encounter different barrier heights. Fabrication of devices with positive (Schottky type) [3] and zero (ohmic) [1] barrier heights for holes have been reported. Devices with positive barrier height have lower on-current and exhibit severe ambipolar behavior [4], while devices with zero barrier height show better performance both theoretically [5] and experimentally [2]. We consider in this work devices with zero ( $\Delta E_{Be} = 0 \text{ eV}$ ) barrier heights for electrons. The barrier height for holes is given by  $\Delta E_{\mathrm{Bh}} = E_{\mathrm{g}} - \Delta E_{\mathrm{Be}}$ . Since the dispersion relations for electrons and holes are the same, our discussions are valid for holes as well. In devices with positive barrier heights most carriers should tunnel through the source-sided barrier at the metal-CNT interface to reach the channel, while in devices with zero barrier height carrier are injected by thermionic emission. The gate voltage controls the current by modulating the transmission coefficient of carriers through the device [1]. However, unwanted ambipolar behavior can occur, which limits the static characteristics of the device by reducing the  $I_{\rm on}/I_{\rm off}$  ratio. We show that not only the ambipolar behavior and static characteristics, but also the dynamic characteristics of the device are improved by appropriately designing the gate-source and gate-drain spacers.

# II. APPROACH

In this section the models used to study the static and dynamic response of CNTFETs are explained.

# A. Static Response

Based on the NEGF formalism we studied the effect of device geometry on the performance of carbon nanotube field-effect transistors. We have solved the coupled system of transport and Poisson equations numerically. Due to quantum confinement along the tube circumference, carrier have bound wave functions around the CNT and can propagate along the tube axis. Under the assumption that the potential profile does not vary around the circumference of the CNT, sub-bands will be decoupled [6]. In this work we assume bias conditions for which the first sub-band contributes mostly to the total current. In the mode-space approach [6] the transport equation for each sub-band can be written as:

$$G^{R} = [EI - H - \Sigma^{R}]^{-1} \tag{1}$$

In (1) an effective mass Hamiltonian was assumed. All our calculations assume a CNT with band gap of  $E_{\rm g}=0.6~{\rm eV}$  corresponding to a CNT with a radius of  $R_{\rm CNT}=0.8~{\rm nm}$ , and  $m^*=0.05m_0$  for both electrons and holes. The total self-energy in (1) consists of the self-energies due to the source contact, drain contact, and electron-phonon interaction,  $\Sigma^R=\Sigma^R_{\rm S}+\Sigma^R_{\rm D}+\Sigma^R_{\rm el-ph}$  [7]. In this work we assumed ballistic transport through the device, and the self energy due to electron-phonon interaction is neglected. Considering the contribution of the source and drain contacts, the total carrier concentration is calculated as:

$$n = \int G^R \Gamma_{\rm S} G^A f(E - E_{\rm FS}) dE + \int G^R \Gamma_{\rm D} G^A f(E - E_{\rm FD}) dE$$

(2)

where,  $G^A = [G^R]^{\dagger}$  and  $\Gamma_{S,D} = i(\Sigma_{S,D} - \Sigma_{S,D}^{\dagger})$ . The carrier charge was taken into account as sheet charge distributed uniformly over the surface of the CNT [8].

The Landauer-Büttiker formula is used to calculate the current through the device:

$$I = \frac{4q}{h} \int [f(E - E_{FS}) - f(E - E_{FD})]TC(E)dE$$

(3)

where  $TC(E) = \text{tr}\{\Gamma_{\rm S}G^R\Gamma_{\rm D}G^A\}$  is the transmission coefficients of carriers.

The coupled system of transport and Poisson equation is solved iteratively. Details are presented in [7].

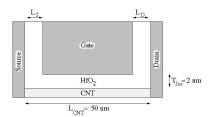

Fig. 1. Sketch of the device.  $T_{\mathrm{Ins}}=2$  nm,  $L_{\mathrm{CNT}}=50$  nm and  $\epsilon_{\mathrm{r}}=15$ .

# B. Dynamic Response

To investigate the dynamic response of the device we consider the device delay time defined as:

$$\tau = \frac{C_{\rm G} V_{\rm DD}}{I_{\rm on}} \tag{4}$$

Here,  $C_{\rm G} = C_{\rm GS} + C_{\rm GD} + C_{\rm GG}$  with  $C_{\rm GG}^{-1} = C_{\rm Ins}^{-1} + C_{\rm Q}^{-1}$ . The quantum capacitance is given by  $C_{\rm Q} = 8{\rm q}^2/{\rm h}\nu_{\rm F} \approx 400{\rm aF}/{\rm \mu m}$ , including the twofold band and spin degeneracy [9]. The insulator capacitance, occurring between the tube and a plane, is given by[10]:

$$C_{\rm Ins} = \frac{2\pi\epsilon}{\cosh^{-1}(T_{\rm Ins}/R_{\rm CNT} + 1)}$$

(5)

For the geometry parameters given in Fig. 1  $C_{\rm Ins} \approx 400 {\rm aF}/\mu{\rm m}$ . For a device with 50 nm channel length  $C_{\rm GG} \approx 10 {\rm aF}$ . To calculate the gate-source and gate-drain parasitic capacitances we assumed the capacitance of two parallel plates,  $C_{\rm GS,GD} = \epsilon A/L_{\rm S,D}$ , (see Fig. 1). Even with a small total area of  $A=200~{\rm nm}\times25~{\rm nm}$  and a large spacer width of  $L_{\rm GS,GD}=10~{\rm nm}$  the parasitic capacitances  $C_{\rm GS}+C_{\rm GD}\approx130~{\rm aF}$  are much bigger than  $C_{\rm GG}$ . As a result,  $C_{\rm G}\approx C_{\rm GS}+C_{\rm GD}=\epsilon A\{1/L_{\rm S}+1/L_{\rm D}\}$ . To normalize  $\tau$  we assumed  $A=1~{\rm nm}^2$ .

# III. THE EFFECT OF GEOMETRY ON THE DEVICE CHARACTERISTICS

In this section the effect of the spacer widths  $L_{\rm S}$  and  $L_{\rm D}$  on the static and dynamic response of CNTFETs is studied. For the static response the output and transfer characteristics are compared, and for the dynamic response the device delay

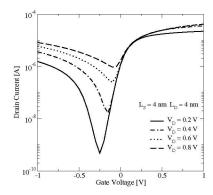

Fig. 2. Transfer characteristics at different drain biases.

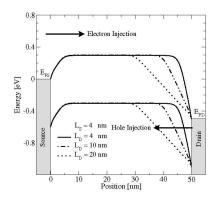

Fig. 3. The effect of  $L_D$  on the band-edge profiles of the device with  $\Delta E_{\rm Be}=0.0~{\rm eV}.~V_G=-0.5~V$  and  $V_D=0.5~V$ .

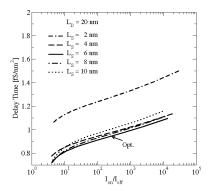

time versus the  $I_{\rm on}/I_{\rm off}$  ratio. The latter figure of merit can be used to compare devices with different geometries and material properties [11].

# A. The Effect of $L_D$ on the Device Characteristics

The transfer characteristics at different drain biases are shown in Fig. 2. In the off-regime (negative gate bias) the drain current of CNTFETs starts to increase, and by increasing the drain bias this phenomenon becomes more apparent [2, 12]. This effect is due to the ambipolar behavior of these devices, which can be well understood by considering the band edge profiles. As shown in Fig. 3, if the drain voltage becomes higher than the gate voltage, the barrier thickness for holes at the drain contact is reduced and the tunneling current of holes increases. At the minimum current points in Fig. 2, electrons and holes have the same contribution to the total current, whereas in other regions either the electron or hole contribution will dominate. By increasing  $L_{\rm D}$  the band edge profile near the drain contact is less affected by the gate voltage (Fig. 3). Therefore, when the voltage between the gate and drain contacts increases the barrier thickness for holes near the drain contact is less reduced, and as a result the tunneling current of holes is suppressed. Fig. 4 compares the transfer characteristics of devices with different  $L_{\rm D}$ . When increasing  $L_{\rm D}$ , the ambipolar behavior is suppressed and the off-current decreases, while the on-current remains nearly unchanged,

Fig. 4. The effect of  $L_{\mathrm{D}}$  on the transfer characteristics.

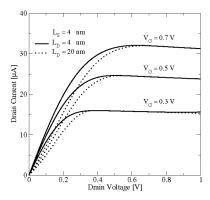

Fig. 5. Output characteristics at different gate biases for devices with  $L_{\rm D}=4~{\rm nm}$  and  $L_{\rm D}=20~{\rm nm}$ .  $L_{\rm S}=4~{\rm nm}$ .

such that the  $I_{\rm on}/I_{\rm off}$  ratio increases. The disadvantage of increasing  $L_{\rm D}$  is that at low drain biases electrons have to tunnel through a thicker barrier near the drain contact, resulting in a smaller drain current at low drain voltages (Fig. 5). This phenomenon is more apparent in devices with positive barrier heights for electrons at the drain-CNT interface [4,8].

In devices with positive barrier heights the ambipolar behavior is more apparent due to lower barrier height for holes. To avoid this problem, we have shown that a double gate structure can be used to strongly suppress the ambipolar behavior of such devices [4] without reducing the drain current at low drain biases. In a double gate device the carrier injection at the source and drain contacts is controlled separately. However, addition of a gate increases the parasitic capacitance.

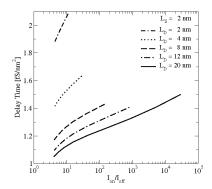

Increasing  $L_{\rm D}$  increases the  $I_{\rm on}/I_{\rm off}$  ratio, while the gate-drain parasitic capacitance decreases. As show in Fig. 6, increasing  $L_{\rm D}$  improves the device delay time versus  $I_{\rm on}/I_{\rm off}$  ratio by several orders of magnitude.

# B. The Effect of $L_S$ on the Device Characteristics

The band edge profile near the source contact plays an important role in controlling the total current. Increasing  $L_{\rm S}$  reduces the gate control of the band-edge profile near the source contact. Both the tunneling current and thermionic emission current contribute to the total current. Electrons with energies lower than the barrier height have to tunnel

Fig. 6. The effect of  $L_{\rm D}$  on the device delay time versus  $I_{\rm on}/I_{\rm off}$  ratios.

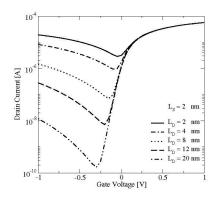

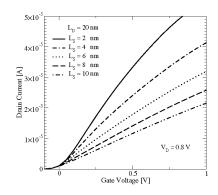

Fig. 7. The effect of  $L_{\rm S}$  on the transfer characteristics.  $L_{\rm D}=20~{

m nm}$  and  $V_{\rm D}=0.8~{

m V}$

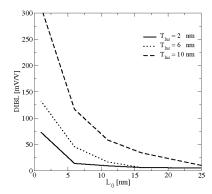

through the source-sided metal-CNT interface barrier to reach the channel while electrons with energies higher than the barrier height are injected by thermionic emission. Since the tunneling probability decreases exponentially with the barrier width the tunneling current decreases with increasing  $L_{\rm S}$ . But, the thermionic emission current is independent of the barrier width. Contribution of tunneling current decreases with decreasing barrier height, while that of the thermionic emission increases. However, even for devices with zero barrier height the mentioned sensitivity is not negligible due to the contribution of the tunneling current from states below the Fermi level. Since at positive gate biases the conduction band-edge is pushed below the source Fermi level, even in devices with zero barrier height the tunneling current can contribute to the total current. For thiner insulators the width of the sourcesided barrier decreases, resulting in a higher tunneling current contribution to the total current and a higher sensitivity of the on-current to  $L_{\rm S}$  Fig. 8.

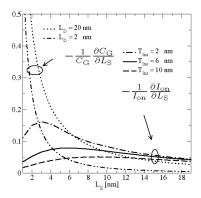

When increasing  $L_{\rm S}$ , the gate-source parasitic capacitance is reduced, and so is the on-current. Since  $\tau$  is proportional to the parasitic capacitance and inversely proportional to the oncurrent (4), there is an optimal value for  $L_{\rm S}$ , which minimizes au. It can be easily shown that the optimal value  $L_{S0}$ , where  $\frac{\partial \tau}{\partial L_S}|_{L_{S0}}=0$ , is achieved when  $\frac{1}{C_G}\frac{\partial C_G}{\partial L_S}|_{L_{S0}}=\frac{1}{I_{on}}\frac{\partial I_{on}}{\partial L_S}|_{L_{S0}}.$  Considering the expression derived for  $C_G$  in Section II.B, we have  $\frac{1}{C_G}\frac{\partial C_G}{\partial L_S}=\frac{1}{L_S(1+L_S/L_D)}$ . Fig. 8 compares the optimal  $L_S$  for devices with different barrier height,  $T_{Ins}$  and  $L_D$ . In devices with zero barrier height the on-current is less sensitive to  $L_{\rm S}$ , resulting in a large, optimal spacer width ( $L_{\rm S} \approx 6~{

m nm}$ at  $T_{\rm Ins}=2~{

m nm}$  and  $L_{

m D}=20~{

m nm}$ ). With the increase of the barrier height the sensitivity of the on-current to  $L_{\rm S}$  increases and optimal spacer widths become smaller ( $L_{\rm S} \approx 3-4~{

m nm}$  at  $T_{\rm Ins}=2~{\rm nm}$  and  $L_{\rm D}=20~{\rm nm}$ ). As shown in Fig. 9 the optimal value of  $L_{\rm S}$  for the given material and geometrical parameters results in optimized device characteristics. Note that the optimal value for  $L_{\rm S}$  depends on  $L_{\rm D}$ . For small values of  $L_{\rm D}$  the gate-drain parasitic capacitance dominate the gatesource parasitic capacitance, therefore further decrease of  $L_{

m S}$ does not improve the delay time.

Fig. 8. The sensitivity of the parasitic capacitance and the on-current to  $L_{\rm S}$  for different insulator thicknesses. The intersection of the curves gives the optimal  $L_{\rm S}$ , which minimizes  $\tau$ .

#### IV. DISCUSSIONS

We showed that an appropriate selection of  $L_{\rm S}$  and  $L_{\rm D}$  improves both the static and dynamic response of the device. The results are based on two assumptions, namely that a) parasitic capacitances dominate quantum and insulator capacitances and b) transport is ballistic. As discussed in Section II.B, for most parameter values parasitic capacitances dominate quantum and insulator capacitances. However, if this condition is not satisfied the total capacitance would not be decreased by a further increase of the spacer width. The assumption of ballistic transport is theoretically justified for the short devices considered in this work [13, 14]. Experimental results indicate that short channel CNTFETs, with channel lengths less than several hundred nanometer, can operate close to the ballistic limit [2].

To avoid drain induced barrier lowering (DIBL), the length of the gate contact  $L_{\rm G}$  should not be too short. Fig. 10 shows that for  $L_{\rm G}>20$  nm the DIBL effect is not important. In devices with thin insulators the insulator capacitance can be larger than the quantum capacitance, such that  $C_{\rm G}\approx C_{\rm Q}$ . Under this condition the gate has good control over the channel. Therefore, with decreasing insulator thickness, the DIBL effect reduces. For very small gate-lengths ( $\approx 2$  nm) observation of Coulomb blockade effects has been reported [15]. However, in

Fig. 9. The effect of  $L_{\rm S}$  on the device delay time versus  $I_{\rm on}/I_{\rm off}$  ratios.  $L_{\rm D}=20$  nm and  $V_{\rm DD}=0.8$  V. The optimal  $L_{\rm S}$  is shown.

Fig. 10. The effect of  $L_{\rm G}$  on the DIBL effect.

this work we assumed gate lengths in the range 20 - 40nm, so that Coulomb blockade is not important.

As discussed in [16], the QSA is valid for frequencies below 4 THz. Therefore, as long as the calculated delay time is above the pS range for the given geometry the QSA approximation remains valid.

### V. CONCLUSION

We showed that both the static and dynamic responses of CNTFETs can be improved by appropriately designing the gate-source and gate-drain spacers. We showed that increasing the gate-drain spacer suppresses the ambipolar behavior and reduces the gate-drain parasitic capacitance. When increasing the gate-source spacer, both the on-current and the gate-source parasitic capacitance are decreased, which implies that the device delay time can be optimized for given geometrical and material parameters. Our discussions are based on the assumption that carrier transport in the device is ballistic and that parasitic capacitances dominate the quantum and insulator capacitances.

#### ACKNOWLEDGMENT

This work was partly supported by the European Commission, contract No. 506844 (NoE SINANO), and the National Program for Tera-level Nano-devices of the Korea Ministry of Science and Technology as one of the 21st Century Frontier Programs.

# REFERENCES

- [1] A. Javey et al., Letters to Nature 424, 654 (2003).

- [2] A. Javey et al., Nano Lett. 4, 1319 (2004).

- [3] J. Appenzeller et al., Phys.Rev.Lett. 92, 048301 (2004).

- [4] M. Pourfath et al., J.Appl.Phys. 97, 1061031 (2005).

- [5] J. Guo et al., IEEE Trans. Electron Devices 51, 172 (2004).

- [6] R. Venugopal et al., J.Appl.Phys. 92, 3730 (2002).

- [7] M. Pourfath et al., Lecture Notes in Computer Science 3743, 578 (2006).

- [8] M. Pourfath et al., Microelectronic Engineering 81, 428.

- [9] D. John et al., J.Appl.Phys. 96, 5180 (2004).

- [10] P. Burke, IEEE Trans. Nanotechnology 2, 55 (2003).

- [11] J. Guo et al., in IEDM Tech.Dig. 703 (2004)

- [12] M. Radosavljevic et al., Appl.Phys.Lett. 83, 2435 (2003).

- [13] J. Guo et al., Appl.Phys.Lett. 86, 193103 (2005).

- [14] J. Guo, J.Appl.Phys. 98, 063519 (2005).

- [15] K. Alam et al., Appl.Phys.Lett. 87, 073104 (2005).

- [16] J. Guo et al., IEEE Trans. Nanotechnology 4, 715 (2005).