## Planarization of Silicon Dioxide and Silicon Nitride Passivation Layers

A. Sheikholeslami <sup>(1)</sup>, F. Parhami <sup>(2)</sup>, H. Puchner <sup>(2)</sup>, S. Selberherr <sup>(1)</sup>TU Vienna (Vienna, AT); <sup>(2)</sup>Cypress Semiconductor Corporation (San Jose, US) sheikholeslami@iue.tuwien.ac.at

Technologies for image sensor processes are sensitive to passivation planarization which serves to prevent clear layer coating issues and to shorten the optical path between color filter and sensor surface. A typical passivation stack in integrated circuits (IC) chips is a layer of SiO2 from plasma enhanced chemical vapor deposition (PECVD) in a Tetraethoxysilane (TEOS) process covered by a layer of PECVD SisN4.

The goal of our investigations was to achieve planarized passivation of moisture barrier and the topmost metal layer. Planarization of a moisture seal  $Si_3N_4$  layer can be obtained by optimizing the trench width and taking advantage of the breadloafing characteristic of a PECVD process. Planarization of a TEOS process on the top metal layer can be achieved by depositing a thick layer of silicon dioxide from TEOS followed by chemical mechanical planarization (CMP) which polishes down the passivation layer to a desired thickness.

The optimization of the above mentioned processes requires a topography simulator for predicting profiles of the deposition steps. Our topography simulator called enhanced level set applications (ELSA) is based on a level set technique for tracking moving boundaries. ELSA has been used as a general purpose two- and three-dimensional topography simulator for different semiconductor manufacturing processes [1-3].

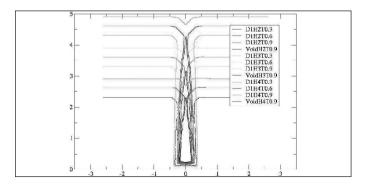

Using ELSA the trench width and height was optimized during the deposition of passivation layer followed by CMP. The optimized parameters guarantee a sufficient planarization margin larger than the CMP. The planarization margin is defined as the distance between the top of the void or the bottom of the oxide dimple (when no void forms) to 0.3 micro meter above the trench. Figure 1 shows a typical example of our investigations, where D (1 micro meter), H, and T stand for trench width, trench height, and the thickness of the passivation layer. H and T are varied from 2 to 4 micro meters, and from 0.3 to 0.9 micro meters bottom-up, respectively.

[1] C. Heitzinger, A. Sheikholeslami, F. Badrieh, H. Puchner, and S. Selberherr, "Feature-scale process simulation and accurate capacitance extraction for the backend of a 100-nm aluminium/teos process," IEEE Trans. Electron Devices, vol. 51, no. 7, pp. 1129-1134, 2004. [2] A. Sheikholeslami, S. Holzer, C. Heitzinger, M. Leicht, O. Haeberlen, J. Fugger, T. Grasser, and S. Selberherr, "Inverse modeling of oxid deposition using measurements of a teos cvd process," in Proc. PhD Research in Microelctronics and Electronics (PRIME), Vol. 2, Lausanne, Switzerland, 2005, pp. 279-282.

[3] A. Sheikholeslami, F. Parhami, R. Heinzl, E. Al-Ani, C. Heitzinger, F. Badrieh, H. Puchner, T. Grasser, and S. Selberherr, "Applications of three-dimensional topography simulation in the design of interconnect lines," in Proc. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Tokyo, Japan, 2005, pp. 187-190.