# Orientation Dependence of the Low Field Mobility in Double- and Single-gate SOI FETs

Viktor Sverdlov, Enzo Ungersboeck, Hans Kosina, and Siegfried Selberherr

Institute for Microelectronics, Technische Universität Wien

Gusshausstrasse 27–29, A-1040 Vienna, Austria

Email: {sverdlov, ungersboeck, kosina, selberherr}@iue.tuwien.ac.at

Abstract—The low field mobility in double- and single-gate structures is analyzed for (100) and (110) SOI substrate orientation. Due to volume inversion, mobility in double-gate ultrathin body (110) SOI FETs is enhanced in comparison with the mobility of single-gate structures in the whole effective field range. In double-gate (100) structures the mobility decreases below the single-gate value for high effective fields. It is argued that the twice as high carrier concentration in double-gate FETs causes significant occupation of higher subbands, where mobility is low, and that additional intersubband scattering channels for the lowest subband are opened. These effects partly compensate the mobility enhancement due to volume inversion and lead to a mobility decrease in double-gate (100) structures.

#### I. INTRODUCTION

Due to aggressive downscaling of transistor feature-size the role of parasitic short-channel effects in bulk MOSFETs is rapidly increasing, prompting for an introduction of alternative MOSFET architectures. Double-gate (DG) silicon-on-insulator (SOI) transistors with ultra-thin Si body (UTB) are considered to be good candidates for the far-end ITRS roadmap scaling [1]. Excellent electrostatic channel control in DG operation is theoretically predicted and allows scaling of the MOSFET's channel length down to 2.5 nm [2], maintaining reasonable subthreshold slope, satisfactory DIBL, and acceptable gain. Contrary to the bulk MOSFET, the UTB SOI FET channel must be intrinsic in order to avoid strong fluctuations of device characteristics due to the sensitivity to the random dopant positions.

Absence of impurity scattering increases the mobility. At the same time important scattering mechanisms limiting the carrier mobility, such as electron-phonon interaction [3], [4], surface roughness scattering [5], [6], Si body thickness fluctuations [7], scattering with interface charges, and remote Coulomb scattering with impurities in the poly-gate [8], [9] have been a subject of recent theoretical and experimental studies. Despite the extensive experimental data avaliable on mobility behavior in UTB SOI FET in DG and single-gate (SG) operation mode as well as the vast number of simulations for either SG or DG structures, a comparative theoretical analysis of mobility behavior in SG and DG FETs is limited to a few publications dealing exclusively with (100) SOI orientation [10], [11]. Such an analysis is desirable due to an existing discrepancy between the mobility measurements and theoretical predictions for (100) UTB SOI FETs. At high

This research was supported by the Austrian Science Fund FWF, project P17285-N02, and by the European Commission, project SINANO IST-506844

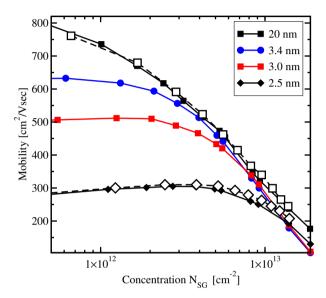

Fig. 1. Mobility simulations for SG (100) SOI FETs (filled symbols). Results are in good agreement with those reported previously [6] (open symbols).

effective fields the mobility measured in DG structures is smaller than the SG mobility [7], although an enhancement due to bulk inversion would be anticipated [12]. However, it was recently confirmed experimentally [13], that in (110) UTB FETs the DG mobility is higher than the SG mobility. In order to explain the observed controversy it becomes necessary to theoretically compare the mobility behavior in SG and DG structures for different body orientations.

In this work we carry out a study of the mobility in SG and DG SOI FETs for different substrate orientations. A Monte Carlo algorithm is used which incorporates degeneracy effects *exactly* in the limit of vanishing driving fields and is valid for arbitrary scattering mechanisms and for general band structure [14]. We demonstrate that the doubled carrier concentration in DG structures leads to higher occupation of subbands with low mobilities and increases intersubband scattering in (100) UTB SOI FETs. These effects compensate the mobility enhancement due to volume inversion.

## II. SIMULATION RESULTS

The transport calculations have accounted for electronphonon interaction [3] and surface roughness scattering, which are the dominant mechanisms determining the mobility in the region of high effective fields. This captures the main difference of the mobility behavior in DG and SG structures at high

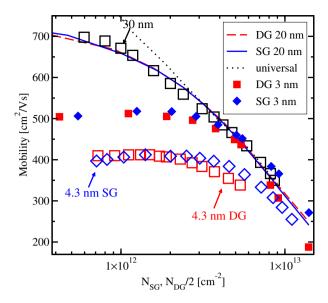

Fig. 2. Mobility for (100) UTB FETs. Mobility is plotted as a function of concentration for the SG structure and as a function of half of the concentration for the DG structure. Mobilities for the 20 nm thick SG and DG structures are in good agreement with experimental data for a thick Si body FET [13]. Mobility in the DG UTB structure is smaller than that in the SG structure at high concentration, which is in qualitative agreement with the experimental data [7] for the 4.3 nm thick UTB FETs and in contrast to the bulk inversion concept [12].

concentrations for different orientations, as we demonstrate below. Coulomb scattering, which is important at small  $N_s$ , and additional mechanisms such as interaction with surface optical phonons and scattering on fluctuations of  $\delta T_{SOI}$  [15] should be included to reproduce the mobility in the whole concentration range. The introduction of acoustic phonon confinement relevant to UTB SOI structures may also improve agreement with the experimental data [16]. We use the Prange and Nee formulation [6], [17] for surface roughness scattering. The correlation function is assumed to be of Gaussian shape

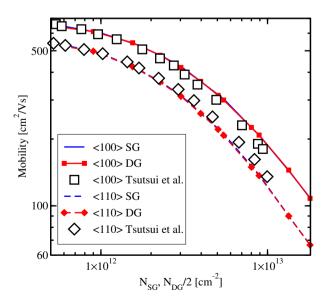

Fig. 3. Low-field mobility in different directions calculated for 20 nm (110) SG and DG structures (filled symbols) closely follows experimental data [13] (open symbols).

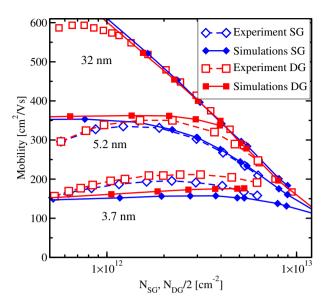

Fig. 4. Mobility comparison between SG and DG structures for (110) UTB SOI FETs, in  $\langle 1\bar{1}0 \rangle$  direction. Mobility is piloted as function of concentration for SG structures and as function of half the concentration for DG structures. DG (110) SOI FET mobility is higher than the one of SG structures in the whole range of concentrations, in good agreement with the experimental data [13], supporting the bulk inversion concept [12].

and equal at the two interfaces. Surface roughness is assumed to be uncorrelated at the opposite interfaces. Static dielectric screening is taken into account.

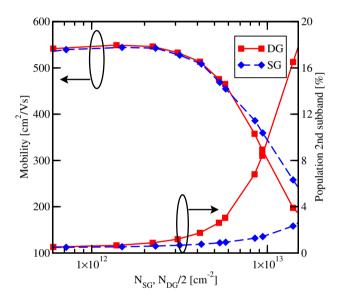

In Fig. 1 we compare the results of mobility simulations against data avaliable in the literature [6]. Our simulations are in good agreement with previous calculations for 20 nm and 2.5 nm thick (100) SOI FETs, assuming similar surface roughness scattering parameters. Using calibrated parameters, mobilities of SG and DG (100) structures for different Si body thicknesses are compared in Fig. 2. For a 20 nm thick Si body the two inversion layers formed at the opposite interfaces of DG structure are well separated and independent. The DG FET mobility plotted as a function of the concentration per single channel is in good agreement with the results for a SG structure. Both curves are in reasonable agreement with experimental data for 30 nm thick Si body FET [13], which reproduces the universal mobility curve [18] at high  $N_s$ . For 3 nm Si thickness the DG mobility, plotted as a function of  $N_s/2$ , tends to be slightly higher at small effective fields. For high  $N_s$  the DG mobility for (100) orientation becomes lower than the SG mobility. This is in qualitative agreement with experimental data, also shown in Fig. 2 with open symbols. This behavior, however, contradicts the volume inversion concept [12]. According to this concept carriers are located in the center of the Si body in volume inversion and are further away from the interfaces. Due to reduced surface roughness scattering the mobility in a DG structure is expected to be higher than the mobility in a SG structure.

Now we turn our attention to (110) SOI FETs. For (110) orientation the subband structure consists of a 4-fold and a 2-fold degenerate subband ladder. Subbands in both ladders are anisotropic. Simulation results for 20 nm SG and DG structures are shown in Fig. 3. The results for SG and DG structures

plotted as a function of the concentration per inversion layer are in good agreement with each other and with experimental data [13]. Due to the high anisotropy of the subbands of each ladder the surface mobility is anisotropic. Diagonal values of the mobility tensor along  $\langle 001 \rangle$  and  $\langle 1\overline{1}0 \rangle$  directions are in agreement with those observed experimentally [13].

Fig. 4 shows results of mobility simulations in  $\langle 1\overline{1}0 \rangle$  direction performed for several Si body thicknesses using the same scattering parameters as for thick Si films. The mobility of (110) SOI FETs coincides reasonably well with the experimental data [13] shown in Fig. 4. The mobility for UTB (110) DG structures is higher than the mobility of (110) SG structures in the whole concentration range. This is consistent with recent experimental studies [13] and confirms the concept of the mobility enhancement in DG SOI FET due to volume inversion [12]. The results for (110) FET mobilities are in sharp contrast with the data for mobilities in (100) FETs.

## III. VOLUME INVERSION IN (110) AND (100) SOI FETS

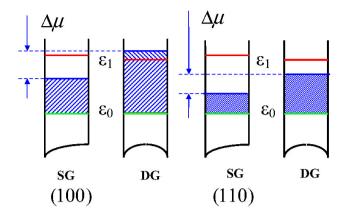

The diverse mobility behavior in (100) and (110) DG structures was attributed to the difference in energy splitting between 2- and 4-fold degenerate subband ladders in SG and DG structures [13]. It was argued [13] that in (100) DG SOI FETs the intersubband energy splitting is smaller than in (100) SG structures, whereas in (110) SG and DG structures the splitting is similar. Smaller intersubband splitting leads to higher occupation of primed subbands with low mobility in the (100) DG structure, which reduces the total mobility in DG structures more significantly than in SG structures. Although this argumentation seems plausible, and the mechanism discussed is present, our estimations show that this cannot solely be responsible for a significant increase of the occupancy of primed subbands.

In UTB FETs the subband structure is mainly determined by strong geometrical confinement. So the subband structure will be quite similar in the DG and SG structures. The SG and DG mobilities are compared as a function of the concentration per single inversion layer. Because of two inversion layers formed at both interfaces in a DG FET, the total concentration in a DG structure is twice as high as in a SG structure for the same gate voltage. It is due to this double concentration that the occupation of the primed subbands turns out to be higher in DG structures.

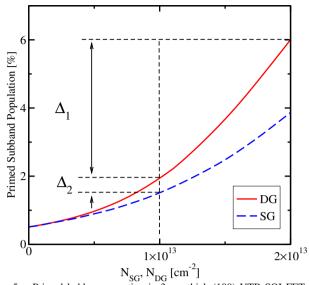

Fig. 5 shows the occupation of the primed subband ladder as a function of the total concentration in SG and DG structures. It reveals the relative contribution of two mechanisms to the increase of relative occupancy of primed subbands. The contribution  $\Delta_2$  computed at the same total concentration is due to the difference in energy splitting between primed and unprimed ladders and corresponds to the mechanism proposed in [13]. This contribution plays a minor role as compared to the increase  $\Delta_1$  of the primed subband occupation due to the doubled carrier concentration in DG structures for similar gate voltages.

It turns out that the same arguments lead to similar conclusions for (110) SOI FETs where the occupation of primed subbands increases rapidly in DG structures at high effective

Fig. 5. Primed ladder occupation in 3 nm thick (100) UTB SOI FET as a function of total concentration for either SG or DG operation mode. Higher primed ladder occupation in DG SOI FET is mainly due to the  $\Delta_1$  contribution resulting from twice-as-high carrier concentration in DG as compared to SG SOI FETs, for similar gate voltage. Contribution  $\Delta_2$  due to subband structure difference [13] is small.

fields. This should lead to a more rapid decrease of DG mobility in (110) FETs. This conclusion, however, contradicts experimental data and the results of simulations. Higher occupancy of primed subbands in DG structures is present in both (100) and (110) SOI FETs and cannot be the only reason responsible for the mobility lowering observed in DG (100) structures.

Due to different quantization masses, the subband structures in (100) and (110) SOI FETs differ significantly. In (100) SOI FETs the subband energy of the second unprimed subband is nearly equal to the energy of the first primed subband, while in (110) FETs the first unprimed 4-fold degenerate subband lies significantly higher than the lowest primed subband. Even though the occupation of primed subbands increases for both (100) and (110) orientations with increasing effective field, higher unprimed subbands remain virtually unpopulated in (110) UTB FETs. On the contrary, the occupation of higher unprimed subbands increases rapidly in DG (100) FETs for high effective fields. Fig. 6 illustrates the higher unprimed subband occupation in (100) compared to (110) DG FETs.

Fig. 7 shows a strong correlation between the rapid mobility degradation and the occupation increase of the higher unprimed subbands in a (100) DG structure. Since the mobility in higher subbands is significantly lower than the one in the lowest subband, occupation of the higher unprimed subband is responsible for the sharp mobility decrease in DG (100) FETs in the volume inversion regime. However, estimations show that the fraction of carriers occupying the higher subbands is not sufficient to cause such a significant drop in the DG (100) FET mobility. A more substantial correction comes from the mobility lowering in the ground subband itself. Since the higher unprimed subband is occupied in (100) DG structures, an extra channel of scattering between the first lowest and the second unprimed subband opens. This mechanism plays

Fig. 6. Illustration of higher unprimed subband occupation in (100) and (110) UTB SOI FETs. Contrary to (110) SOI FETs, the higher unprimed subbands are occupied significantly in DG (100), for similar concentrations, due to a heavier quantization mass and a lighter in-plane density-of-states mass.

Fig. 7. Correlation between mobility degradation and occupation of higher unprimed subbands in a 3 nm thick DG (100) SOI FET.

a significant role in the (100) DG mobility lowering: If we switch off the intersubband scattering in the simulations, thus forbidding the scattering between the lowest and higher unprimed subbands, the DG mobility exceeds the corresponding (100) SG mobility, even at high carrier concentrations, in compliance with the volume inversion concept.

## IV. CONCLUSION

The mobility in double- and single-gate ultra-thin body FETs for different Si orientations was investigated. Our method is based on the solution of the linearized Boltzmann equation and allows the exact treatment of the Pauli exclusion principle in the limit of vanishing driving fields. This method is valid for arbitrary scattering rates and includes realistic band structures. The results are in good agreement with experimental data for (110) UTB FETs, confirming the mobility enhancement in DG operation mode over the SG operation mode due to volume inversion. It is shown that two

effects compensate the volume inversion induced mobility enhancement in (100) DG structures. These effects are a significant occupation of higher subbands in the unprimed ladder as well as an extra channel of intersubband scattering, which decreases the mobility in the lowest subband of DG (100) FETs. Due to different quantization masses, these effects are absent in (110) UTB FETs.

#### REFERENCES

- K. K. Likharev, "Sub-20-nm Electron Devices," in Advanced Semiconductor and Organic Nano-Techniques, H. Morkoc, Ed. New York: Academic Press, 2003, pp. 239–302.

- [2] V. Sverdlov, T. Walls, and K. Likharev, "Nanoscale Silicon MOSFETs: A Theoretical Study," *IEEE Trans. Electron Devices*, vol. 50, no. 9, pp. 1926–1933, 2003.

- [3] C. Jacoboni and L. Reggiani, "The Monte Carlo Method for the Solution of Charge Transport in Semiconductors with Applications to Covalent Materials," *Reviews of Modern Physics*, vol. 55, no. 3, pp. 645–705, 1083

- [4] M. Lundstrom, Fundamentals of Carrier Transport. Cambridge Cambridge University Press, 2000.

- [5] M. V. Fischetti, Z. Ren, P. M. Solomon, M. Yang, and K. Rim, "Six-Band K.P Calculation of the Hole Mobility in Silicon Inversion Layers: Dependence on Surface Orientation, Strain, and Silicon Thickness," *J.Appl.Phys.*, vol. 94, no. 2, pp. 1079–1095, 2003.

- [6] D. Esseni, "On the Modeling of Surface Roughness Limited Mobility in SOI MOSFETs and Its Correlation to the Transistor Effective Field," *IEEE Trans. Electron Devices*, vol. 51, no. 3, pp. 394–401, 2004.

- [7] K. Uchida, J. Koga, and S. Takagi, "Experimental Study on Carrier Transport Mechanisms in Double- and Single-Gate Ultrathin-Body MOSFETs Coulomb Scattering, Volume Inversion, and  $\delta T_{SOI}$ -induced Scattering," in *IEDM Techn. Dig.*, 2003, pp. 805–808.

- [8] F. Gámiz, J. B. Roldán, J. E. Carceller, and P. Cartujo, "Monte Carlo Simulation of Remote-Coulomb-Scattering-Limited Mobility in Metal-Oxide-Semiconductor Transistors," *Appl.Phys.Lett.*, vol. 82, no. 19, pp. 3251–3253, 2003.

- [9] D. Esseni and A. Abramo, "Modeling of Electron Mobility Degradation by Remote Coulomb Scattering in Ultrathin Oxide MOSFETs," *IEEE Trans. Electron Devices*, vol. 50, no. 7, pp. 1665–1675, 2003.

- [10] F. Gámiz, J. B. Roldán, A. Godoy, P. Cartujo-Cassinello, and J. E. Carceller, "Electron Mobility in Double Gate Silicon on Insulator Transistors: Symmetric-Gate versus Asymmetric-Gate Configuration," *J.Appl.Phys.*, vol. 94, no. 9, pp. 5732–5741, 2003.

- [11] D. Esseni, A. Abramo, L. Selmi, and E. Sangiorgi, "Physically Based Modeling of Low Field Electron Mobility in Ultrathin Single- and Double-Gate SOI n-MOSFETs," *IEEE Trans. Electron Devices*, vol. 50, no. 12, pp. 2445–2455, 2003.

- [12] F. Balestra, S. Cristoloveanu, M. Benachir, J. Brini, and T. Elewa, "Double-Gate Silicon-on-Insulator Transistor with Volume Inversion: a New Device with Greatly Enhanced Performance," *IEEE Electron Device Lett.*, vol. 8, no. 9, pp. 410–412, 1987.

- [13] G. Tsutsui, M. Saitoh, T. Saraya, T. Nagumo, and T. Hiramoto, "Mobility Enhancement due to Volume Inversion in (110)-oriented Ultra-Thin Body Double-Gate nMOSFETs with Body Thickness less than 5 nm," in *IEDM Techn. Dig.*, 2005, pp. 747–750.

- [14] S. Smirnov, H. Kosina, M. Nedjalkov, and S. Selberherr, "Monte Carlo Method for Modeling of Small Signal Response Including the Pauli Exclusion Principle," *J.Appl.Phys.*, vol. 94, no. 9, pp. 5791–5799, 2003.

- [15] D. Esseni and A. Abramo, "Mobility Modeling of SOI MOSFETs," Semicond. Sci. Technol., vol. 19, pp. S67–S70, 2004.

- [16] L. Donetti, F. Gámiz, N. Rodriguez, F. Jamenez, and C. Sampedro, "Influence of Acoustic Phonon Confinement on Electron Mobility in Ultrathin Silicon on Insulator Layers," *Appl. Phys. Lett.*, vol. 88, no. 1, pp. 122108–(1–3), 2006.

- [17] R. E. Prange and T. W. Nee, "Quantum Spectroscopy of the Low-Field Oscillations in the Surface Impedance," *Physical Review*, vol. 168, no. 3, pp. 779–786, 1968.

- [18] S. I. Takagi, A. Toriumi, M. Iwase, and H. Tango, "On the Universality of Inversion Layer Mobility in Si MOSFET's: Part I - Effects of Substrate Impurity Concentration," *IEEE Trans. Electron Devices*, vol. 41, no. 12, pp. 2357–2362, 1994.