# ECS Transactions, 3 (3) 299-308 (2006) 10.1149/1.2355721, copyright The Electrochemical Society

## Numerical Analysis of Gate Stacks

M. Karner, S. Holzer, W. Goes, M. Vasicek,

M. Wagner, H. Kosina, and S. Selberherr

Institute for Microelectronics

Technische Universität Wien

Gußhausstraße 27–29, 1040 Wien, Austria

An efficient software tool for investigations on novel stacked gate dielectrics with emphasis on reliability has been developed. The accumulation, depletion, and inversion of carriers in MOS capacitors is properly considered for n- and p-substrates. The effect of carrier quantization on the electrostatics and the leakage current is included by treating carriers in quasi-bound states (QBS) and continuum states. The effect of interface traps and bulk traps in arbitrarily stacked gate dielectrics is taken into account. Trap assisted tunneling (TAT) is incorporated assuming an inelastic single step tunneling process. A brief overview of implemented models is given. The capabilities of our tool are demonstrated by several examples.

## Introduction

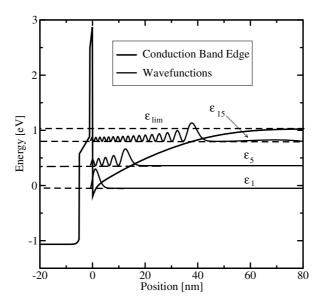

In order to enable further device down-scaling to the decananometer channel length regime numerous technological innovations including material and process changes such as high- $\kappa$  gate dielectrics and metal gate electrodes, are currently investigated (1). For future CMOS devices the use of high- $\kappa$  gate dielectrics provides an option to keep the gate leakage current within tolerable limits while retaining a good control over the inversion charge (2). Gate stacks consisting of layers of high- $\kappa$  dielectrics such as Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, Ta<sub>2</sub>O<sub>5</sub>, HfO<sub>2</sub>, or ZrO<sub>2</sub> have been suggested. The relevant parameter values for these materials reported in (3)-(9) are summarized in Tab. I. The different conduction band offsets of a SiO<sub>2</sub>/HfO<sub>2</sub> gate stack can be seen in Fig. 1. To overcome the technological problems, further theoretical and experimental research including the use of computer simulation is needed. We present a software tool, the Vienna Schrödinger Poisson solver (VSP), for the numerical analysis of novel gate stacks (10).

The software is written in C++ using state-of-the-art software design techniques. VSP offers a graphical user interface, as well as an XML based interface. Furthermore, VSP has an open software application interface (API) for integration into third party simulation environments. These features are mandatory for tasks such as parameter

Table I: Permittivity, band gap, and conduction band offset of gate stack materials.

|                                 | Permittivity          | Band gap                                    | Band offset                   |

|---------------------------------|-----------------------|---------------------------------------------|-------------------------------|

|                                 | $\kappa/\kappa_0$ [1] | $\mathcal{E}_{\mathrm{g}} \; [\mathrm{eV}]$ | $\Delta \mathcal{E}_{C} [eV]$ |

| $SiO_2$                         | 3.9                   | 8.9 - 9.0                                   | 3.0 - 3.5                     |

| $\mathrm{Si}_{3}\mathrm{N}_{4}$ | 7.0 - 7.9             | 5.0 - 5.3                                   | 2.0 - 2.4                     |

| $Al_2O_3$                       | 7.9 - 12.0            | 5.6 - 9.0                                   | 2.78 - 3.5                    |

| $ZrO_2$                         | 12.0 - 25.0           | 5.0 - 7.8                                   | 1.4 - 2.5                     |

| $HfO_2$                         | 16.0 - 40.0           | 4.5 - 6.0                                   | 1.5                           |

| $Ta_2O_5$                       | 23.0 - 26.0           | 4.4 - 4.5                                   | 0.3 - 1.5                     |

| ${ m TiO}_2$                    | 39.0 - 170.0          | 3.0 - 3.5                                   | 0.0 - 1.2                     |

Fig. 1: The conduction band edge of an NMOS inversion layer with a stacked gate dielectric. A potential potential well with a finite height  $\mathcal{E}_{\text{lim}}$  forms. The wavefunctions and the energy levels of three quasi-bound states are shown.

identification and model calibration, for example, for CV-characteristics and gate stack optimizations. Binaries are available for Linux, Windows, IBM AIX, and MacOs on request.

#### The Models

This section briefly describes the models implemented in the Schrödinger Poisson (S/P) solver. The chosen software architecture allows new models to be added easily. VSP is a quantum mechanical solver for closed as well as open boundary problems. The thereby calculated carrier concentration is used in the Poisson equation in a self consistent manner. Quantization effects can be treated in both, in the Si substrate and in the poly-Si gate.

## The Poisson Model

The Poisson equation describes the relation between the electrostatic potential  $\varphi$  and the space charge  $\rho$ .

$$\nabla \cdot (\varepsilon \nabla \varphi) + \rho(\varphi) = 0 \tag{1}$$

Hence, for S/P calculations a system of coupled partial differential equations (PDE) has to be solved self-consistently. We use an iterative predictor corrector scheme (11) in order to achieve a fast and stable convergence behavior. For each iteration step i, a linearized Poisson equation has to be solved:

$$\nabla \cdot (\varepsilon \nabla \varphi^i) + \varphi^i \frac{\partial \rho}{\partial \varphi} \Big|_{\varphi^{i-1}} = -\rho(\varphi^{i-1}). \tag{2}$$

## Effective Mass Approach

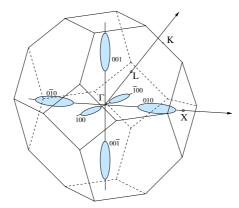

The band structure for electrons and holes is given by an arbitrary number of valley sorts, defined by an anisotropic effective mass and a band edge energy (12) (see Fig. 2). In this way a wide range of materials can be treated. Also, the effects of substrate orientation and strain on the band structure can be taken into account.

## Closed System Carrier Density

The energy levels  $\mathcal{E}_n$  and the wave functions  $\Psi_n$  of bound states within a quantum well follow from the effective mass Schrödinger equation:

$$\left(-\frac{\hbar^2}{2}\frac{\partial}{\partial x}\frac{1}{m(x)}\frac{\partial}{\partial x} + V(x)\right)\Psi(x) = \mathcal{E}\Psi(x).$$

[3]

For a well with a finite barrier height  $\mathcal{E}_{lim}$  (e.g. for a MOS inversion layer shown in Fig. 1), the occupation of the subband states is considered up to this energy. The

Fig. 2: Equi-energy surfaces of the first conduction band of unstrained Silicon. VSP treats the conduction band as three valleys having the same minimum energy but different orientations of the effective mass tensor.

electron density is given by the effective DOS of a two-dimensional electron gas  $N_{\text{C,2D}}$  and the incomplete Fermi function  $\mathcal{F}_0(x,b)$  as follows.

$$n_{\mathrm{C,2D}}(x) = N_{\mathrm{C,2D}} \sum_n |\Psi_n(x)|^2 \times \left(\mathcal{F}_0\left(\frac{\mathcal{E}_{\mathrm{F}} - \mathcal{E}_n}{\mathrm{k_B}T}, 0\right) - \mathcal{F}_0\left(\frac{\mathcal{E}_{\mathrm{c}} - \mathcal{E}_{\mathrm{F}}}{\mathrm{k_B}T}, \frac{\mathcal{E}_{\mathrm{c}} - \mathcal{E}_{\mathrm{lim}}}{\mathrm{k_B}T}\right)\right) [4]$$

Starting at  $\mathcal{E}_{lim}$ , a continuum of states is assumed, carrying the electron density

$$n_{\mathrm{C,3D}}(x) = N_{\mathrm{C,3D}} \mathcal{F}_{\mathrm{1/2}} \left( -\frac{\mathcal{E}_{\mathrm{c}} - \mathcal{E}_{\mathrm{F}}}{\mathrm{k_{\mathrm{B}}} T}, -\frac{\mathcal{E}_{\mathrm{lim}} - \mathcal{E}_{\mathrm{c}}}{\mathrm{k_{\mathrm{B}}} T} \right). \tag{5}$$

The total electron density is the sum of the two contributions:  $n_{\rm C} = n_{\rm C,2D} + n_{\rm C,3D}$ . Similar expressions apply for holes. The treatment of carriers in the non-quantized energy regime is mandatory to handle carrier accumulation properly.

## Bulk and Interface Trap Charges

VSP includes models for interface traps and bulk traps in arbitrarily stacked gate dielectrics. The occupation of the bulk traps can be defined by the user. The occupation of the two-dimensional interface states  $g_{\rm int}$  is calculated using Fermi statistics (13). The surface charge is given by

$$\rho_{\text{int}} = q \int_{\mathcal{E}_{\min}}^{\mathcal{E}_{\max}} g_{\text{int}}(\mathcal{E}_x) f(\mathcal{E}_x) d\mathcal{E}_x.$$

[6]

The hereby calculated bulk and surface charges enter the Poisson equation, and hence have to be evaluated at each iteration step.

## Direct Tunneling Current

The leakage current is calculated in a post processing step, since it has a negligible influence on the electrostatic potential. The direct tunneling current components from both continuum  $J_{\rm 3D}$  and quasi-bound states (QBS)  $J_{\rm 2D}$  are taken into account according to (14). Following (15), these direct tunneling current components can be estimated by

$$J_{\rm d,2D} = q \sum_{i} \frac{n_i}{\tau_i}, \qquad [7]$$

$$J_{d,3D} = q \int_{\mathcal{E}_{lim}}^{i} TC(\mathcal{E}_x, m_{diel}) N(\mathcal{E}_x, m_D) d\mathcal{E}_x.$$

[8]

The lifetime  $\tau_i$  of the  $i^{\text{th}}$  QBS is evaluated based on a semiclassical approximation (14) or a more rigorous formulation using the complex energy eigenvalues of the Schrödinger equation with open boundary conditions (16).

## Trap Assisted Tunneling Current

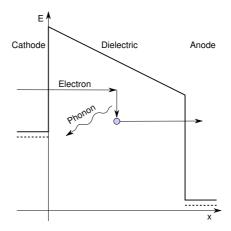

Trap assisted tunneling (TAT), which is a major reliability issue in novel gate stacks (17), is modeled by an inelastic single step tunneling process (18) as depicted in Fig. 3. The current density reads:

$$J_{\text{tat}} = q \int_0^{t_{\text{ox}}} \frac{N_{\text{t}}(x)}{\tau_{\text{c}}(x) + \tau_{\text{e}}(x)} \, \mathrm{d}x \,.$$

[9]

Here  $\tau_{\rm c}$  and  $\tau_{\rm e}$  denotes the capture and emission times of the traps, respectively, and  $N_{\rm t}(x)$  gives the spatial distribution of the trap density. The model has been calibrated to measurements.

Fig. 3: The trap assisted tunneling process, where the excess energy of the tunneling electrons is released by means of phonon emission.

## Application and Results

Conventional bulk MOS, partially depleted SOI, and novel device designs like DG-MOS structures can be investigated. With the described software package, NMOS structures with various gate dielectrics and gate materials have been simulated. For instance, the band edge energy of a MOS structure with a stacked gate dielectric under inversion conditions has been evaluated. The conduction band edge and some of the QBS are depicted in Fig. 1. A doping concentration of  $N_{\rm A}{=}5\times10^{17}{\rm cm}^{-3}$  in the bulk and  $N_{\rm D}{=}1\times10^{19}{\rm cm}^{-3}$  in the poly-silicon gate was assumed.

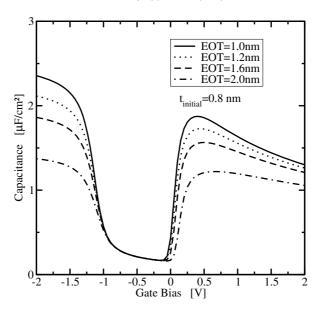

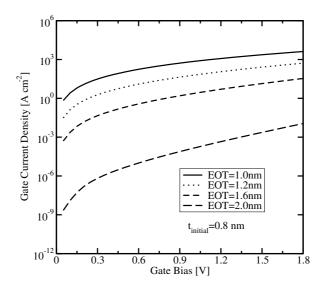

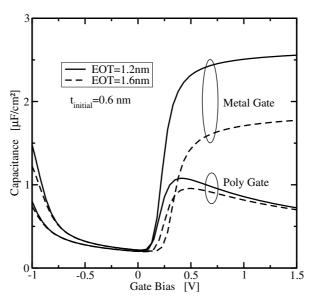

The capacitance voltage characteristics (CV) of MOS structures with different effective oxide thicknesses (EOT) including a  $\rm Si_3N_4$  layer are plotted in Fig. 4. The corresponding leakage currents are shown in Fig. 5. A nearly exponential increase of the leakage current by decreasing the oxide thickness can be clearly seen. Furthermore, structures including a layer of HfO<sub>2</sub> have been analyzed. The CV characteristics using a metal gate and a poly silicon gate are shown in Fig. 6. The effect of poly depletion can be clearly seen. The properties are considerably improved due the metal gate. Hence, the use of a metal gate is reasonable for further down scaling the EOT.

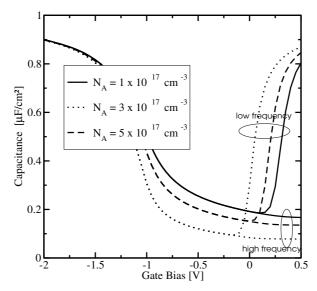

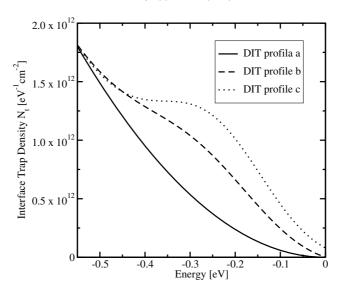

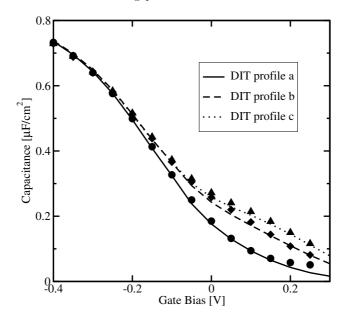

VSP has the capability to evaluate the static and the high-frequency CV characteristics of MOS structures. This feature is demonstrated in Fig. 7 showing the high-frequency CV curves which can be easier obtained by measurement than the static one. The influence of states at the semiconductor insulator interface for various density interface states (DIT) profiles (see Fig. 8) has been investigated. The corresponding CV characteristics are shown in Fig. 9.

Fig. 4: The CV characteristics of  $\rm SiO_2/Si_3N_4$  stacked gate dielectrics for different EOTs. An initial  $\rm SiO_2$  layer of 0.8 nm has been assumed.

Fig. 5: The gate current density of  ${\rm SiO_2/Si_3N_4}$  stacked gate dielectrics at several EOTs.

Fig. 6: The CV characteristic of  ${\rm SiO_2/HfO_2}$  stacked gate dielectrics for different EOTs. Metal gates are suitable for scaling the EOT down.

Fig. 7: The static and the high frequency CV characteristics of an NMOS structure with different substrate doping concentrations.

Fig. 8: The distribution of interface trap density versus energy. The value zero corresponds to the middle of the bandgap in the bulk  ${\rm Si.}$

Fig. 9: The circles, the diamonds, and the triangles show CV measurements of an example gate stack at 1 kHz, 10 kHz, and 1MHz, respectively. The simulated CV characteristics assuming the DIT profiles as shown in Fig. 8 can reproduce the measurement data.

## Summary

We developed the Vienna Schrödinger Poisson solver (VSP), a multi-purpose quantum mechanical solver, with the aim to aid theoretical as well as experimental research on novel gate dielectrics. A brief overview of models implemented in VSP including direct- and trap assisted tunneling has been given. Furthermore, some relevant features have been demonstrated by several examples.

## Acknowledgments

The authors are grateful to Stefan Abermann for numerous helpful discussions and providing the CV measurement data shown in Fig. 9. This work has been partly supported by the European Commission, project SINANO, IST 506844 and the Austrian Science Fund, special research program IR-ON, F2509.

#### References

- 1. International Technology Roadmap for Semiconductors, public.itrs.net (2005).

- 2. E. M. Vogel et al., IEEE Trans. Electron Devices, 45, 1350 (1998).

- 3. J. Zhang et al., Solid-State Electron., 44, 2165 (2000).

- 4. J. D. Casperson, L. D. Bell, and H. A. Atwater, J. Appl. Phys., 92, 261 (2002).

- 5. 4. M. LeRoy et al., J. Appl. Phys., 93, 2966 (2003).

- 6. C. M. Osburn  $et\,al.,\,IBM\,J.Res.Dev.,\,{\bf 46},\,299$  (2002).

- 7. G. D. Wilk, R. M. Wallace, and J. M. Anthony, J. Appl. Phys., 89, 5243 (2001).

- 8. J. Robertson, J. Vac. Sci. Technol., 18, 1785 (2000).

- 9. H.-S. P. Wong, IBM J.Res.Dev., 46, 133 (2002).

- 10. M. Karner et al., Proc. IWCE 255 (2006).

- 11. A. Trellakis et al., J. Appl. Phys., 81, 7880 (1997).

- 12. F. Stern, Phys.Rev.B., 5, 4891 (1972).

- 13. S. Mudanai et al., IEEE Electron Devices Letters, 23, 728 (2002).

- 14. E. Cassan, J. Appl. Phys., 87, 7931 (2000).

- 15. A. Gehring and S. Selberherr, Proc. SISPAD, 25 (2004).

- 16. M. Karner et al., Proc. SISPAD, 35 (2005).

- 17. M. Houssa et al., J. Appl. Phys., 87, 8615 (2000).

- 18. F. Jiménez-Molinos et al., J.Appl.Phys.,  $\mathbf{90}$ , 3396 (2001).