# Enhancement Mode HEMTs: Evaluation of Two Approaches by Numerical Simulation

Stanislav Vitanov and Vassil Palankovski (Faculty Mentor)

Advanced Material and Device Analysis Group

Institute for Microelectronics, TU Wien

Vienna, Austria

Email: {vitanov,palankovski}@iue.tuwien.ac.at

Abstract — Normally-off operation of high electron mobility transistors is desired for many reasons, however proved to be difficult to achieve, despite the rapid development of the depletion mode devices. Amongst the few approaches proposed so far, we focus on two, which promise high performance. The first device features an InGaN cap layer, while the later relies on gate recess technology. We perform DC and AC analyses, using our device simulator calibrated against experimental data, and compare the performance of the devices based on simulation results.

#### I. INTRODUCTION

The transport and material properties of GaN and AlN and their heterostructures have encouraged the research of AlGaN/GaN based transistors for various applications in the last decade. Consequently, outstanding results have been reported for the depletion mode (D-mode) high electron mobility transistors (HEMTs). However, for several applications enhancement mode (E-mode) devices are essential. In analog electronics they supersede the negative voltage supply and also assure a safe state in case of power loss. In digital electronics, they allow complementary logic.

Despite the interest in E-mode operation, the excellent results as in D-mode devices remain to be seen. The first E-mode transistor was reported back in 1996 by Khan *et al.* [1], and several other refinements followed. In this paper we focus on two recently proposed approaches. The first relies on gate recess combined with fluorine based surface treatment, while the second incorporates a thin InGaN layer, which raises the conduction band. For the study of the devices we use our two-dimensional device simulator MINIMOS-NT.

### II. DEVICE STRUCTURE WITH INGAN-CAP

The InGaN/AlGaN/GaN device structure was proposed by Mizutani *et al.* [2]. A 3  $\mu$ m thick GaN layer is grown on sapphire substrate. A 20 nm thick Al<sub>0.25</sub>Ga<sub>0.75</sub>N supply layer follows (5 nm undoped, 10 nm highly-doped, and 5 nm undoped). A 5 nm non-intentionally doped In<sub>0.2</sub>Ga<sub>0.8</sub>N layer is deposited next. The gate length l<sub>g</sub>=1.9  $\mu$ m, source-gate distance is 1.5  $\mu$ m, and gate-drain distance is 2.4  $\mu$ m.

# III. DEVICE STRUCTURE WITH RECESSED GATE

The gate recess structure and its fabrication is reported by Palacios *et al.* [3]. The 11 nm thick GaN channel is grown on-top of a 1 nm thick  $In_{0.1}Ga_{0.9}N$  back-barrier. A 1 nm thick AlN layer between the channel and the 25 nm  $Al_{0.33}Ga_{0.67}N$  is grown in order to improve the electron mobility. After the AlGaN surface treatment a 12 nm gate recess is performed, resulting in a gate-to-channel distance of 13 nm. The gate length  $l_g$  is 160 nm, source-gate distance is 0.6  $\mu$ m, and gate-drain distance is 0.9  $\mu$ m.

#### IV. SIMULATION SETUP

The device simulator MINIMOS-NT has proven to be a suitable tool for the analysis of heterostructure devices [4]. Recently, it has been used for the study of a whole generation of AlGaN/GaN HEMTs [5]. Since the longitudinal electric field in the channel reaches peak values of above 500 kV/cm, the hydrodynamic transport model is used to properly model electron transport and energy relaxation. Self-heating effects are accounted for by using a global self-heating model, which calculates a spatially constant lattice temperature. The value of the sheet charge at the AlGaN/GaN interface induced by the polarization effects is derived from the DC characteristics. Additional charges at the InGaN and AlGaN interfaces are accounted for [6].

# V. SIMULATION RESULTS

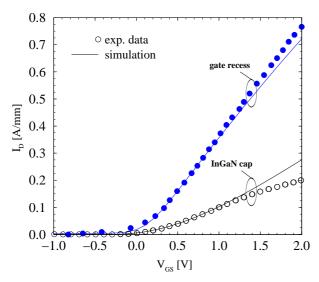

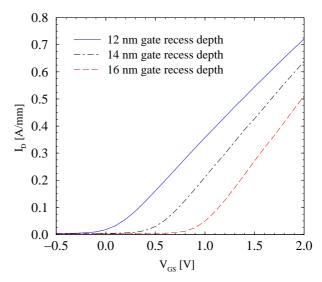

Figure 1 shows the results for the transfer characteristics of both devices. After a calibration of the sheet charges a good agreement is achieved. The InGaN/GaN device exhibits lower current, however a higher threshold voltage is achievable, without recessing the InGaN cap layer [2]. The threshold voltage of the recess device can be increased too (Figure 2) by increasing the recess depth.

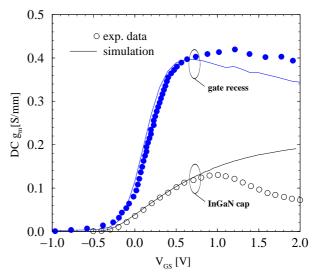

Figure 3 compares the DC transconductance  $g_{\rm m}$  for both devices. The decrease in the measured  $g_{\rm m}$  of the InGaN/AlGaN/GaN transistor at higher gate bias, might be due to non-idealities in the source and drain ohmic contacts, which are not considered in the simulation.

Figure 1: Comparison of the measured (symbols) and simulated (lines) transfer characteristics at  $V_{\rm ds}$ =5 V.

As expected, the recessed gate device exhibits a higher  $g_{\rm m}$  due to the much shorter gate length  $l_{\rm g}$  and the reduced gate-to-channel separation.

We also perform an AC analysis of the transistors. The recessed gate structure ( $\rm l_g=0.16~\mu m)$  exhibits transit cut-off frequency  $f_{\rm T}=85~{\rm GHz}$ , while our simulation gives  $f_{\rm T}=10~{\rm GHz}$  for the InGaN/AlGaN/GaN device ( $\rm l_g=1.9~\mu m)$ ). Note, that the product  $f_{\rm T}\times \rm l_g=19~{\rm GHz}\cdot \mu m$  is higher than  $14.4~{\rm GHz}\cdot \mu m$  of the recessed-gate device. Our simulation of an InGaN cap structure with  $\rm l_g=0.8~\mu m$  shows that  $f_{\rm T}=30~{\rm GHz}$  can be achieved.

#### VI. CONCLUSION

After a calibration against experimental data our device simulator provides reliable results for the DC and AC performance of the investigated novel HEMTs. This allows us to perform further device optimization, e.g. for higher current capability, higher threshold voltage, and better AC performance.

## ACKNOWLEDGMENTS

The authors acknowledge support from the Austrian Science Fund (FWF), Project START Y247-N13.

#### REFERENCES

- [1] M. Khan, Q. Chen, C. Sun, J. Yang, M. Blasingame, M. Shur, and H. Park. Enhancement and depletion mode GaN/AlGaN heterostructure field effect transistors. *Appl. Phys. Lett.* 68(4):514–516, Jan. 1996.

- [2] T. Mizutani, M. Ito, S. Kishimoto, and F. Nakamura. AlGaN/GaN HEMTs with thin InGaN cap layer for normally off operation. *IEEE Electron Device Lett.* 28(7):549–551, July 2007.

Figure 2: Simulated transfer characteristics at  $V_{\rm ds}$ =5 V for HEMTs with different gate recess depths.

Figure 3: Comparison of the measured (symbols) and simulated (lines) DC transconductance  $g_{\rm m}$  at  $V_{\rm ds}$ =5 V.

- [3] T. Palacios, C. Suh, A. Chakraborty, S. Keller, S. DenBaars, and U. Mishra. High-performance Emode AlGaN/GaN HEMTs. *IEEE Electron Device Lett.* 27(6):428–430, June 2006.

- [4] V. Palankovski and R. Quay. *Analysis and Simulation of Heterostructure Devices*. Wien New York, Springer, 2004.

- [5] S. Vitanov, V. Palankovski, S. Murad, T. Rödle, R. Quay, and S. Selberherr. Predictive Simulation of AlGaN/GaN HEMTs. *Tech.Dig. IEEE Compound Semiconductor IC Symp.* pp. 131–134, Nov. 2007.

- [6] S. Vitanov and V. Palankovski. Normally-off Al-GaN/GaN HEMTs with InGaN cap layer: A simulation study. *Solid-State Electron*. 2008, (in press).