# Modeling Floating Body Z-RAM Storage Cells

Viktor Sverdlov and Siegfried Selberherr

Abstract— Advanced floating body Z-RAM memory cells are studied. In particular, the scalability of the cells is investigated. First, a Z-RAM cell based on a 50nm gate length double-gate structure corresponding to state of the art technology is studied. A bi-stable behavior essential for Z-RAM operation is observed even in fully depleted structures. It is demonstrated that by adjusting the supply source-drain and gate voltages the programming window can be adjusted. The programming window is appropriately large in voltage as well as in current.

We further extend our study to a Z-RAM cell based on an ultra-scaled double-gate MOSFET with 12.5nm gate length. We demonstrate that the cell preserves its functionality by providing a wide voltage operating window with large current differences. An appropriate operating window is still observed at approximately 25-30% reduced supply voltage, which is an additional benefit of scaling. The relation of the obtained supply voltage to the one anticipated in an ultimate MOSFET with quasiballistic transport is discussed.

### I. INTRODUCTION

Standard DRAM cell scaling is hampered by the presence of a capacitor which is difficult to reduce in size. Recently, a revolutionary concept of a DRAM memory cell based on a transistor alone was introduced [1–8]. The ultimate advantage of this new concept is that it does not require a capacitor, and, in contrast to traditional 1T/1C DRAM cells, it thus represents a 1T/0C cell named Z (for zero)-RAM.

Although based on the two states of a MOSFET with different threshold voltages, the working principle of a Z-RAM cell is different from that of flash memory cells. Flash memory is based on a MOSFET with two gates. In addition to the top control gate used to open and close a MOSFET, the second gate called floating gate can trap charges. The floating gate is insulated from the channel and the control gate and may retain the trapped charge for years. A charge stored in the floating gate alters the threshold voltage of the cell. Depending on the amount of charge in the floating gate the MOSFET may be in an open or closed state at a given voltage at the control gate. Single-level cells are able to store one bit of information, while multi-level cells allow to store more than one bit per cell by choosing between multiple levels of electrical charge in the floating gate of a cell. Charging of the floating gate

V. Sverdlov and S. Selberherr are with the Institute for Microelectronics, TU Wien, Gußhausstraße 27–29/E360, A–1040 Wien, Austria, E-mail: {sverdlov|selberherr}@iue.tuwien.ac.at

is performed by hot-electron injection or by quantum mechanical tunneling through the potential barrier of a dielectric insulating the floating gate from the channel. Flash memory cells store the charge in a polysilicon floating gate. Due to electrical interference between adjacent cells, caused by the electric field of the electrons stored in the polysilicon gates, it is difficult to scale the floating gate cells beyond 45 nm technology node [9].

Replacement of the flash stack by a SONOS charge trapping stack allows to continue scaling [10]. SONOS devices the floating gate is replaced by a nonconductive nitride layer with a high density of deep charge trapping sites able to store the charge. SONOS is not susceptible to drain turn-on and floating gate interference. The gate stack of SONOS is up to  $\sim 50\%$ thinner as compared to flash. SONOS stacks offer a higher quality charge storage due to the smooth homogeneity of the nitride film compared to the polycrystalline film of flash and are less prone to oxide defects. Because of the insulating nature of the nitride film, a leakage path is usually locally confined and only able to affect a few traps. Therefore, SONOS is less sensitive to stress induced leakage currents, when the bottom oxide layer is thinner than in flash. A thinner oxide layer enables faster programming and lower write/erase voltages.

Recently a 10 nm bulk-planar SONOS type memory cell with a double tunnel junction, exhibiting good scalability while offering low write/erase voltages and excellent charge retention characteristics at the same time was demonstrated [11]. To increase the gate coupling factor silicon dioxide between the gates should be replaced with a high-k material. For charge trapping devices also high-k materials are needed as blocking oxides between the trap layer and the control gate. This demands high-k materials with large band gaps and band offsets,which limits the materials of choice and restricting the permittivity values in the moderate range from  $\sim 9-20\ [12].$

Contrary to flash memory cells, a Z-RAM cell does not contain an extra floating gate and is based on an SOI MOSFET alone. The functionality of the first generation Z-RAM is based on the possibility to store the majority carriers in the floating body. The carriers are generated by impact ionization caused by the minority carriers close to the drain. The threshold voltage is modified because of the charge accumulated in the body

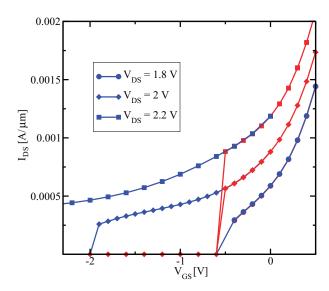

Fig. 1.  $I_{DS} - V_{GS}$  for a 50nm double gate MOSFET with silicon body thickness 10nm for different source-drain voltages  $V_{DS}$ . The hysteretic behavior is clearly observed for  $V_{DS} = 2.0$ V, while for  $V_{DS} = 2.2$ V the transition to the low current state is not observed even for  $V_{GS} \approx -2$ V.

thus guaranteeing the two states of a MOSFET channel, open and close, for a gate voltage chosen between the two thresholds.

Already the first generation Z-RAM is characterized by the two current values corresponding to the two logical states sufficient for applications [1]. In order to increase the size of the programming window one can use not only a MOSFET but also a bipolar transistor which is known to exist in SOI MOSFETs [21]. The bipolar transistor is usually considered as parasitic: when opened it hinders the functionality of the field-effect transistor.

The idea of the second generation Z-RAM is to exploit the properties of the bipolar transistor [13], allowing to expand the Z-RAM applicability to such of advanced non-planar devices as FinFETs, multi-gate and gate-all-around FETs. Contrary to the first generation, the current is flowing through the body of the structure. This increases the value of current by roughly the ratio of the fin radius to the surface layer thickness. The majority carriers are generated due to impact ionization. They are stored under the gate at the silicon/silicon dioxide interface. The stored charge provides good control over the bipolar current, in contrast to the first generation Z-RAM where the charge was stored in the area close to the buried oxide.

While keeping all advantages of the first Z-RAM generation, the most recent generation of Z-RAM cells [13] is characterized by a significantly enlarged programming window and much longer retention times. Recently, a 128Mb floating body RAM was designed and developed [8].

With CMOS downscaling continuing the question ob-

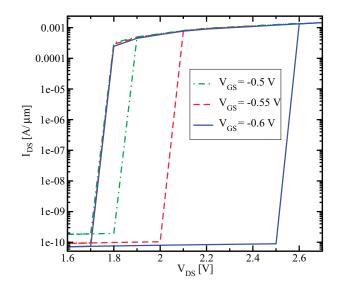

Fig. 2.  $I_{DS}-V_{DS}$  in a logarithmic scale for a 50nm double gate MOSFET with silicon body thickness 10nm, for different gate voltages  $V_{GS}$ . Hysteresis behavior is clearly observed for  $V_{GS}=$ -0.6V and  $V_{GS}=$ -0.55V, while it is nearly extinct at  $V_{GS}=$ -0.5V.

viously arises, whether a Z-RAM cell is also scalable. The goal of our study is to demonstrate that a Z-RAM cell preserves its functionality and remains operational for scaled MOSFETs.

In order to reach this goal, several issues must be addressed. Multi-gate FETs and finFETs are the most promising candidates for the upcoming CMOS MOS-FETs beyond the 22nm technology node. The functionality of both generations of Z-RAM cells on partially depleted SOI structures was recently demonstrated [13]. With channel length reduced, maintaining control over the channel becomes increasingly challenging, and several measures must be taken to preserve it. from improving electrostatic control by downscaling oxide thickness, the channel width can be reduced. This is achieved by artificially confining carriers within an ultra-thin silicon film. Due to the small dimensions of the silicon body there will be only few impurities inside. This results in unacceptably large threshold voltage fluctuations [14]. Fully depleted double-gate MOS-FETs with undoped intrinsic silicon body are perfectly functionable [15,16]. They preserve a good channel control, reasonable DIBL, large  $I_{on}/I_{off}$  ratio, and gain down to a channel length as short as 5nm [17]. It has recently been demonstrated that the functionality of a Z-RAM cell based on a fully depleted scaled MOSFET is preserved [18].

Because of the importance of impact ionization, the source-drain voltages are higher for Z-RAM operation, namely for writing, than for CMOS logic. An important question is whether this voltage can be reduced while scaling the device down. We demonstrate that, as for CMOS devices, this is generally true. Calcu-

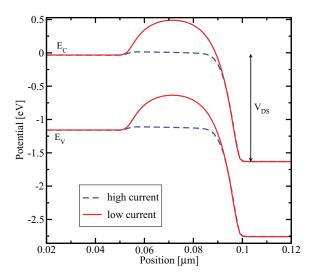

Fig. 3. Cross section of the potential energy from the source to the drain along the middle of the channel in a 50nm double gate MOSFET at  $V_{GS}=$ -1V and  $V_{DS}=$ 2V. The potential barrier is high in the low current state, and the transistor is closed. In the high current state there is no barrier, and the transistor is opened.

lated voltages for scaled Z-RAM cells are around 1.4V. This value is also in agreement with the writing voltage in a quasi-ballistic MOSFET with an ultra-short channel, which is considered as a good candidate for an ultimate MOSFET [14]. The value is higher than the projected supply voltage for upcoming MOSFETs. However, the current prototypes of a Z-RAM cell operate now at 2.2V [13]. Therefore, a decrease in supply voltage to 1.4V is significant.

#### II. STRUCTURES

For our analyses we have chosen two double-gate structures. One structure has a gate length of 50nm and a lightly doped ( $N_A = 10^{15} {\rm cm}^{-3}$ ) Si body of 10nm thickness. We have used metal gates with mid-gap work function and oxide with equivalent thickness of 2nm. Source and drain extentions are heavily doped to  $N_D = 10^{20} {\rm cm}^{-3}$  in order to provide enough injected electrons. This structure corresponds to the current technology node [19].

The scaled double-gate structure has a gate length of 12.5nm and a lightly doped Si body of 3nm thickness. An oxide with an equivalent thickness of 1nm is chosen, The source and drain extensions are heavily doped to  $N_D=10^{20}{\rm cm}^{-3}$ .

The analyses were performed with the MINIMOS-NT device simulator [20]. Impact ionization is essential to the functionality of a Z-RAM cell. Electron-hole recombination is very important as antagonistic mechanism. Similar parameters for impact ionization and for recombination are used for both structures. Bandto-band tunneling was also included with a standard model [20].

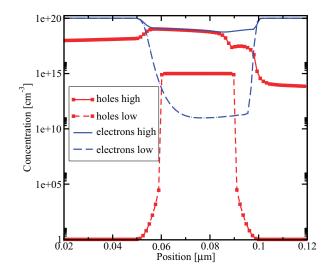

Fig. 4. Cross section of the electron and hole concentrations along the middle of the channel in a 50nm double gate MOSFET at  $V_{GS}$  =-1V and  $V_{DS}$  =2V for the two current states. The higher majority carrier concentration in the channel in the high current state is due to holes captured in the potential wells clearly seen in Fig. 3 under the gates.

#### III. RESULTS

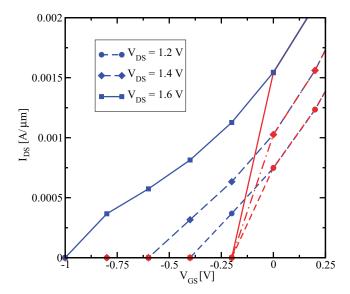

The results for current calculations as function of the gate voltage for a 50nm double-gate structure are shown in Fig. 1 and Fig. 2. At high positive gate voltages the current values do not depend on the gate voltage scan direction.

For negative gate voltages the situation is completely different. In a forward scan direction for the gate voltage, the current stays low for both values of the source-drain voltage until a certain critical value is reached. This part of the  $I_{DS}-V_{GS}$  corresponds to the subthreshold regime. Due to negligible DIBL in a 50nm double-gate structure, the current dependence in the subthreshold regime is similar for both values of the source-drain current.

As soon as a critical current value is reached, the source-drain current rapidly increases by several orders of magnitude. The current keeps increasing for positive gate voltage values.

In a reverse gate voltage scan, the current first slowly decreases. For positive gate voltages, the current takes exactly the same values as for the forward scan. Therefore, the  $I_{DS}-V_{GS}$  curve is completely reversible for both values of the source drain voltage, as already mentioned. However, the current value does not decrease sharply for moderately negative values of gate voltages, although it keeps slightly decreasing. The current values at the reverse scan remain several orders of magnitude higher than the values for the forward scan. The relatively large current value is maintained down to  $V_{GS}$ =-2V for  $V_{DS}$ =2.0V, where it abruptly decreases by several orders of magnitude. Thereby the MOSFET

Fig. 5. Contour plot of the hole distribution in the 12.5nm long MOSFET channel for the high current state. Close to the gates the hole concentration is high. Due to quantum correction, the centroid of the hole concentration is at a certain distance from the gates.

Fig. 6. Contour plot of the hole distribution in the 12.5nm long MOSFET channel for the low current state. The concentration is small. Due to quantum correction, the centroid of the hole concentration is at a certain distance from the gates.

is turned back into the subthreshold regime, completing the hysteresis loop. Indeed, the previous current value cannot be reached just by inverting the scan direction. Instead, if one increases the gate voltage, the current will follow the lower subthreshold branch, until the critical current value is reached at  $V_{GS}$ =-0.6V. The point with relatively high current at  $V_{GS} = -2V$  can only be reached by inverting the gate voltage scan after the high current value was achieved at positive gate voltages. Interestingly, if we increase the source-drain voltage to  $V_{DS}=2.2V$ , the abrupt transition to the subthreshold regime during the reverse voltage scan cannot be observed for technically relevant negative gate voltage values. A similar behavior is observed when a parasitic bipolar transistor turns on in floating body SOI structures [21], which is usually considered as undesirable.

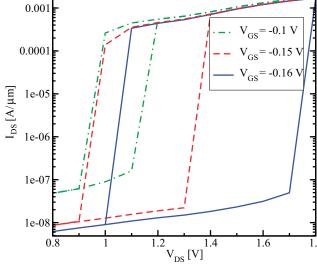

The two different current states corresponding to the same drain and gate voltages, seen also on  $I_{DS} - V_{DS}$  characteristics shown in Fig. 2 are essential for Z-RAM functionality [13]. We are now analyzing the physical reasons for these two different current states.

Fig. 3 displays the potential profile from the source to the drain electrode, cut in the middle of the silicon body, for two different current states corresponding to the same source and drain voltage. In the low current state the potential has a large barrier under the gate preventing the current flowing from the source to the drain. On the contrary, in the high current state the potential is nearly flat in the source-gate region, and the transistor is opened. Such a difference in potential profiles is due to different charge distributions in the system shown in Fig. 4. In the state with low cur-

rent the electron concentration in the channel is small and the majority carrier concentration (holes) is small too (Fig. 4). In the state with high current one naturally has a higher electron concentration in the channel. More important, the hole concentration in the channel has also increased as shown in Fig. 4. The hole concentration in the channel is higher close to the gates, in agreement with [13]. Holes are generated close to the drain region due to impact ionization. The electric field in the channel close to the drain region drives generated holes in the body region, where they accumulate. This accumulated positive charge pins down the conduction band to the potential in the source and opens the transistor.

Holes recombine with electrons primarily via the Shockley-Read-Hall mechanism. Excess holes visible in Fig. 4 flow into the source region. Their extra positive charge is compensated by additional electrons, resulting in a slightly higher electron concentration than the equilibrium concentration determined by  $N_D=10^{20}{\rm cm}^{-3}$ .

The nature of the two current states analyzed above allows to determine conditions, where the transitions between them occur. One important ingredient is obviously impact ionization which is usually characterized by the multiplication factor M>1. The positive feedback loop is activated, when the collector current is larger than the base current. Since the hole base current is proportional to M-1, the positive feedback corresponds to the condition [21]

$$\beta_F(M-1) > 1,\tag{1}$$

where  $\beta_F$  is the common-emitter current gain. The increase of the drain current is triggered by the positive

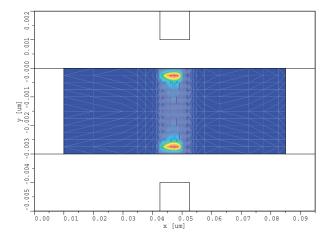

Fig. 7.  $I_{DS}-V_{GS}$  for a scaled double gate MOSFET with the gate length 12.5nm and silicon body thickness 3nm, for three source-drain voltage. Hysteresis behavior is clearly observed.

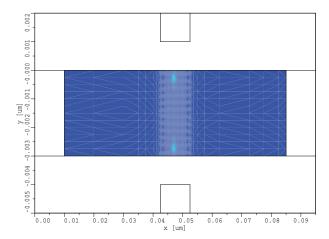

Fig. 8.  $I_{DS} - V_{DS}$  in a logarithmic scale for a 12.5nm double gate MOSFET with silicon body thickness 3nm, for different gate voltages  $V_{GS}$ . Hysteresis behavior is clearly observed.

feedback, saturating when the transistor opens.

If we now reduce the gate voltage, an increasing number of holes must be stored under the gate to compensate the gate voltage decrease and keep the transistor open. This results in an increased recombination rate which reduces  $\beta_F$ . At large negative gate voltages the condition (1) cannot be fulfilled. The positive feedback loop breaks, which results in a sudden decrease of the current. The number of generated holes drops. Their concentration under the gate reduces and they cannot screen the gate potential. This leads to a potential barrier increase which further reduces the current. The process stops, when the transistor is closed.

The consideration above can explain the  $I_{DS}-V_{GS}$  behavior at  $V_{DS}=2.0\mathrm{V}$  for the reverse gate voltage scan. For the forward gate voltage scan the transistor stays in the closed state for higher gate voltages than for the reverse scan. The reason is the absence of current in the closed state. However, due to an exponential current increase in the subthreshold regime at a gate voltage close to zero, the current reaches a critical value after which the positive feedback loop opening the transistor activates. The critical current values only slightly depend on drain voltage, due to a dependence of  $\beta_F$  on drain voltage.

We have demonstrated that a programming window, which is formed by the two current values and the two gate voltage values when switching appears, is sufficiently large for stable Z-RAM operation on 50nm double-gate transistors. We now present simulations of a double-gate structure with 12.5nm gate length. Excess hole concentrations in the open and close states corresponding to the large and low values of the current are shown in Fig. 5 and Fig. 6, respectively. Due to

quantum correction included in simulations, the charge centroid is shifted away from the interface. Results of  $I_{DS} - V_{GS}$  calculations and hole concentrations shown in Fig. 7 and Fig. 8 clearly display a hysteretic behavior similar to that observed for a 50nm MOSFET. For all considered source-drain voltages the transition to the high current state appears at slightly negative gate voltages. For the reverse scan the transition to the low current state is observed at large negative gate voltages for  $V_{DS} = 1.6 \text{V}$ , while for  $V_{DS} = 1.2 \text{V}$  the hysteresis has nearly disappeared. For  $V_{DS} = 1.4 \text{V}$ , the transition to the low current state occurs at  $V_{GS}$  = -0.6V. This results in a relatively large programming window sufficient for successful Z-RAM cell operation. It is thus demonstrated that a Z-RAM cell built on a scaled double-gate MOSFET with 12.5nm gate length preserves its functionality.

# IV. DISCUSSION

The  $I_{DS}-V_{GS}$  behavior for a 12.5nm gate length MOSFET looks principally analogous to the behavior of a 50nm MOSFET. One difference between the results is that the current density for a thinner and shorter double-gate structure is nearly an order of magnitude smaller. However, this is not a substantial limitation, because the important criterion for Z-RAM functionality is the difference between the two values of current in the two different current states, which is still several orders of magnitude for a 12.5nm double-gate structure.

Although our simulations show that a very small Z-RAM cell is functionable, the program window was found to reduce gradually with scaling. This suggests that for more accurate predictions a more refined treatment of quantum effects beyond quantum correction

is needed. Another anticipated direction for improvement is a choice of a more accurate model for band-to-band tunneling. Although band-to-band tunneling was included within a standard model [20], a different model for band-to-band tunneling indicates a possible failures during "Read 0" operation in ultra-scaled Z-RAM cells [24].

Our simulations predict that the supply voltages are 25-30% smaller for a Z-RAM based on a scaled MOS-FET. The obtained substantial decrease in supply voltage is comparable with the anticipated decrease for scaled logic devices. We should add, however, that the impact ionization model used in the simulations depends on the local field only. When the channel length is reduced, the local field in the channel at the drain end is expected to increase. Therefore, the local field impact ionization model can overestimate impact ionization. Another potential limitation of the applicability of our approach is that in scaled devices transport becomes quasi-ballistic, and the impact ionization models used in Monte Carlo simulations of hot carrier transport [22] become relevant. These models are characterized by threshold energies above which impact ionization starts, with the lowest threshold of 1.2eV. It was recently argued that due to the presence of energetic carriers in an injected distribution substantial impact ionization can be present even, when the source-drain voltage is smaller than the threshold [23]. However, because of the gap increase due to size quantization in a 3nm silicon film, we believe that 1.2eV is a fair estimate of a Z-RAM cell supply voltage, which is consistent with  $V_{DS} = 1.4$ V obtained in our simulations.

## V. CONCLUSION

We have shown that a Z-RAM cell built on a scaled double-gate MOSFET preserves its functionality by providing a wide voltage operating window with large current differences. We also predict a decrease in the supply voltage to 1.2-1.4V, which is about 25-30% smaller than in current prototypes. Results are in agreement with recent considerations of floating body RAM scaling down to 32nm technology node based on experimental results [8].

#### References

- S. Okhonin, M. Nagoga, J. Sallese, and P. Fazan, "A SOI Capacitor-Less 1T-DRAM Concept," in SOI Intl. Conf. Techn. Dig., 2001, pp. 153–154.

- [2] E. Youshida and T. Tanaka, "A Capacitor-Less 1T-DRAM Technology Using Gate-Induced Drain-Leakage (GIDL) Current for Low-Power High-Speed Embedded Memory", IEEE Trans. Electron Devices, vol. 53, pp. 692–697, 2006.

- IEEE Trans. Electron Devices, vol. 53, pp. 692–697, 2006.

[3] D. Ban, U.E. Avci, U. Shah et al.," Floating Body Cell with Independently-Controlled Double Gates for High Density Memory", in IEDM Techn. Dig., 2006, pp. 573–576.

- [4] T. Shino, N. Kusunoki, T. Higashi et al., "Floating Body RAM Technology and its Scalability to 32nm Node and Beyond", in *IEDM Techn. Dig.*, 2006, pp. 569–572.

- [5] D. Ban, U.E. Avci, D.L. Kencke, and P.L.D. Chang, "A

- Scaled Floating Body Cell (FBC) Memory with High-k+Metal Gate on Thin-Silicon and Thin-BOX for 16nm Technology Node and Beyond," in  $Proc.\ 2008\ VLSI\ Symposium,\ 2008,\ pp.\ 92–93.$

- [6] M.G. Ertosun, H. Cho, P. Kapur, and K.C. Saraswat, "A Nanoscale Vertical Double-Gate Single-Transistor Capacitorless DRAM," *IEEE Electron Device Lett.*, vol. 29, no. 6, pp. 615–617, 2008.

- [7] U. Avci, I. Ban, D. Kencke, and P. Chang, "Floating Body Cell (FBC) Memory for 16-nm Technology with Low Variation on Thin Silicon and 10-nm BOX", in *Proceedings IEEE International SOI Conference*, 2008, pp. 29–30.

[8] T. Hamamoto and T. Ohsawa, "Overview and Future Chal-

- [8] T. Hamamoto and T. Ohsawa, "Overview and Future Challenges of Floating Body RAM (FBRAM) Technology for 32nm Technology Node and Beyond", Solid-State Electron., vol. 53, no. 7, pp. 676–683, 2009.

- [9] M. Boutchich, D.S. Golubovic, N. Akil, M. van Duuren, "Evaluation of Layered Tunnel Barrier Charge Trapping Devices for Embedded Non-volatile Memories", *Microelectronic Engineering*, vol. 87, no. 1, pp. 41–46, 2010.

- [10] J. Bu, M.H. White, "Design Considerations in Scaled SONOS Nonvolatile Memory Devices", Solid-State Electron., vol. 45, no. 1, pp. 113-120, 2001.

- tron., vol. 45, no. 1, pp. 113–120, 2001.

[11] R. Ohba, Y. Mitani, N. Sugiyama, S. Fujita, "10 nm Bulk-Planar SONOS-Type Memory with Double Tunnel Junction and Sub-10 nm Scaling Utilizing Source to Drain Direct Tunnel Sub-Threshold, *IEDM Techn. Dig.*, 2008, pp. 1–4.

- [12] J.A. Kittl, K. Opsomer, M. Popovici, N. Menou, B. Kaczer, X.P. Wang, C. Adelmann, M.A. Pawlak, K. Tomida, A. Rothschild, B. Govoreanu, R. Degraeve, M. Schaekers, M. Zahid, A. Delabie, J. Meersschaut, W. Polspoel, S. Clima, G. Pourtois, W. Knaepen, C. Detavernier, V.V. Afanas'ev, T. Blomberg, D. Pierreux, J. Swerts, P. Fischer, J.W. Maes, D. Manger, W. Vandervorst, T. Conard, A. Franquet, P. Favia, H. Bender, B. Brijs, S. Van Elshocht, and M. Jurczak, J. Van Houdt, D.J. Wouters, "High-k Dielectrics for Future Generation Memory Devices", Microelectronic Engineering, vol. 86, no. 7-9, pp. 1789–1795, 2009.

- [13] S. Okhonin, M. Nagoga, E. Carman, R. Beffa, and E. Faraoni, "New Generation of Z-RAM," in *IEDM Techn. Dig.*, 2007, pp. 925–928.

- [14] K. K. Likharev, "Sub-20-nm Electron Devices," in Advanced Semiconductor and Organic Nano-Techniques, H. Morkoc, Ed. New York: Academic Press, 2003, pp. 239–302.

- [15] Y. Naveh and K. K. Likharev, "Modeling of 10 nm-Scale Ballistic MOSFETs," *IEEE Electron Device Lett.*, vol. 21, no. 5, pp. 242–244, 2000.

- [16] M. Lundstrom, "The Ultimate MOSFET and the Limits of Miniaturization," in *Intl. Semiconductor Device Research Symposium Techn. Dia.*, 2007, pp. 1-1.

- Symposium Techn. Dig., 2007, pp. 1–1.

[17] V. A. Sverdlov, T. J. Walls, and K. K. Likharev, "Nanoscale Silicon MOSFETs: A Theoretical Study," IEEE Trans. Electron Devices, vol. 50, no. 9, pp. 1926–1933, 2003.

- [18] S. Okhonin, M. Nagoga, C.-W. Lee, J.-P. Colinge, A .Afzalian, R. Yan, N Dehdashti Akhavan, W. Xiong, V. Sverdlov, S. Selberherr, C. Mazure, "Ultra-scaled Z-RAM cell", in SOI Intl. Conf. Techn. Dig., 2008, pp. 157–158.

[19] W. Xiong, C. R. Cleavelin, C.-H. Hsu, M. Ma, K. Schrue-

- [19] W. Xiong, C. R. Cleavelin, C.-H. Hsu, M. Ma, K. Schruefer, K. V. Armin, T. Schulz, I. Cayrefourcq, C. Mazure, P. Patruno, M. Kennard, K. Shin, X. Sun, T.-J. Liu, K. Cherkaoui, and J. Colinge, "Intrinsic Advantages of SOI Multiple-Gate MOSFET (MuGFET) for Low Power Applications," ECS Transactions, vol. 6, no. 4, pp. 59–69, 2007.

- [20] MINIMOS-NT 2.1 User's Guide, Institut für Mikroelektronik, Technische Universität Wien, Austria, 2004.

- [21] J.-P. Colinge, Silicon on Insulator Technology: Materials to VLSI. Boston: Kluwer Academic Publishers, 2004.

- [22] M. V. Fischetti, S. E. Laux, and E. Crabbé, "Understanding Hot-Electron Transport in Silicon Devices: Is there a Shortcut?" J.Appl.Phys., vol. 78, no. 2, pp. 1058–1085, 1995.

- cut?" J.Appl.Phys., vol. 78, no. 2, pp. 1058–1085, 1995.

[23] J. Guo, M. Alam, and Y. Ouyang, "Subband Gap Impact Ionization and Excitation in Carbon Nanotube Transistors," J. Appl. Phys., vol. 101, pp. 064311–1-064311–5, 2007.

- J.Appl.Phys., vol. 101, pp. 064311–1-064311–5, 2007.

[24] A. Schenk, "Scalability Study of Floating Body Memory Cells" in *Proc. of SISPAD*, 2009, pp. 31–34.