# **Modeling of Modern MOSFETs with Strain**

Viktor A. Sverdlov and Siegfried Selberherr

Institute for Microelectronics, TU Wien, Gußhausstraße 27-29 / E360, A-1040 Wien, Austria e-mail: {sverdlov | selberherr@iue.tuwien.ac.at}

#### **Abstract**

We review modeling techniques to evaluate strain induced performance enhancement of modern MOSFETs. While p-channel MOSFETs were intensively studied and are quite well understood, electron transport in n-type strained structures received surprisingly little attention. A rigorous analysis of the subband structure in inversion layers and thin silicon films under stress is performed. Calculated subband effective masses strongly depend on shear strain and film thickness. A decrease of the transport effective mass under tensile stress in [110] direction and an additional splitting between the unprimed subbands with the same quantum number guarantees a mobility enhancement even in ultra-thin (001) silicon films. This increase of mobility and drive current combined with the improved channel control makes multi-gate MOSFETs based on thin films or silicon fins preeminent candidates for the 16nm technology node and beyond.

#### 1. Introduction

The rapid increase in computational performance and speed of modern integrated circuits is supported and guaranteed by the aggressive downscaling of semiconductor devices. Size reduction of MOSFETs is successfully continuing because of innovative changes in the technological processes and the introduction of new materials. Until recently, the main method of increasing complementary metal-oxide semiconductors (CMOS) transistor performance was based on geometrical scaling, which led to an outstanding success in increasing the speed and functionality of electronic devices. Although a possibility to build a MOSFET with a gate length as short as 6nm has been demonstrated [1], the semiconductor industry is facing increasing difficulties with ongoing scaling continuing. Among them are the short channel effects and increasing power dissipation caused mostly by the high leakage currents. Rising costs of chip manufacturing are making further scaling increasingly more problematic: the feasibility

of fabrication cannot be easily guaranteed, and maintaining performance and reliability are becoming severe issues. With scaling apparently approaching its fundamental limits, the semiconductor industry is facing critical challenges. New engineering solutions and innovative techniques are required to improve CMOS device performance.

Strain-induced mobility enhancement is the most attractive way chosen by the industry to boost the device speed and performance. It will certainly maintain its key position among upcoming technological changes for the future technology generations. The 32nm MOSFET process technology developed by Intel [2] employs advanced fourth generation strain engineering techniques. Apart from strain, the 32nm MOSFET process technology involves new hafnium-based high-k dielectric/metal gates first introduced for the 45nm technology node [3], which represented a major change in the technological process since the introduction of MOSFETs into mass production. Although alternative channel materials with a mobility higher than in silicon were already investigated [4], it is commonly believed that strained silicon will be the main channel material even for MOSFETs beyond the 22nm technology node. In addition, new device architectures based on multi-gate structures with better electrostatic channel control and reduced short channel effects are gaining momentum [5]. A multi-gate MOSFET architecture is expected to be introduced for the 16nm technology node. Combined with a high-k dielectric/metal gate technology and strain engineering, a multi-gate MOSFET appears to be the ultimate device for high-speed operation with excellent channel control, reduced leakage currents, and low power budget.

In the following we shortly review stress techniques commonly used to enhance transport in CMOS FETs. We summarize the results for the relatively well understood mobility enhancement in p-channel MOSFETs. Then we briefly review the two-band  $\mathbf{k} \cdot \mathbf{p}$  model for the conduction band in silicon and analyze the subband structure in (001) ultra-thin films by calculating the subband quantization energies and effective masses. The subband parameters are embedded into a subband Monte Carlo procedure to evaluate the low-field mobility. Results of the maximum current enhancement in a MOSFET at its ultimate scaling limit are analyzed.

# 2. Strain Engineering Techniques

The techniques to introduce stress can be classified in two categories. Global stress in silicon is created by epitaxially growing silicon on a (001) SiGe substrate. Due to the crystal lattice mismatch between silicon and SiGe, silicon is symmetrically stretched along the directions [100] and [010]. n-channel MOSFETs on a strained substrate

exhibit a 70% higher effective mobility [6]. The global stress techniques did not receive a broad commercial appreciation and recognition. The reason is the decrease of the hole mobility in p-channel MOSFETs in biaxially strained silicon on (001) SiGe substrate [7, 8], regardless of the large hole mobility enhancement anticipated in the bulk [9]. The semiconductor industry has adopted a path on which stress is delivered to *each* n-channel and p-channel MOSFET *independently*. For (001) oriented wafers the hole mobility is enhanced along the [110] direction by compressive stress, applied in the same direction, while the electron mobility is enhanced by [110] tensile stress. A way to introduce compressive stress in a p-channel MOSFET is to fill the source and drain regions with SiGe [10, 11]. Additional uniaxial stress is typically introduced by compressive or tensile capping layers [12-14]. The advantage of local stress techniques is that they can be combined and superimposed on the same wafer. The existing state-of-the-art strain engineering processes are also compatible with the hybrid orientation technique to boost mobility [15].

### 3. Modeling of p-channel MOSFETs

Mobility enhancement in p-channel MOSFETs was intensively studied theoretically and good understanding was achieved. Due to the complex valence band structure in silicon, the considerations must be based on the 6-band k·p model [16], which takes into account the bands of heavy and light holes and the split-off band due to spin-orbit interaction. When stress is applied, splitting between the heavy and light hole bands and/or effective mass change appears. Strain can be easily incorporated into the formalism of the k·p method [17]. Since the heavy and light holes have different conductivity masses, the strain-induced change in their relative population introduces the mobility enhancement. Scattering depends strongly on strain because of the change of the density of states and band splitting. An accurate self-consistent solution of the Schrödinger, Poisson, and the Boltzmann equation is needed in order to evaluate the mobility enhancement. The hole mobility in inversion layers for general strain conditions was carefully studied for several important substrate orientations [7, 8, 18]. At high stress the largest surface mobility enhancement factor was predicted for (001) oriented wafers, when transport is along the [110] direction under compressive uniaxial stress [8]. The maximal value of the mobility enhancement was found along the [110] direction under uniaxial compressive stress at the (001) and (1-10) interfaces [8]. Recently, a nearly three-fold on-current enhancement due to [110] compressive stress

was predicted in strained double-gate structures with the help of a deterministic multisubband device solver [19].

### 4. Peculiarities of Modeling n-channel MOSFETs

The conduction band in silicon consists of six equivalent valleys with their energy minima located close to the corresponding *X*-points of the first Brillouin zone. Within the parabolic approximation each valley is characterized by two transversal and one longitudinal effective mass [20]. Biaxial stress removes the degeneracy between the six equivalent valleys [17, 21]. The occupation of the valleys with favorable transport mass and reduced inter-valley scattering leads to a bulk mobility enhancement. Mobility enhancement in biaxially stressed silicon, both in the bulk [9] and in the electron inversion layers [22, 23], was carefully investigated.

It was found [24] that the electron mobility enhancement data on (001) substrate under [110] uniaxial stress can be explained only, if a conductivity mass dependence on stress is assumed. This effective mass dependence cannot be recovered within the effective mass approximation, and a generalization of the conduction band description in uniaxially stressed silicon is needed.

An approach based on the full band structure computed with the empirical pseudo-potential method (EPM) [25, 26] is computationally demanding. A 30-band **k·p** method [27] method is also computationally involved. In contrast, the two-band **k·p** model [25, 28, 29] developed in the vicinity of the *X*-point provides a simple but accurate framework to compute the subband structure, in particular the dependences of the electron effective masses on shear strain and the thickness of thin films [30].

#### 4.1. Model of the conduction band in silicon

From symmetry considerations the two-band  $\mathbf{k} \cdot \mathbf{p}$  Hamiltonian of a [001] valley in the vicinity of the *X* point of the Brillouin zone in silicon must be in the form [17]:

$$H = \left(\frac{\hbar^{2}k_{z}^{2}}{2m_{l}} + \frac{\hbar^{2}(k_{x}^{2} + k_{y}^{2})}{2m_{l}}\right)I + \left(D\varepsilon_{xy} - \frac{\hbar^{2}k_{x}k_{y}}{M}\right)\sigma_{z} + \frac{\hbar^{2}k_{z}k_{0}}{m_{l}}\sigma_{x},$$

(1)

where  $\sigma_{x,z}$  are the Pauli matrices, I is the 2×2 unity matrix,  $m_t$  and  $m_l$  are the transversal and the longitudinal effective masses,  $k_0 = 0.15 \times 2\pi/a$  is the position of the valley minimum relative to the X point in unstrained silicon,  $\varepsilon_{xy}$  denotes the shear strain

component,  $M^{-1} \approx m_t^{-1} - m_0^{-1}$ , and D=14eV is the shear strain deformation potential [17, 28, 29].

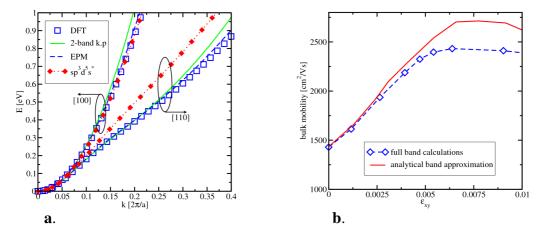

The conduction band dispersions computed with several methods in [100] and [110] directions are compared in Fig.1a. As illustrated in this figure the **k·p** method

Figure 1 a. Comparison of bulk dispersions close at the minimum of the [001] valleys of the conduction band in [100] and [110] directions. The density-functional theory (DFT) and the empirical pseudo-potential method (EPM) based results are similar, while the sp<sup>3</sup>d<sup>5</sup>s\* tight-binding model underestimates anisotropy;

**b**. Bulk mobility computed by accounting for the full-band structure (symbols) and approximated with non-parabolic dispersion of six valleys (line).

reproduces the band structure accurately at energies below 0.8eV, which is sufficient to describe the subband structure and transport properties of advanced MOSFETs.

Shear strain  $\varepsilon_{xy}$  affects the [001] valleys by moving them down in energy, thus lifting the six-fold degeneracy. In the presence of shear strain the transport mass  $m_t$  of the [001] valleys acquires two different values along (+) and across (-) tensile stress direction [29]:

$$m_{t}(\eta)/m_{t} = [1 \pm |\eta| m_{t}/M]^{-1}, \qquad |\eta| \le 1;$$

(2a)

$$m_t(\eta)/m_t = [1 \pm m_t/M]^{-1}, \qquad |\eta| \ge 1, \quad (2b)$$

where  $\eta = m_l \varepsilon_{xy} / \hbar^2 k_0^2$ .

Fig.1b shows that the bulk mobility in the [110] tensile stress direction computed within the analytical parabolic band approximation for the conduction band with the effective masses (2) gives accurate results up to the strain level of 0.5%, after which a more refined conduction band model based on (1) is needed. \

The model for the effective masses (2) was used to evaluate the mobility enhancement in long and short n-channel MOSFETs [31]. The highest mobility is achieved for the standard [110]/(001) channel, although the low-field mobility of [-110](110) channel

experiences the highest enhancement factor and approaches the [110]/(001) value at high stress.

In ultra-thin films, however, the bulk expression (2) for the effective masses is not sufficient. In order to find appropriately accurate values for the subband parameters the confinement potential U(z)I must be included in the Hamiltonian (1).

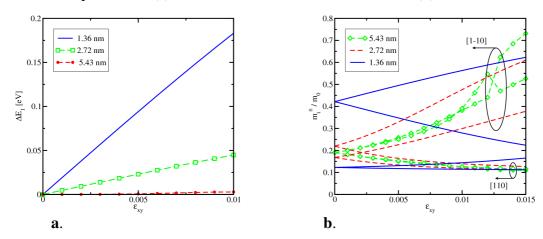

Figure 2 a. Shear strain induced splitting of the ground subbands for several film thicknesses. In ultra-thin films the splitting is larger than kT already for moderate stress.

**b**. Effective masses of the two ground subbands. In ultra-thin films the effective masses of the two ground subbands are different even without stress.

#### 4.2. Subbands in (001) silicon films

To obtain the subband structure of (001) thin films we solve the Schrödinger equation with the Hamiltonian (1), where the substitution  $k_z = -i\partial/\partial z$  is made and the confinement potential IU(z) is introduced. In unstrained films the unprimed subband ladder originates from two different [001] transport masses and is two-fold degenerate. Shear strain makes the bulk dispersion non-parabolic. This lifts the degeneracy between the unprimed subbands, which results in a so called valley splitting. The numerical values of the splitting between the ground subbands are shown in Fig.2a. It proves that the valley splitting can be effectively controlled by adjusting the shear strain and modifying the effective thickness t of the electron system. The valley splitting in ultrathin films can be quite large already at reasonable stress values.

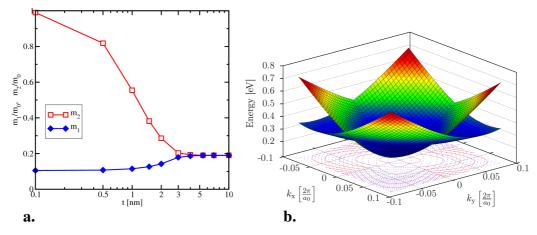

Fig.3a demonstrates the transport masses in the [110] direction of the two ground subbands as function of shear strain, for several film thicknesses. The dependence of the effective masses deviates substantially from the bulk expression (2) at large strain values and/or at thin film thicknesses. Interestingly, in thin films the two subbands originating from the two valleys cease to be equivalent by developing different curvature effective masses along the [110] (and [-110]) direction even without strain as demonstrated in Fig.2b.

#### 4.3. Transport in (001) films

A multi-subband Monte Carlo method is used to evaluate the mobility in MOSFETs with thin silicon films. The method is based on the solution of the linearized multi-subband Boltzmann equation. A particular advantage of the method is that it includes degeneracy effects due to the Pauli exclusion principle, which are important in thin films at high carrier concentrations. Scattering with phonons and surface roughness is

Figure 3 a. The thickness dependence of the effective masses in unstrained films of the two lowest unprimed subbands.

**b.** Dispersions of the two ground subbands for a film thickness of 1.36nm.Without strain the subbands are degenerate at the minimum, but they develop different curvature effective masses along [110] (and [-110]) direction.

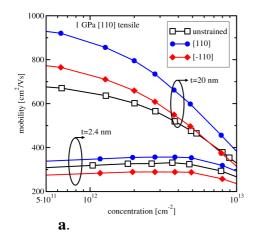

included. Fig.4a shows the mobility in (001) silicon films for two film thicknesses under tensile uniaxial stress of 1GPa in [110] direction. Stress shifts down and populates more the two [001] unprimed subbands with favorable transport masses providing the mobility enhancement in the stress direction for a 20nm film. Apart from shifting the primed subbands with unfavorable transport masses in the (001) plane up in energy and de-populating them, tensile stress in [110] direction generates a shear component which modifies the transport effective masses of the unprimed subbands The decrease of the effective masses in [110] direction induced by shear strain is the main reason for the mobility enhancement in thin films, as demonstrated in Fig.4a.

Calculated subband parameters allow evaluating current in an ultra-scaled MOSFET.

Figure 4 a. The mobility enhancement due to tensile stress of 1GPa in [110] transport direction is preserved even in ultra-thin films due to the transport mass decrease.

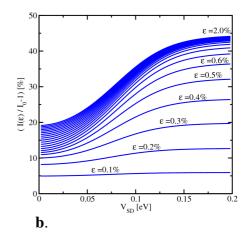

**b.** Current enhancement as a function of drain bias for several shear strain values for a ballistic MOSFET with a silicon body thickness t=1.36nm.

The relative current increase  $(I(V_{DS})-I_0(V_{DS}))/I_0(V_{DS})$  as function of the drain-source voltage is shown in Fig.4b. For small shear strain the current enhancement does not depend on bias. For high strain a higher current enhancement is observed (Fig.4b). The reason is the strain-induced energy splitting between the unprimed subbands. Because of this splitting the density of states decreases prompting an increase of the chemical potential and current at the fixed gate voltage. At high stress the increase of  $E_F$  is larger than in the linear regime guaranteeing a larger drive current enhancement.

#### 5. Conclusion

A rigorous analysis of the subband structure in thin silicon films allows evaluating the mobility enhancement in strained MOSFETs with ultra-thin silicon films. The decrease of the transport effective mass and additional splitting between the unprimed subbands induced by shear strain is the reason for current enhancement even in ultra-thin (001) silicon films. This mobility and drive current increase combined with the improved channel control makes multi-gate MOSFETs based on thin films or silicon fins preeminent candidates for the 16nm technology node and beyond.

# **Acknowledgments**

This work has been partly supported by the European Research Council through the grant #247056 MOSILSPIN.

#### References

- [1]. B.Doris, M.Ieong, T.Kanarsky, *et al.*: "Extreme Scaling with Ultra-Thin Si Channel MOSFETs." In *IEDM Techn. Dig.* 2002, pp.267–270.

- [2]. P.Packan, S.Akbar, M.Armstrong, *et al.*: "High Performance 32nm Logic Technology Featuring 2<sup>nd</sup> Generation High-k + Metal Gate Transistors." In *IEDM Techn. Dig.* 2009, pp.1–4.

- [3]. K. Mistry, C.Allen, C.Auth, *et al.*: "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-Free Packaging." In *IEDM Techn. Dig.* 2007, pp.247–250.

- [4]. M.K.Hudait, G.Dewey, S.Datta, *et al.*: "Heterogeneous Integration of Enhancement Mode In0.7Ga 0.3As Quantum Well Transistor on Silicon Substrate Using Thin (≤2µm) Composite Buffer Architecture for High-Speed and Low-Voltage (0.5V) Logic Applications." In *IEDM Techn. Dig.* 2007, pp.625–628.

- [5]. B.-Y.Nguyen, C. Mazure, D. Delprat, *et al.*: "Overview of FDSOI Technology from Substrate to Device." In *ISDRS Techn. Dig.* 2009, pp.1-2.

- [6]. J.Welser, J.L. Hoyt, J.F. Gibbons: "Electron Mobility Enhancement in Strained-Sin-Type Metal-Oxide-Semiconductor Field-Effect Transistors." *IEEE Electron Device Lett.* **15**, 1994, pp.100–102.

- [7]. E.X.Wang, P.Matagne, L.Shifren, *et al.*: "Physics of Hole Transport in Strained Silicon MOSFET Inversion Layers."

- *IEEE Trans.Electron Devices* **53**, 2006, pp.1840–1851.

- [8]. G.Sun, Y.Sun, T.Nishida, S.E.Thompson: "Hole Mobility in Silicon Inversion Layers: Stress and Surface Orientation." *J.Appl.Phys.* **102**, 2007, 084501.

- [9]. M.V.Fischetti, S.E.Laux: "Band Structure, Deformation Potentials, and Carrier Mobility in Si, Ge, and SiGe Alloys." *J.Appl.Phys.* **80**, 1996, pp.2234–2252.

- [10]. Q.Ouyang, Min Yang, J.Holt, *et al.*: "Investigation of CMOS Devices with Embedded SiGe Source/Drain on Hybrid Orientation Substrates." In *Intl. Symp. on VLSI Technology*, 2005, pp.28–29.

- [11]. K.-W.Ang, K.J.Chui, V.Bliznetsov, *et al.*: "Enhanced Performance in 50nm n-MOSFETs with Silicon-Carbon Source/Drain Regions." *In IEDM Techn. Dig.* 2004, pp.1069–1071.

- [12]. S.Pidin, T.Mori, K.Inoue, *et al.*: "A Novel Strain Enhanced CMOS Architecture Using Selectively Deposited High Tensile and High Compressive Silicon Nitride Films." In *IEDM Techn. Dig.* 2004, pp.213–216.

- [13]. C.D.Sheraw, M.Yang, D.M.Fried, *et al.*: "Dual Stress Liner Enhancement in Hybrid Orientation Technology." In *Int. Symp. On VLSI Technology* 2005, pp.12–13.

- [14]. R.Arghavani, L.Xia, H.M.Saad, *et al.*: "A Reliable and Manufacturable Method to Induce a Stress of >1GPa on a p-Channel MOSFET in High Volume Manufacturing." *IEEE Electron Device Lett.* **27**, 2006, pp. 114–116.

- [15]. M.Yang, V.W.C.Chang K.K.Chang, *et al.*: "Hybrid-Orientation Technology (HOT): Opportunities and Challenges."

- *IEEE Trans.Electron Devices* **53**, 2006, pp. 965–978.

- [16]. J.M.Luttinger and W.Kohn: "Motion of Electrons and Holes in Perturbed Periodic Fields." *Phys.Rev.* **97**, 1955, pp. 869–883.

- [17]. G.L.Bir and G.E.Pikus: *Symmetry and Strain-Induced Effects in Semiconductors*. J.Wiley & Sons, NewYork –Toronto, 1974.

- [18]. M.V.Fischetti, Z.Ren, P.M.Solomon, *et al.*: "Six-Band **k·p** Calculation of the Hole Mobility in Silicon Inversion Layers: Dependence on Surface Orientation, Strain, and Silicon Thickness." *J.Appl.Phys.* **94**, 2003, pp.1079–1095.

- [19]. A.T.Pham, C.Jungemann, B.Meinerzhagen: "Deterministic Multisubband Device Simulations for Strained Double Gate PMOSFETs Including Magnetotransport." In *IEDM Techn. Dig.* 2008, pp.895–898.

- [20]. T.Ando, A.B.Fowler, F.Stern: "Electronic Properties of Two-Dimensional Systems." *Rev.Mod.Phys.* **54**, 1982, pp.437–672.

- [21]. M.Rieger, P.Vogl: "Electronic-Band Parameters in Strained Si<sub>1-x</sub>Ge<sub>x</sub> Alloys on Si<sub>1-y</sub>Ge<sub>y</sub> Substrates." *Phys.Rev. B* **48**, 1993, pp.14276–14287.

- [22]. M.V.Fischetti, F.Gámiz, W.Hänsch: "On the Enhanced Electron Mobility in Strained-Silicon Inversion Layers." *J.Appl.Phys.* **92**, 2002, pp.7320–7324.

- [23]. S.I.Takagi, J.L.Hoyt, J.J.Welser, J.F.Gibbons: "Comparative Study of Phonon-Limited Mobility of Two-Dimensional Electrons in Strained and Unstrained Si Metal-Oxide-Semiconductor Field-Effect Transistors." *J.Appl.Phys.* **80**, 1996, pp. 1567–1577.

- [24]. K.Uchida, T.Krishnamohan, K.C.Saraswat, Y.Nishi: "Physical Mechanisms of Electron Mobility Enhancement in Uniaxial Stressed MOSFETs and Impact of Uniaxial Stress Engineering in Ballistic Regime." In *IEDM Techn. Dig.* 2005, pp. 129–132.

- [25]. D.Esseni and P.Palestri: "Linear Combination of Bulk Bands Method for Investigating the Low-Dimensional Electron Gas in Nanostructured Devices." *Phys.Rev. B* **72**, 2005, 165342.

- [26]. V.Sverdlov, D.Esseni, O.Baumgartner, *et al.*: "The Linear Combination of Bulk Bands-Method for Electron and Hole Subband Calculations in Strained Silicon Films and Surface Layers." In *Proc. IWCE*, 2009, pp. 49–53.

- [27]. D.Rideau, M.Feraille, L.Ciampolini, *et al.*: "Strained Si, Ge, and Si<sub>1-x</sub>Ge<sub>x</sub> Alloys Modeled with a First-Principles-Optimized Full-Zone **k·p** Method." *Phys.Rev. B* **74**, 2006, 195208.

- [28]. J.C.Hensel, H.Hasegawa, M.Nakayama: "Cyclotron Resonance in Uniaxially Stressed Silicon. II. Nature of the Covalent Bond." *Phys.Rev.* **138**, 1965, pp.A225–A238.

- [29]. E.Ungersboeck, S.Dhar, G.Karlowatz, *et al.*: "The Effect of General Strain on Band Structure and Electron Mobility of Silicon."

- *IEEE Trans.Electron Devices* **54**, 2007, pp.2183–2190.

- [30]. V.Sverdlov and S.Selberherr: "Electron Subband Structure and Controlled Valley Splitting in Silicon Thin-Body SOI FETs: Two-Band **k·p** Theory and Beyond." *Solid-State Electron.* **52**, 2008, pp.1861–1866.

- [31]. R.Kotlyar, M. D. Giles, S. Cea, *et al*: "Modeling the Effects of Applied Stress and Wafer Orientation in Silicon Devices: From Long Channel Mobility Physics to Short Channel Performance." *J.Comp.Electron.* **8**, 2008, pp.110-123.