# *In Situ* Poly Heater—A Reliable Tool for Performing Fast and Defined Temperature Switches on Chip

Thomas Aichinger, Michael Nelhiebel, Sascha Einspieler, and Tibor Grasser, Senior Member, IEEE

Abstract—In this paper, we discuss the calibration procedure and performance of the poly-heater measurement technique for device characterization and reliability issues. We put a particular emphasis on the accessible temperature range, the heating and cooling dynamics, as well as on the impact of temperature gradient between the heater, device, and thermo chuck. In this context, the poly-heater technique provides a reliable solution for fast and arbitrary temperature switches and offers the possibility to reach device temperatures that are far beyond the operating range of conventional thermo-chuck systems.

Index Terms—In situ heating, NBTI, poly heater, temperature switches.

# I. INTRODUCTION

POLY RESISTORS surrounding a silicon device can be used to perform fact in a silicon. used to perform fast in situ heating on a single device at the wafer level, which is commonly applied in time-critical wafer-level reliability monitoring [1]–[5]. In this context, the main advantage of the poly heater is that it provides an elevated stress temperature without the limitations associated with a conventional heating system like a thermo chuck. Although this is a valuable feature, it does not even begin to explore the multitude of possibilities that one finds in a more scientific use. For example, we have recently extended the poly-heater tool in a sophisticated way in order to study the NBTI recovery of identically stressed devices at various recovery temperatures [6]. Furthermore, the characteristics and response of NBTIinduced interface and oxide defects have been investigated by performing ultrafast temperature switches directly during recovery [7]. By correct calibration and automation of the poly-heater-device system, the temperature becomes a quasi-

Manuscript received July 27, 2009; revised September 7, 2009, September 15, 2009, and September 21, 2009. First published October 20, 2009; current version published March 5, 2010. This work was supported in part by the Federal Ministry of Economics and Labour of the Republic of Austria under Contract 98.362/0112-C1/10/2005 and in part by the Carinthian Economic Promotion Fund (KWF) under Contract 98.362/0112-C1/10/2005.

T. Aichinger is with the Kompetenzzentrum für Automobil- und Industrie-Elektronik, 9524 Villach, Austria. He is also with Infineon Technologies Austria, 9500 Villach, Austria, and with the Christian Doppler Laboratory for TCAD in Microelectronics, Institute for Microelectronics, TU Vienna, 1040 Vienna, Austria (e-mail: thomas.aichinger@k-ai.at).

M. Nelhiebel is with Infineon Technologies Austria, 9500 Villach, Austria (e-mail: michael.nelhiebel@infineon.com).

S. Einspieler is with the Kompetenzzentrum Automobil- und Industrie-Elektronik, 9524 Villach, Austria, and also with the Carinthia University of Applied Sciences, 9524 Villach, Austria (e-mail: sascha.einspieler@k-ai.at).

T. Grasser is with the Christian Doppler Laboratory for TCAD in Microelectronics, Institute for Microelectronics, TU Vienna, 1040 Vienna, Austria (e-mail: grasser@iue.tuwien.ac.at).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TDMR.2009.2033467

arbitrary experimental parameter, which can be switched easily by more than  $\pm 200~\rm K$  within a couple of seconds. In this context, the ability of degradation quenching has been identified and elaborated in [6]. With degradation quenching, we understand a method that strictly separates stress and analysis temperatures. In the case of NBTI, this means that we stress the device at an elevated stress temperature while performing defect profiling and recovery analysis at a much lower relaxation temperature. This approach enables us, for example, to compare charge-pumping (CP) currents and  $V_{\rm TH}$  shifts of devices stressed at different stress temperatures always at the same recovery temperature.

During cooling, we may impede recovery by keeping the stress bias applied until the lower analysis temperature has stabilized. On the other hand, additional degradation during cooling is impeded as well because the temperature drop is very fast as we switch off the heater. In fact, additional stress during cooling can be neglected safely, provided that the cooling time is much shorter than the actual stress time before. Degradation quenching enables us to bring identically processed devices to the same degradation level, conserve the degradation level during cooling, and later characterize the device at an arbitrary recovery temperature. For such an application, conventional thermo-chuck systems are unsuitable because they are slow and their heating/cooling durations depend strongly on difference to the target temperature. We further remark that a mandatory requirement for keeping the junction biases applied during the temperature switch is that we do not lose probe-needle contact during the temperature switch. Because heating and cooling a wafer on a thermo chuck involve considerable thermal expansion, this demand cannot be fulfilled over a wide temperature range without continuous manual needle adjustment. As opposed to heating the whole wafer on the thermo chuck, in situ heating by poly heaters is very local. Hence, there is no thermal expansion of needles and pads, which saves us from losing mechanical contact during the temperature switch.

Once calibrated and implemented in software, the polyheater feature opens up unprecedented possibilities for device characterization and reliability testing. Its application potential is thereby way beyond the scope of NBTI characterization. Nowadays, the concept of *in situ* heating of small-area structures by implanted poly wires has been taken up also, for instance, for active thermocycling [8] or to perform on-chip high-temperature annealing of irradiated PMOS dosimeters [9].

A common problem of *in situ* heating can be found in the fact that the device, which we want to heat up, is, in most cases, a distance away from the actual heating source. Consequently, the poly wires are always hotter than the tested object itself, which

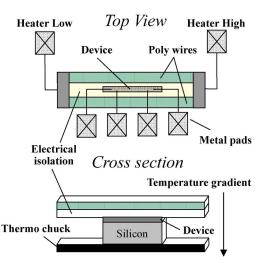

Fig. 1. Schematic illustration of a poly-heater-device system placed on a thermo chuck. Electrically isolated poly wires surround the silicon device. When power is applied to the wires, the dissociated heat elevates the temperature within the subjacent electrically active device regions. Due to the lower chuck temperature, a temperature gradient and a time delay between the heater and wafer bottom arise.

results in a temperature gradient between the radiator, device, and ambient. In particular, the distance between the poly-heater wires and the active areas of the device must be large enough to prevent a direct current flow between the separate components. However, the larger the distance between the heater and the device, the lower the thermal resistance of the system and the more power has to be applied to the wires in order to generate a certain elevated device temperature. Furthermore, the time delay for restoring thermal equilibrium must also be taken into account as we switch the heater on or off abruptly. The farther the heater away from the device, the longer it takes to restore thermal equilibrium. Thus, in order to find the optimal distance between the heating source and the active device for a particular application, the previously specified points have to be considered carefully.

The situation for an active transistor surrounded by a polyheater system on top and placed on a thermo chuck below is shown in Fig. 1. Depending on the ground temperature of the thermo chuck, a certain power has to be applied to the heater in order to reach a specified device temperature. From the layout point of view, the heater should overlap the device considerably in order to guarantee a homogeneous temperature distribution over the whole active area. The theoretical determination of poly-heater and device temperatures as we apply a certain power to the heater is very difficult [10] because considerable simplifications are required due to the fact that various back-end layers and materials usually have nonlinear thermal conductivities [11].

In the following paragraphs, we present an experimental procedure to determine the exact power supply that is necessary to bring an active transistor to a certain device temperature. Thereby, we evaluate both heater and device temperatures, which enables us to estimate the temperature gradient between the poly wires and device. Furthermore, we extract the transient heating and cooling characteristics for different target temperatures and discuss the effects that may delay the restoration of thermal equilibrium and destabilize an adjusted temperature.

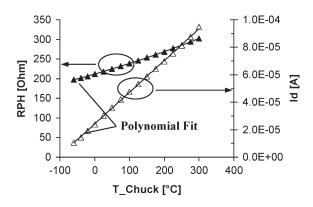

Fig. 2. Development of (full triangles) the poly resistance  $R_{\rm PH}$  and (open triangles) the drain current  $I_d$  as a function of chuck temperature.  $R_{\rm PH}$  is characteristic for the poly-wire temperature, while  $I_d$  reflects the interface temperature of the active device.

#### II. HEATER VERSUS DEVICE TEMPERATURES

For the extraction of poly-heater and device temperatures when a power is applied, we call on an appropriate temperature-dependent parameter of the material. In the case of a highly doped poly-silicon wire, the temperature-dependent electric resistance  $(R_{\rm PH})$  would be such a factor. In the case of a MOS transistor, the current through the source–bulk diode or the source–drain current itself around the threshold voltage of the device can be used as a thermometer. For reliability issues, we prefer to use the source–drain current  $(I_d)$  because it directly reflects the temperature of the interface between the silicon substrate and the gate oxide. This interface is of major importance because most studies suggest this region to be the location of concern for NBTI, TDDB, and hot-carrier degradation.

For the initial calibration, we heat up the wafer from -60 °C to 300 °C on the thermo chuck and record the poly resistance  $(R_{\rm PH})$  and the drain current  $(I_d)$  of our PMOS device at selected temperatures (cf. Fig. 2). Note that the sense currents and voltages must be chosen carefully in order to prevent selfheating during measurement. Within the scanned temperature range, the increase of poly resistance and drain current can be fitted very well by a polynomial of first or second order. From a physical point of view, the increase in poly resistance can be explained by a reduction of carrier mobility due to enhanced lattice scattering at higher temperatures, while the increase in drain current originates from an enhancement of the concentration of thermally activated inversion carriers. Having determined the coefficients of the polynomial fit, we can later easily calculate the poly and device temperatures from  $R_{\rm PH}$  and  $I_d$ , respectively, when power is applied.

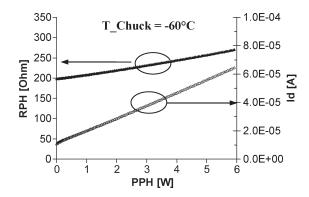

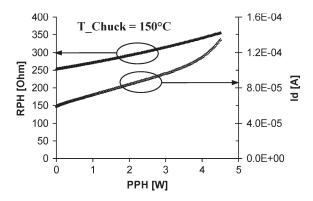

In Fig. 3, the poly resistance and drain current are shown as a function of power supply  $(P_{\rm PH})$ . In this example, the chuck temperature was -60 °C. If we apply 0 W  $(P_{\rm PH}=0~{\rm W})$ , the resistance and drain current correspond exactly to their values extracted for -60 °C in Fig. 2. As we increase the power supply from 0 to 6 W, the resistance and drain current grow simultaneously. In order to provide enough time for restoring equilibrium, the steps in power supply must be moderate. In the analysis, we can later convert  $R_{\rm PH}$   $(P_{\rm PH})$  into a poly temperature  $(T_{\rm PH})$  and  $I_d$   $(P_{\rm PH})$  into a device temperature  $(T_{\rm DV})$ . The extracted poly and device temperatures

Fig. 3. (Full triangles) Poly resistance  $R_{\rm PH}$  and (open triangles) drain current  $I_d$  as we increase the heater power  $P_{\rm PH}$ . The chuck temperature was  $-60~^{\circ}{\rm C}$  in this example. The increase in heater power causes a characteristic increase in poly and device temperatures.

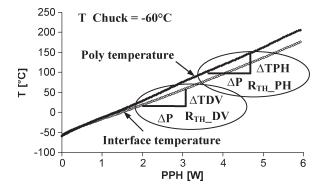

Fig. 4. (Full diamonds) Extracted poly temperature and (open diamonds) interface temperature as we increase the heater power. The chuck was at  $-60~^{\circ}\mathrm{C}$ . As we increase the heater power, the poly and device temperatures slightly drift apart due to the vertical temperature gradient. Thermal resistance  $R_{\mathrm{TH}}$  is given by slope  $\Delta T$  versus  $\Delta P$ .

as a function of power supply are shown in Fig. 4. As can be seen, if we apply a power of 6 W at a chuck temperature of  $-60~^{\circ}\mathrm{C}$ , we can reach a device temperature of approximately 175  $^{\circ}\mathrm{C}$ . This corresponds to a maximum temperature gap of  $\Delta T_{\mathrm{DV}}=235~\mathrm{K}$ . The correlation between the heater power and the corresponding temperature gap is naturally dependent on the particular poly design. We further note that the higher the power input, the further the poly and device temperatures drift apart. For example, at a poly temperature of 150  $^{\circ}\mathrm{C}$ , the device temperature is just 125  $^{\circ}\mathrm{C}$ . This is due to the vertical temperature gradient between the heater and the thermo chuck (cf. Fig. 1). We remark that there is a linear relationship between temperature and power supply. From the slope  $(\Delta T/\Delta P)$ , we can determine the thermal resistances  $(R_{\mathrm{TH}}$ 's) at -60- $^{\circ}\mathrm{C}$  ambient temperature.

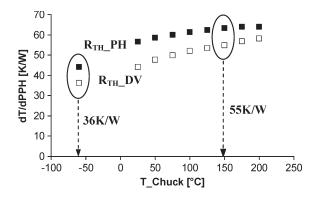

In Fig. 5, the thermal resistances  $R_{\rm TH}$ \_PH and  $R_{\rm TH}$ \_DV of our particular design have been elaborated for different chuck temperatures. Obviously,  $R_{\rm TH}$  increases as ambient temperature increases. This means that we have to spend less power at higher ambient temperatures in order to bridge the same temperature range  $\Delta T$ . The increase in  $R_{\rm TH}$  can be explained by the nonlinear thermal conductivity of silicon. In fact, thermal conductivity decreases as temperature increases [10]–[12]. Consequently, the dissipated heat by the poly wires is distributed to a smaller area. Due to the narrower concen-

Fig. 5. Thermal resistances of (full squares) the poly heater ( $R_{\rm TH}$ \_PH) and (open squares) the device interface ( $R_{\rm TH}$ \_DV) extracted for different chuck temperatures. The higher the chuck temperature, the steeper the temperature increase with heater power.  $R_{\rm TH}$ \_DV is lower than  $R_{\rm TH}$ \_Poly due to the vertical temperature gradient.

trated power dissipation, poly and device heating becomes more efficient at higher temperatures. This phenomenon also causes  $R_{\rm TH}$ \_PH and  $R_{\rm TH}$ \_DV to come closer together at higher ambient temperatures.

In many cases, one is not interested in the thermal resistance and heating characteristics, making the calibration procedure for a single target temperature much less laborious. In principle, it is sufficient to determine one single target drain current at a certain target temperature. Therefore, we heat up the thermo chuck to the desired temperature and record the corresponding target current at threshold voltage. When we later (at a lower chuck temperature) want to determine the correct power supply that is necessary to reach this elevated target temperature, we simply increase the power supply incrementally and measure the drain current in parallel. When the measured drain current corresponds exactly to its target value, we have determined the required power supply.

# III. MAXIMUM ACCESSIBLE TEMPERATURE RANGE

A remarkable application of the poly-heater technique can be found in the ability of reaching device temperatures far beyond conventional thermo-chuck ranges. Such an ultrahigh target temperature can be reached by providing additional heating power at the maximum temperature range that is accessible by the thermo chuck. This feature enables us to determine, for example, activation energies of NBTI-induced defects in a much wider temperature range than that provided by the thermo chuck. The high stress temperature during NBTI is then generated by the heater. Before poststress characterization, we perform degradation quenching and turn off the heater. This enables us to characterize devices stressed at a high temperature within a minimum time delay at a much lower characterization temperature. We remark that a low characterization temperature is essentially required for NBTI monitoring because it improves the accessible energy range and the resolution of transfer curve analysis ( $I_d$ - $V_q$  sweeps), C-V characteristics, and CP measurements. Previous approaches by Jeppson and Svensson [13] have used the thermo chuck itself for cooling the device from stress temperature to characterization temperature. However,

Fig. 6. (Full triangles) Poly resistance  $R_{\rm PH}$  and (open triangles) drain current  $I_d$  as we increase the heater power at a chuck temperature of 150 °C. While poly resistance  $R_{\rm PH}$  still increases regularly in the high-temperature regime, the drain current begins to deviate as the silicon substrate becomes intrinsic ( $T_{\rm L}$ Int > 300 °C). In the intrinsic regime, drain current  $I_d$  no longer serves as a reliable thermometer.

this procedure is superslow and does not allow one to keep the junction biases applied during the temperature switch.

If we want to calibrate the heater in the high-temperature regime, more effort is needed to obtain a reasonable correlation between heater power and device temperature. This is mainly due to the fact that we cannot determine a target drain current in a temperature regime that is not accessible by the thermo chuck. Furthermore, previously established thermometers, like the drain current around  $V_{\rm TH}$ , change their temperature-dependent characteristics as the semiconductor becomes intrinsic.

The high-temperature situation is shown in Fig. 6. We have performed the same experiment as in Fig. 3 but, this time, at a chuck temperature of 150 °C. As we increase the power supply at an ambient temperature of 150 °C, the heater resistance  $(R_{\rm PH})$  and drain current  $(I_d)$  initially show a similar behavior as that shown in Fig. 3. Both parameters ( $R_{PH}$  and  $I_d$ ) increase regularly until we reach a power supply of 3 W. According to the thermal resistance of 55 K/W (cf. Fig. 5), the 3 W applied at a ground temperature of 150 °C should elevate the device temperature to approximately 315 °C. Beyond this temperature range, the doped silicon substrate becomes intrinsic, which changes the current-voltage characteristics and temperature development of the drain current significantly. As can be seen in Fig. 6, between 3 and 5 W, the drain current begins to deviate from its regular temperature relationship (cf. Fig. 2) and can therefore no longer be used as a reliable thermometer. On the other hand, the poly resistance abides by its regular development, which still validates  $R_{\rm PH}$  for poly-temperature

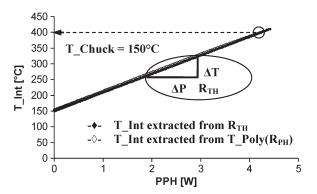

In Fig. 7, we have determined the interface temperature of the device for an increasing power supply in two different ways. The first way is simply linked to the thermal resistance evaluated in Fig. 5. According to the  $R_{\rm TH}$ \_Int extracted for 150 °C, the device temperature should increase by 55 K/W. We can use this result to calculate the device temperature in a straightforward manner. The second way is a little bit trickier. From the poly resistance, which still follows its regular development in the high-temperature regime, we can calculate first the poly temperature as a function of power supply. In the second step, the poly temperature can be used to draw

Fig. 7. Interface temperature  $(T_{\rm Int})$  versus power supply in the high-temperature regime. (Open diamonds) Extracted from the poly resistance and poly temperature. (Full diamonds) Extracted from thermal resistance  $R_{\rm TH}_{\rm Int}$ . Although both techniques are based on independent calculations, they yield similar results for  $T_{\rm Int}$  ( $P_{\rm PH}$ ). At a chuck temperature of 150 °C, interface temperatures up to 400 °C (4.2 W) can be reached by the poly heater.

conclusions on the device temperature by making use of the direct relationship between poly and device temperatures. The procedure is similar as that shown in Fig. 4 but, this time, for a chuck temperature of 150 °C. As can be seen in Fig. 7, the results of both techniques perfectly coincide. In particular, at a chuck temperature of 150 °C, we are able to reach device temperatures up to 400 °C, which is far beyond the scope of most conventional thermo-chuck systems. At the moment, we turn off the heater, and the temperature drops back to 150 °C almost immediately. The detailed heating and cooling dynamics of the heater–device system will be demonstrated in the next paragraph.

# IV. HEATING AND COOLING DYNAMICS

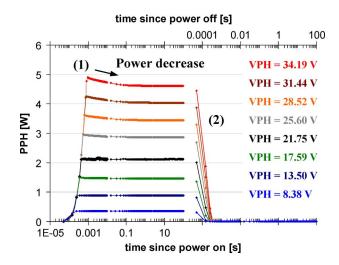

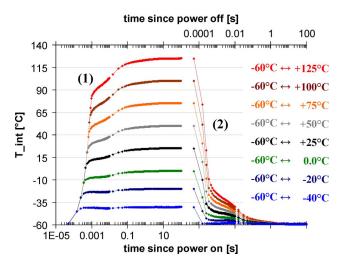

In this paragraph, we elaborate on the time-dependent heating and cooling dynamics of the device as a heating voltage or power is applied or removed, respectively. The chuck (ambient) temperature was -60 °C during our experiments. By applying a certain heating voltage to the poly wires, the device temperature quickly elevates and stabilizes after a couple of seconds. On the other hand, if we remove the heating voltage, the device cools down immediately. In order to determine the exact heating voltage, which is necessary to reach a certain device temperature, a calibration procedure has been done in advance. During this calibration procedure, we have incrementally increased the heating voltage/power until the measured drain current at threshold voltage corresponded exactly to its target value evaluated previously at a higher chuck temperature. The output of this initial calibration was eight different heating voltages, which are necessary to heat up the device from -60 °C to -40 °C/-20 °C/0 °C/25 °C/50 °C/75 °C/100 °C/125 °C.

In the experiments shown in Fig. 8, we abruptly apply a heating voltage while recording in parallel the heater current for 100 s. After this 100-s heating period, we remove the voltage while recording again the heater current in parallel for another 100 s. From the heating voltage and current, we calculate the time-dependent power dissipation of the heater.

As can be seen in Fig. 8, as we turn the heater on, it takes up to 1 ms until we reach the maximum power dissipation.

AICHINGER et al.: IN SITU POLY HEATER 7

Fig. 8. Heating power as we turn the heater voltage abruptly (1) on or (2) off. During the heater calibration, we have determined specific voltages that are necessary to reach certain device temperatures. At the moment, we turn the voltage (1) on or (2) off, and we record the heating current in parallel to calculate  $P_{\rm PH}$ .

Fig. 9. Heating and cooling characteristics as we turn the heater power abruptly (1) on or (2) off in order to reach various interface temperatures. The chuck temperature was  $-60\,^{\circ}\mathrm{C}$ . The chuck–device–heater system needs a couple of seconds to restore thermal equilibrium. At the very beginning of the heating and cooling procedures, we therefore observe a shoulder in the interface temperature development.

This delay time is larger if the temperature gap is higher, and it is mainly limited by the finite speed of the voltage source. Note that, using our particular design, heating voltages up to 34 V are required in order to overcome a temperature gap of 185 °C (-60 °C  $\rightarrow +125$  °C). After the voltage source has stabilized (>1 ms), the heater power tends to reduce slightly for a couple of seconds. This is due to the fact that some time is needed to restore thermal equilibrium between the heater, wafer, and chuck. Consequently, the initial power decrease is higher if the temperature gap is larger between the heater and chuck.

As we turn the heater off, the heater power vanishes quasi immediately within 1 ms. Again, this 1 ms originates from the finite speed of the voltage source.

In the experiments shown in Fig. 9, we perform the same measurement sequence as in Fig. 8 but record this time the

device drain current at  $V_{\rm TH}$  as a representative for the interface temperature of the device. By using the results of Fig. 2, we calculate the interface temperature  $(T_{\rm int})$  from  $I_d$ .

As can be seen in Fig. 9, as we turn the heater on abruptly, it takes up to 10 s until the device temperature has stabilized at its calibrated value. The larger the temperature gap, the longer it takes to reach the target temperature. This larger time delay originates from the finite time interval that is necessary to restore thermal equilibrium a distance away from the actual heating source. The shoulder that is visible in the development of  $T_{\rm int}$  during heating originates from the power decrease shown in Fig. 8. We remark that, although the heater power reaches a maximum 1 ms after turning the heater voltage on, the device temperature does never exceed its target value due to the delayed thermal coupling between the heater and device. This is an important aspect because we do not want to subject the device to an elevated prestress at the moment we turn the heater on.

As we turn the heater off, the situation is similar as that during heating. It takes a couple of seconds until the excess heat, which is generated by the poly heater, can be removed by the thermo chuck.

Following Fig. 9, we come to the conclusion that, at  $-60^{\circ}$ C ambient temperature, any temperature switch up to  $\pm 200$  K can be executed safely within a time interval of 10 s maximum. In fact, it takes approximately 0.1 s to reach the target temperature by 3% and 1 s to obtain a 1% accuracy, and after 10 s, the target temperature is adjusted by 0.1%, which corresponds to the measurement resolution as well.

# V. CONCLUSION

In this paper, we have demonstrated and summarized the features and performance of the in situ poly-heater measurement technique. We have elaborated in detail the temperature calibration procedure for determining the poly temperature and device temperature for different ambient temperatures and power supplies. The thermal resistances of the poly heater and device were found to be dependent on ambient temperature, which is consistent with the nonlinear thermal conductivity of silicon. We have shown that a temperature gap of more than 200 K can be bridged by the additional power supply provided by the poly heater. In particular, the ability of reaching device temperatures that are far beyond conventional thermochuck ranges and the principle of degradation quenching have been pointed out. A thorough study on the heating and cooling dynamics of the device has revealed that a maximum time of 10 s is needed to switch the temperature within an interval of  $\pm 200$  K and restore thermal equilibrium. Equipped with this feature, the poly-heater tool exhibits a remarkable and unique tool for device reliability testing and characterization purposes.

# ACKNOWLEDGMENT

The authors would like to thank S. Baier, N. Krischke, and T. Ostermann (Infineon Technologies) for the support in the poly-heater design and layouting process.

#### REFERENCES

- [1] W. Muth and W. Walter, "Bias temperature instability assessment of n- and p-channel MOS transistors using a polysilicon resistive heated scribe lane test structure," *Microelectron. Reliab.*, vol. 44, no. 8, pp. 1251– 1262, Aug. 2004.

- [2] C. Schluender, R.-P. Vollertsen, W. Gustin, and H. Reisinger, "A reliable and accurate approach to assess NBTI behavior of state-of-the-art pMOSFETs with fast-WLR," in *Proc. 37th ESSDERC*, 2007, pp. 131–134.

- [3] T.-K. Kang, C.-S. Wang, and K.-C. Su, "Self-heating p-channel metal-oxide-semiconductor field-effect transistors for reliability monitoring of negative-bias temperature instability," *Jpn. J. Appl. Phys.*, vol. 46, no. 12, pp. 7639–7642, Dec. 2007.

- [4] C.-S. Wang, W.-C. Chang, W.-S. Ke, and K.-C. Su, "Ultra-fast negative bias temperature instability monitoring and end-of-life projection," in *Proc. IEEE IIRW Final Rep.*, 2006, pp. 136–138.

- [5] C. S. Wang, W. C. Chang, W. S. Ke, C. T. Chiang, C. F. Lee, and K. C. Su, "Characterization of embedded poly-heater pMOSFETs and its application on in-line wafer level NBTI monitor," in *Proc. Int. Conf.* SSDM, 2005, pp. 580–581.

- [6] T. Aichinger, M. Nelhiebel, and T. Grasser, "On the temperature dependence of NBTI recovery," *Microelectron. Reliab.*, vol. 48, no. 8/9, pp. 1178–1184, Aug./Sep. 2008.

- [7] T. Aichinger, M. Nelhiebel, and T. Grasser, "Unambiguous identification of the NBTI recovery mechanism using ultra-fast temperature changes," in *Proc. IEEE IRPS*, 2009, pp. 2–7.

- [8] H. Köck, V. Košel, C. Djelassi, M. Glavanovics, and D. Pogany, "IR thermography and FEM simulation analysis of on-chip temperature during thermal-cycling power-metal reliability testing using in situ heated structures," in *Microelectron. Reliab.*, vol. 49, no. 9-11, pp. 1132–1136, Aug. 2009.

- [9] A. Kelleher and W. Lane, "Investigation of on-chip high temperature annealing of PMOS dosimeters," *IEEE Trans. Nucl. Sci.*, vol. 43, no. 3, pp. 997–1001, Jun. 1996.

- [10] V. Košel, R. Sleik, and M. Glavanovics, "Transient non-linear thermal FEM simulation of smart power switches and verification by measurements," in *Proc. 13th Int. Workshop THERMINIC*, 2007, pp. 110–114.

- [11] A. Ramalingam, F. Liu, S. R. Nassif, and D. Z. Pan, "Accurate thermal analysis considering nonlinear thermal conductivity," in *Proc. ISQED*, 2006, pp. 643–649.

- [12] C. J. Glassbrenner and G. A. Slack, "Thermal conductivity of silicon and germanium from 3 °K to the melting point," *Phys. Rev.*, vol. 134, no. 4A, pp. 1058–1069, May 1964.

- [13] K. O. Jeppson and C. M. Svensson, "Negative bias stress of MOS devices at high electric fields and degradation of MNOS devices," *J. Appl. Phys.*, vol. 48, no. 5, pp. 2004–2014, May 1977.

Thomas Aichinger was born in Villach, Austria, in 1983. He received the Mag. rer. nat. degree in physics from the University of Graz, Graz, Austria, in 2007. He is currently working toward his Ph.D. degree at the Kompetenzzentrum für Automobil- und Industrie-Elektronik (KAI), Villach, in cooperation with the Christian Doppler Laboratory for TCAD in Microelectronics, Institute for Microelectronics, TU Vienna, Vienna.

During his diploma thesis, concerning the implementation of charge pumping in laboratory software

and hardware environments, he was with the Quality and Reliability Group, Infineon Technologies Austria.

Mr. Aichinger received the Best Paper Award at ESREF 2008.

Michael Nelhiebel was born in Vienna, Austria, in 1970. He received the M.S. degree in physics from Vienna University of Technology, Vienna, in 1995 and the Ph.D. degree in solid state physics from Ecole Centrale Paris, Châtenay-Malabry, France, in 1999. The focus of his Ph.D. dissertation was on interferometric effects in the chemical microanalysis of crystals using electron energy-loss spectrometry in the transmission electron microscope.

In 1999, he joined Infineon Technologies Austria, Villach, Austria, as a Reliability Engineer in silicon-

wafer production, where he is currently a Senior Staff Engineer with the Quality Department, Infineon Automotive Business Division, who is responsible for wafer- and package-technology-related product reliability in the development phase. He has coordinated the qualification that is necessary for the delivery release of major automotive technology platforms and participates in research activities of Infineon Technologies Austria targeting technology reliability.

Sascha Einspieler was born in Klagenfurt, Austria, in 1987. He received the Diploma degree in electrical and network engineering from the Federal Secondary College of Engineering, Klagenfurt, in May 2006. He is currently working toward the M.Sc. degree in mechatronics with the Carinthia University of Applied Sciences, Villach, Austria.

Since October 2008, he has been doing an internship with the Kompetenzzentrum Automobilund Industrie-Elektronik, Villach, Austria, concerning reliability testing and laboratory engineering.

**Tibor Grasser** (M'05–SM'05) was born in Vienna, Austria, in 1970. He received the Diplomingenieur degree in communications engineering, the Ph.D. degree in technical sciences, and the Venia Docendi in microelectronics from Technische Universität Wien, Vienna, in 1995, 1999, and 2002, respectively.

He is currently an Associate Professor with the Institute for Microelectronics, TU Vienna, Vienna, where he was appointed in 2003 as Head of the Christian Doppler Laboratory for TCAD in Microelectronics, an industry-funded research group em-

bedded in the Institute for Microelectronics. Since 1997, he has been heading the Minimos-NT Development Group, working on the successor of the highly successful MiniMOS program. He was a Visiting Research Engineer with Hitachi, Ltd., Tokyo, Japan, and the Alpha Development Group, Compaq Computer Corporation, Shrewsbury, MA. He is a coauthor or author of over 250 articles in scientific books, journals, and conferences proceedings and is the Editor of a book on advanced device simulation. His current scientific interests include circuit and device simulation, device modeling, and reliability issues.

Dr. Grasser has been involved in the program committees of several conferences, such as SISPAD, IWCE, ESSDERC, IRPS, IIRW, and ISDRS, and is a recipient of the Best Paper Awards at IRPS and ESREF. He was also the Chairman of SISPAD 2007.