# Analysis of the Threshold Voltage Turn-Around Effect in High-Voltage n-MOSFETs Due to Hot-Carrier Stress

I. Starkov★, H. Enichlmair\*, S. Tyaginov★, and T. Grasser★

\*Institute for Microelectronics, Vienna University of Technology, Gußhausstraße 27-29, A-1040 Wien, Austria \*Process Development and Implementation Department,

Austriamicrosystems AG, Tobelbader Straße 30, A-8141 Unterpremstaetten, Austria Email: starkov@iue.tuwien.ac.at

Abstract—The turn-around effect of the threshold voltage shift during hot-carrier stress has been investigated. Such a phenomenon is explained by the interplay between interface states and oxide traps, i.e. by the compensation of the rapidly created oxide charges by the more slowly created interface states. To prove this idea, a refined extraction scheme for the defect distribution from charge-pumping measurements has been employed. The obtained results are in a good agreement with the findings of our physics-based model of hot-carrier degradation. This approach considers not only damage produced by channel electrons but also by secondary generated channel holes. Although the contribution of the holes to the total defect creation is smaller compared to that of electrons, their impact on the threshold voltage shift is comparable with the electronic contribution. The reason behind this trend is that hole-induced traps are shifted towards the source, thereby more severely affecting the device behavior.

Index Terms—threshold voltage, turn-around effect, hot-carrier degradation, worst-case conditions, Monte-Carlo, interface states, MOSFET, TCAD

#### I. INTRODUCTION

It is commonly accepted that processes related to trapping/detrapping in the oxide bulk play a crucial role in the bias temperature instability (BTI) [1,2]. Since BTI and hotcarrier degradation (HCD) are believed to have a similar microscopic origin, one may expect that bulk oxide traps with the density  $N_{\rm ot}$  should also contribute to HCD. At the same time,  $N_{\rm ot}$  dominates the recoverable component of BTI [3] and, therefore, this suggests that HCD should also recover considerably. However, in n-MOSFETs hot-carrier degradation demonstrates rather small recovery over a wide range of temperatures [4,5]. The situation is made even more complicated because of turn-around effects sometimes observed during hot-carrier stresses [6, 7]. These turn-around effects are related to the partial compensation of the charge stored in the oxide traps by interface state trapping (characterized by the density  $N_{\rm it}$ ) [5,7]. However, a systematic study considering the evolution of the lateral defect profiles with stress time has not been carried out. The main scope of this work is to analyze the turn-around of the  $V_{

m th}$  shift observed during HC stress. This effect is explained by the interplay between  $N_{\mathrm{it}}$  and  $N_{\mathrm{ot}}$  contributions. This strategy is then supported by charge-pumping (CP) data and is linked to the physics-based

HCD model presented in our previous work [8]. The model considers not only channel electrons but also secondary holes generated by impact ionization due to hot electrons. These holes are then accelerated by the electric field back towards the source, thereby creating interface states shifted with respect to these created by electrons. Our modeling approach is based on the information how efficiently carriers trigger the bond dissociation process [8, 10–12]. We consider the superposition of single- and multiple-carrier mechanisms of Si-H bond-breakage (SC- and MC-processes) for both channel electrons and holes [8]. These mechanisms are controlled by the carrier acceleration integral (AI):

$$I_{\text{SC/MC}}^{(\text{e,h})} = \nu_{\text{SC/MC}}^{(\text{e,h})} \int_{E_{\text{th}}}^{\infty} f^{(\text{e,h})}(E)g(E)\sigma_{\text{SC/MC}}^{(\text{e,h})}(E)v(E)dE,$$

(1)

where f(E) is the carrier distribution function, g(E) the density-of-states, v(E) the carrier velocity and integration is performed over energy starting from the threshold for the Si-H bond dissociation reaction [9, 10]. The acceleration integral has the same functional form for SC- and MC-mechanisms and for both types of carriers.

#### II. EXPERIMENTAL SUPPORT

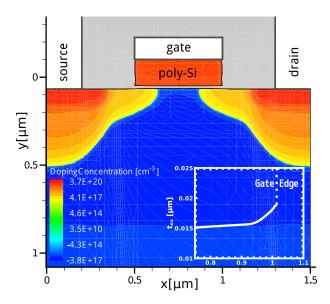

We use a high-voltage 5V n-MOSFET fabricated in a standard  $0.35\mu m$  CMOS process (Fig. 1). Devices with channel lengths of  $0.5\mu m$  were stressed at three combinations of drain and gate voltages:  $V_{ds}$ ,  $V_{gs}$ ={6.5,2.6}, {6.75,2.0} and  $\{6.25,2.0\}$ V and a temperature of T=40°C. For such a long-channel transistor the silicon-hydrogen bond-breakage process is dominantly triggered by the interaction of the bond with a solitary energetical carrier [4, 10]. This carrier is accelerated by the electric field up to energies sufficient enough to effectively rupture the bond in a single collision. Since impact ionization is a process which has an analogous activation nature, the concentration of electron-hole pairs generated by impact ionization may be used as a criterion of how hot the carriers are. As a consequence, one may judge the degradation intensity on the substrate current  $I_{\text{sub}}$ which is composed of majority carriers generated by impact ionization [4, 5, 13]. Usually, the  $I_{\text{sub}}$  maximum is observed

Fig. 1. The topology of the n-MOSFET with the net doping profile highlighted. Inset: the dependence of the oxide thickness vs. the lateral coordinate.

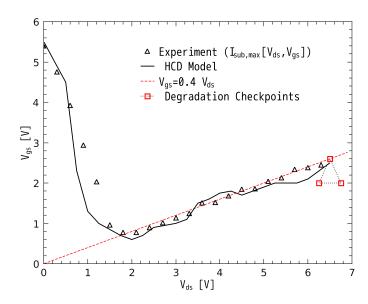

when  $V_{\rm gs} = (0.4 - 0.5)V_{\rm ds}$  [5] and, hence, it is assumed that the most severe degradation corresponds to these stress conditions. This idea is supported by Fig. 2 demonstrating both experimental and simulated (with our HCD model [10, 14]) dependences of worst case conditions (WCC) with respect to  $V_{\rm gs}$  and  $V_{\rm ds}$ . As we have discussed in [9, 15], for long-channel and/or high-voltage device the values of the acceleration integrals  $I_{

m MC}^{

m (e,h)}$  are rather high, thereby the dose of damage provided by the MC-component is homogeneously distributed over the lateral coordinate. In other words, the density of interface states generated by "colder" carriers does not vary with the lateral coordinate. Hence, the strong localization of HCD is related to the single-carrier process and the position of the  $N_{\rm it}$  peak is defined by the acceleration integral maximum. Very often other criteria are being used in the literature and among them are the electric field, carrier averaged energy, dynamic energy, and the most prolonged tails of the carrier energy distribution function. However, as we showed in [10], the  $N_{\rm it}$  peak only coincides with the AI peak and is shifted with respect to maxima of other quantities.

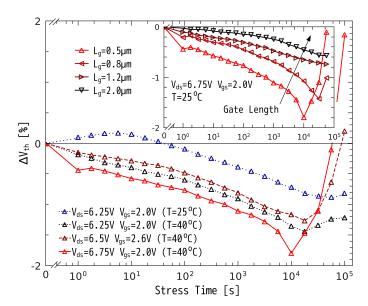

We have intentionally chosen stress voltages close to the WCC (see checkpoints in Fig. 2) in order to maximize the contribution of all the degradation effects. The threshold voltage was monitored up to  $10^5$ s. Fig. 3 demonstrates that first  $V_{\rm th}$  decreases due to hole trapping in the oxide bulk while after 10ks  $V_{\rm th}$  increases due to trapping of electrons by interface traps. To check these speculations, the CP technique with varying amplitude of the gate pulse [16, 17] has been employed to investigate the  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  distributions.

In our work we use a standard experimental scheme where the gate of the transistor is connected to a pulse generator and a small constant reverse bias is applied to the source and drain. We measured the substrate current at a gate pulse frequency of  $100 \mathrm{kHz}$ . We use  $V_{\mathrm{gl}} = 5 \mathrm{V}$  and increase  $V_{\mathrm{gh}}$  from -4 to  $2 \mathrm{V}$

Fig. 2. The gate voltage as a function of the drain voltage corresponding to the worst-case conditions. The noise pronounced in the simulated curve is related to stochastic nature of the transport kernel employed in our HCD model, see [14].

(varying high level technique) and  $V_{\rm gh}=3{\rm V}$  with decreasing  $V_{\rm gh}$  from 2 to -5V (varying base level technique) in 0.02V increments, where  $V_{\rm gl}$  and  $V_{\rm gh}$  are the base and the high levels of the gate pulse, respectively. Such a small voltage step is required in order to obtain sufficient spatial resolution.

#### III. INTERFACE AND OXIDE TRAP PROFILES EVOLUTION

### A. Local Oxide Capacitance

Most methods for the extraction of the lateral  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  profiles from CP data employ the oxide capacitance  $C_{\rm ox}$  [16–18] as a crucial parameter. Usually  $C_{\rm ox}$  is treated as a constant parameter of the device [17]:

$$C_{\rm ox} = \varepsilon_{\rm ox}/t_{\rm ox},$$

(2)

where  $t_{\rm ox}$  is the oxide thickness at the device center and  $\varepsilon_{\rm ox}$  the dielectric permittivity.

This approach is applicable only for transistors with a fixed oxide thickness and leads to erroneous results when  $t_{ox}$ varies along the interface. In fact, in such an approach the capacitor is considered ideal or, in other words, the electric field is assumed uniform. An extension of the technique to non-uniform  $t_{ox}(x)$  has been suggested in [16]. In practice, however, a substantial distortion occurs near the source/drain ends of the gate. Moreover, even in the case of a uniform thickness distribution such a scheme leads to spurious results due to fringing capacitance. The aforementioned simplification does not strongly affect the transistor characteristics. However, the electric field non-uniformity is of particular importance for the extraction of the interface state density profile after HC stress because  $N_{it}(x)$  peaks near the drain end of the gate where the capacitor non-ideality is most pronounced [4]. Additionally, Lee et al. [18] have already demonstrated that

Fig. 3. The shift of  $V_{\rm th}$  as a function of stress time at various voltages. Inset:  $\Delta V_{\rm th}$  measured for devices of the same architecture but different only in channel lengths stressed at  $V_{\rm ds}$ =6.75V and  $V_{\rm gs}$ =2.0V.

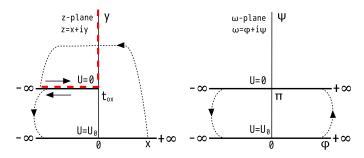

Fig. 4. The conformal transformation used to solve the gate/drain fringing problem. The complicated case of the corner gate form (red dashed line) was reduced just to a ray [19].

the coordinate dependence of the capacitance  $C_{\rm ox}(x)$  due to the fringing effect is essential.

The conformal-mapping method is most helpful for fringing electric fields in simple two-dimensional boundary problems (which is just our case) by transforming the boundary to a soluble form [20]. A series of simulations (described below) allow us to conclude that for the  $C_{\rm ox}(x)$  consideration a simplified structure can be used. Namely, the edge of the gate contact can be interpreted geometrically as a ray instead of more complicated corner variant. The problem with the coordinate system is shown in Fig. 4. The z plane is mapped into the w plane with the functional relationship between z and w described by

$$z = \frac{t_{\text{ox}}(x)}{\pi} (\omega + \exp(\omega))$$

(3)

The suggested conformal transformation is shown in Fig. 4 and reduces the original problem to the Laplace problem between two parallel infinitely long metallic plates at different potentials [20]. The local oxide capacitance is then defined as the ratio between the interface charge density and the interface

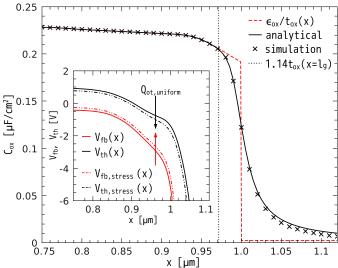

Fig. 5. The local oxide capacitance calculated using the approach of [18], compared with the newly developed analytical model. Here  $l_{\rm g}$  is the position of the drain end of the gate. Inset: local threshold and flatband voltage distributions with uniform oxide charge profiles.

potential and can be written as [19]

$$x = \frac{t_{\text{ox}}(x)}{\pi} (\varphi + \exp(\varphi))$$

$$C_{\text{ox}}(x) = \frac{\varepsilon_{\text{ox}}}{t_{\text{ox}}(x)(1 + \exp(\varphi))}$$

(4)

For  $x \to -\infty$  (or  $\varphi \to -\infty$ ) equation (4) asymptotically turns into the well known expression for the parallel-plate capacitance (2).

For evaluating the local oxide capacitance using device modeling we employ the method developed by Lee et~al. [18]. To determine  $C_{\rm ox}(x)$  by means of simulations, a careful calculation of the local flatband  $V_{\rm fb}(x)$  and threshold  $V_{\rm th}(x)$  voltage distributions as crucial quantities is performed. Due to the symmetry of the source and drain for the fresh device, we present results only for the drain half of the device [18]. For an unstressed transistor  $V_{\rm th}(x)$  and  $V_{\rm fb}(x)$  can be obtained with a widely-adopted routine [7,21] employing our device simulator MiniMOS-NT [22]. The carrier concentrations used as a criterion for local threshold and flatband voltages are  $2\times 10^{13}{\rm cm}^{-3}$  and  $8\times 10^{14}{\rm cm}^{-3}$ , respectively. The validity of the obtained curves has been verified using the Monte-Carlo device simulator MONJU [23, 24].

For any point at the device interface the post-stress local threshold  $V_{\rm th}(x)$  and local flatband  $V_{\rm fb}(x)$  values deviate from the pre-stressed by [16, 25]:

$$V_{\rm th,stress}(x) = V_{\rm th}(x) - \frac{\mathrm{q}\Delta N_{\rm ot}(x)}{C_{\rm ox}(x)} + \frac{\mathrm{q}\Delta N_{\rm it}(x)}{2C_{\rm ox}(x)}$$

$$V_{\rm fb,stress}(x) = V_{\rm fb}(x) - \frac{\mathrm{q}\Delta N_{\rm ot}(x)}{C_{\rm ox}(x)} - \frac{\mathrm{q}\Delta N_{\rm it}(x)}{2C_{\rm ox}(x)},$$

(5)

where  $\Delta N_{\rm it}(x)$  and  $\Delta N_{\rm ot}(x)$  is the change between pre- and post-stress concentrations of interface traps and bulk oxide

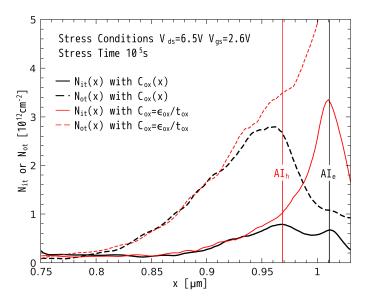

Fig. 6. The lateral distributions of  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  extracted using different  $C_{\rm ox}(x)$  approaches for  $10^5 {\rm s}$  at  $V_{\rm ds}$ =6.5V and  $V_{\rm gs}$ =2.6V. Peaks of  $N_{\rm it}(x)$  correspond to the maxima of electron and hole acceleration integrals [8].

Fig. 7. The comparison of the experimental and simulated transfer characteristics for fresh and stressed devices.

charges. In other words, the presence of a uniform probe oxide charge  $Q_{\rm ot,uniform}$  leads to a local threshold voltage shift  $\Delta V_{\rm th,uniform}(x)$  [18]. The local oxide capacitance is thus found as

$$C_{\rm ox}(x) = -Q_{\rm ot,uniform}/\Delta V_{\rm th,uniform}(x).$$

(6)

A typical example of  $\Delta V_{\rm th,uniform}(x)$  induced by a uniform oxide charge density of  $10^{12} {\rm cm}^{-2}$  is shown in Fig. 5, inset.

A comparison of the simulations and developed analytical approach for the local capacitance profile shows good agreement, see Fig. 5. At the same time, the expression  $C_{\rm ox}=\varepsilon_{\rm ox}/t_{\rm ox}$  – even when corrected for  $t_{\rm ox}=t_{\rm ox}(x)$  (Fig. 1, inset) – leads to substantially different results. The value of

$C_{\rm ox}(x)$  has its maximum with  $C_{\rm ox}(=\varepsilon_{\rm ox}/t_{\rm ox})$  in the middle of the gate and decreases gradually toward a much lower value outside the gate edge due to the fringing effect. As expected, the most pronounced peculiarity is observed at the drain side of the gate where the abrupt change in the oxide thickness occurs, Fig. 1, inset. From a detailed analysis using the suggested conformal transformation we conclude that under the gate electrode the fringing effect can be neglected for distances larger than  $1.14t_{\rm ox}(x=l_{\rm g})$  from the gate edge (this is reflected in Fig. 5). Note that an abrupt reduction in  $C_{\rm ox}(x)$  at  $x=1.0\mu{\rm m}$  is unphysical and such an approach should not be used.

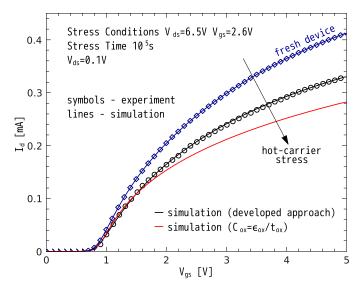

# B. Extraction of $N_{\rm ot}(x)$ and $N_{\rm it}(x)$ Profiles

For extraction of the evolution of  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  with the stress time we employed the analytical  $C_{\rm ox}(x)$  distribution incorporated into the scheme described in [16] based on system (5). The results obtained under different assumptions on the  $C_{\rm ox}(x)$  distribution are presented in Fig. 6. The extracted  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  profiles were subjected to further validation as input parameters to simulate the transfer characteristics of the degraded device. Comparison of simulated and experimental curves once again confirms applicability of the developed model (see Fig. 7). The role of the fringing effect at large stress times is obvious.

#### IV. RESULTS AND DISCUSSION

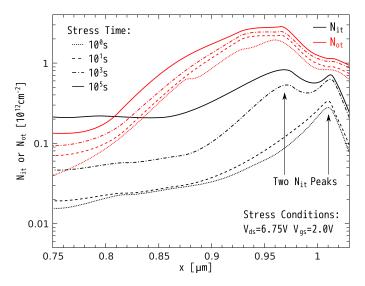

The extracted  $N_{\rm it}(x)$  profile features two peaks, see Fig. 6. This finding is in good agreement with the results of our HCD model [8] which shows that these peaks are related to the contributions induced by primary channel electrons and secondary generated holes (note that the latter one is shifted towards the source). Fig. 6 demonstrates that these peaks just correspond to the maxima of the electron and hole acceleration integrals. In our previous works [8, 10] we have already demonstrated that in long-channel devices the multiple-carrier process of Si-H bond-breakage leads to  $N_{\rm it}$ homogeneously distributed over x (see Figs. 8,9). At the same time, this is just the component which gives the main contribution to  $\Delta V_{

m th}$  because the device is most sensitive to  $N_{\rm it}$  created closer to the channel middle where the SC-related contribution is negligible. Hence, notwithstanding the fact that the maximum value of  $N_{\rm ot}$  is higher than the  $N_{\rm it}$  peak value already from the beginning (Figs. 8,9),  $N_{\rm it}$  starts to prevail over  $N_{\rm ot}$  at longer times ( $\gtrsim 10^4 {\rm s}$  in this particular case). This is because at these times only the peak  $N_{\rm ot}$  value is higher than the  $N_{\rm it}$  maximum while within the device center (which defines the  $V_{\rm th}$  behavior)  $N_{\rm it}$  is higher. Strong localization of the  $N_{\rm it}$  SC-component near the drain edge of the gate and, as a consequence, the secondary influence on  $\Delta V_{\rm th}$  can be confirmed by saturation of  $V_{

m th}$  and a turn-around effect. This trend is depicted in Fig. 3, where the inset also shows for four MOSFETs of the same architecture with different gate lengths.

The main conclusion drawn from these results is that the hole contribution is considerably shifted towards the source. The single-electron component generates traps situated outside the channel which explains why the hole-induced traps have a stronger relative impact on the threshold voltage turn-around effect. The contribution of channel holes to the total defect concentration is much less than the corresponding fraction of the  $V_{\rm th}$  change. This trend becomes more pronounced for longer devices (Fig. 3, inset), see also [8]. Another tendency supporting these conclusions is that the  $\Delta V_{\rm th}$  turn-around effect is less pronounced at room temperature (Fig. 3 for the stress regime with  $V_{\rm ds}=6.25{\rm V}$  and  $V_{\rm gs}=2.0{\rm V}$ ). This is because trapping/detrapping in the oxide bulk is triggered by non-elastic trap-assisted tunneling which is accelerated at higher temperatures [26, 27].

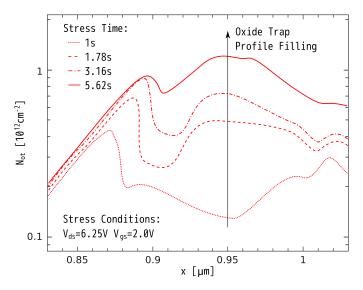

In Fig. 10 the  $N_{\rm ot}(x)$  profiles are resolved for short stress times. The tendencies typical for  $N_{\rm it}$  are also pronounced in the case of bulk charge density: at short stress times  $N_{\rm ot}$  demonstrates two peaks related to channel electrons and to secondary generated holes. Initially, these peaks are differently located in space while after  $\sim$ 5s they unite into a single common hump. This behavior can be explained assuming that trap-assisted tunneling responsible for charging bulk oxide traps occurs not necessarily perpendicular to the  $\rm Si/SiO_2$  interface. As a result, the bulk states situated (over the x coordinate) between two initial peaks are also being filled resulting in a widened hump on the  $N_{\rm ot}$  profile.

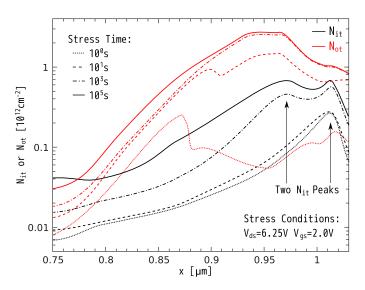

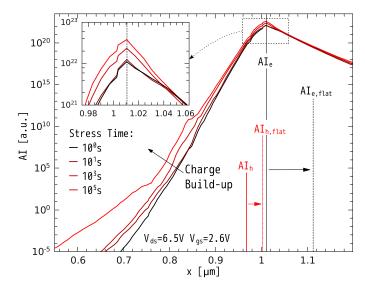

It is worth emphasizing that the position of the  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  peaks does not change with time (Figs. 8,9). This is in a good agreement with the model predictions where the position of the carrier acceleration integral maximum just coincides with the  $N_{\rm it}(x)$  peak position. To additionally check this we self-consistently calculated the acceleration integrals considering  $N_{\rm it}(x)$ . Fig. 11 shows the AI vs. x and confirms the previous tendency. Note finally that if during simulations the oxide thickness is assumed uniform  $(t_{\rm ox}(x)=t_{\rm ox})$ , both AI peaks are shifted (relatively to the AI peaks typical for the real device geometry), which implicitly confirms that the peculiarities of the device architecture have to be taken into account.

## V. CONCLUSION

We have examined the turn-around effect of the threshold voltage shift under the worst-case hot-carrier stress conditions for long-channel 5V n-MOSFETs. For this purpose, we have improved the conventional defect density profile extraction techniques from charge-pumping measurements. We have demonstrated that by ignoring the spatial variation of  $C_{ox}(x)$ , a spurious result is produced, leading to an ambiguous picture of HCD with the model ignoring the  $C_{\rm ox}(x)$  distribution. The turn-around of the  $V_{\rm th}$  shift is explained to be due to the interplay between  $N_{\rm it}$  and  $N_{\rm ot}$  induced contributions. This idea is supported by our model of hot-carrier degradation which considers contribution of channel electrons as well as secondary holes generated by impact ionization. We have shown that in spite of a less pronounced hole contribution to the total interface states density, the device behavior is more sensitive to the hole-induced trap generation as compared to the electron contribution. This is related to the fact that the

Fig. 8. The evolution of  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  profiles with stress time for  $V_{\rm ds}=6.25{\rm V}$  and  $V_{\rm gs}=2.0{\rm V}$ .

Fig. 9. The evolution of  $N_{\rm it}(x)$  and  $N_{\rm ot}(x)$  profiles with stress time for  $V_{\rm ds}$ =6.75V and  $V_{\rm gs}$ =2.0V.

hole-induced portion of  $N_{\rm it}$  is situated closer to the channel, thereby affecting the  $V_{\rm th}$  in a stronger fashion.

## REFERENCES

- [1] V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling," *Microel. Reliab.*, vol. 46, no. 1, pp. 1–23, 2006.

- [2] T. Grasser, T. Achinger, G. Pobegen, H. Reisinger, P.-J. Wagner, J. Franco, M. Nelhiebel, and B. Kaczer, "The 'permanent' component of NBTI: Composition and annealing," in *Conference Proceedings of International Reliability Physics Symposium (IRPS 2011)*, 2011.

- [3] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P.-J. Wagner, F. Schanowsky, J. Franco, P. Roussel, and M. Nelhiebel, "Recent advances in understanding the bias temperature instability," in *Proc. International Electron Devices Meeting (IEDM)*, pp. 82–85, 2010.

- [4] A. Bravaix and V. Huard, "Hot-carrier degradation issues in advanced CMOS nodes," in *Proc. European Symposium on Reliability of Electron Devices Failure Physics and Analysis (ESREF)*, tutorial, 2010.

Fig. 10. Filling of the oxide traps revealed for small stress times at the stress regime with  $V_{\rm ds}$ =6.25V and  $V_{\rm gs}$ =2.6V.

Fig. 11. The evolution of  $AI_e$  with the stress time for  $V_{ds}$ =6.5V and  $V_{gs}$  =2.6V. The position of the  $N_{it}(x)$  and  $N_{ot}(x)$  peaks does not change with the stress time. The assumption of a constant oxide thickness results in a significant shift of the AI peak for holes and electrons ( $AI_{e(h)} \rightarrow AI_{e(h),flat}$ ).

- [5] S. Rauch and G. L. Rosa, "CMOS hot carrier: From physics to end of life projections, and qualification," in *Proc. International Reliability Physics Symposium (IRPS)*, tutorial, 2010.

- [6] D. DiMaria and J. Stasiak, "Trap creation in silicon dioxide produced by hot electrons," *Journ. Appl. Phys.*, vol. 65, no. 6, pp. 2342–2356, 1989

- [7] P. Heremans, J. Witters, G. Groeseneken, and H. Maes, "Analysis of the charge pumping technique and its application for the evaluation of the MOSFET degradation," *IEEE Trans. Electron Dev.*, vol. 36, p. 1318, 1000

- [8] S. Tyaginov, I. Starkov, O. Triebl, H. Enichlmair, C. Jungemann, J. Park, H. Ceric, and T. Grasser, "Secondary generated holes as a crucial component for modeling of HC degradation in high-voltage n-MOSFET," in *Proc. International Conference on Simulation of Semiconductor Processes and Devices (SISPAD)*, pp. 123–126, 2011.

- [9] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann,

- S. Carniello, J. Park, H. Enichlmail, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Interface traps density-of-states as a vital component for hot-carrier degradation modeling," *Microelectronics Reliability*, vol. 50, pp. 1267–1272, 2010.

- [10] I. Starkov, S. Tyaginov, H. Enichlmair, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Ceric, and T. Grasser, "Hot-carrier degradation caused interface state profile - simulations vs. experiment," *Journal of Vacuum Science and Technology - B*, vol. 29, no. 1, pp. 01AB09–1– 01AB09–8, 2011.

- [11] W. McMahon, K. Matsuda, J. Lee, K. Hess, and J. Lyding, "The effects of a multiple carrier model of interface states generation of lifetime extraction for MOSFETs," in *Proc. Int. Conf. Mod. Sim. Micro*, vol. 1, pp. 576–579, 2002.

- [12] K. Hess, L. Register, B. Tuttle, J. Lyding, and I. Kizilyalli, "Impact of nanostructure research on conventional solid-state electronics: the giant isotope effect in hydrogen desorption and CMOS lifetime," *Physica E*, vol. 3, pp. 1–7, 1998.

- [13] J. Wang-Ratkovic, R. Lacoe, K. Williams, M. Song, S. Brown, and G. Yabiku, "New understanding of LDD CMOS hot-carrier degradation and device lifetime at cryogenic temperatures," in *Proc. International Reliability Physics Symposium (IRPS)*, pp. 312–314, 2003.

- [14] I. Starkov, S. Tyaginov, H. Enichlmair, J. Park, T. Grasser, and C. Jungemann, "Analysis of worst-case hot-carrier degradation conditions in the case of n- and p-channel high-voltage MOSFETs," in *International Conference on Simulation of Semiconductor Processes and Devices* (SISPAD), pp. 127–130, 2011.

- [15] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmair, M. Karner, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Hot-carrier degradation modeling using full-band monte-carlo simulations," in *Proc. Interna*tional Symposium on the Physical & Failure Analysis of Integrated Circuits (IPFA), 2010.

- [16] W. K. Chim, S. E. Leang, and D. S. H. Chan, "Extraction of metal-oxide semiconductor field-effect-transistor interface state and trapped charge spatial distributions using a physics-based algorithm," *Journ. Appl. Phys.*, vol. 81, no. 4, pp. 1992–1997, 1997.

- [17] S. Mahapatra, C. Parikh, V. Rao, C. Viswanathan, and J. Vasi, "Device scaling effects on hot-carrier induced interface and oxide-trapped charge distributions in MOSFETs," *EEE Trans. Electron Dev.*, vol. 47, no. 4, pp. 789–796, 2000.

- [18] R. G.-H. Lee, J.-S. Su, and S. S. Chung, "A new method for characterizing the spatial distributions of interface states and oxide-trapped charges in LDD n-MOSFETs," *IEEE Trans. Electron Dev.*, vol. 43, no. 1, pp. 81–89, 1996.

- [19] I. Starkov, A. Starkov, S. Tyaginov, H. Enichlmair, H. Ceric, and T. Grasser, "An analytical model for MOSFET local oxide capacitance," in *Proc. International Semiconductor Device Research Symposium (IS-DRS 2011)*, 2011.

- [20] N. Pesonen, W. Kahn, R. Allen, M. Cresswell, and M. Zaghloul, "Application of conformal mapping approximation techniques: parallel conductors of finite dimensions," *Instrumentation and Measurement*, *IEEE Transactions on*, vol. 53, pp. 812–821, june 2004.

- [21] S. Chung and J.-J. Yang, "A new approach for characterizing structuredependent hot-carrier effects in drain-engineered MOSFET's," *IEEE Trans Electron Dev.*, vol. 46, pp. 1371–1377, July 1999.

- [22] Institute for Microelectronic, TU Wien, MiniMOS-NT Device and Circuit Simulator.

- [23] C. Jungemann and B. Meinerzhagen, Hierarchical Device Simulation. Springer Verlag Wien/New York, 2003.

- [24] I. Starkov, S. Tyaginov, H. Enichlmair, J. Park, H. Ceric, and T. Grasser, "Accurate extraction of MOSFET unstressed interface state spatial distribution from charge pumping measurements," *Solid State Phenomena*, vol. 178-179, pp. 267–272, 2011.

- [25] S. Mahapatra, D. Parikh, V. Rao, C. Viswanathan, and J. Vasi, "A comprehensive study of hot-carrier induced interface and oxide trap distribution in MOSFETs using a novel charge pumping technique," *IEEE Trans. Electron Dev.*, vol. 47, no. 1, pp. 171–177, 2000.

- IEEE Trans. Electron Dev., vol. 47, no. 1, pp. 171–177, 2000.

[26] M. Houssa, M. Tuominen, M. Naili, V. Afanas'ev, A. Stesmans, S. Haukka, and M. M. Heyns, "Trap-assisted tunneling in high permittivity gate dielectric stacks," Journal of Applied Physics, vol. 87, no. 12, pp. 8615–8620, 2000.

- [27] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities," *Microelectronics Reliability*, vol. 52, no. 1, pp. 39–70, 2011.