## New Trends in Microelectronics: Towards an Ultimate Memory Concept

A. Makarov, V. Sverdlov, and S. Selberherr Institute for Microelectronics, TU Wien, Gußhausstraße 27-29/E360, A-1040 Wien, Austria Email: {makarov|sverdlov|selberherr}@iue.tuwien.ac.at

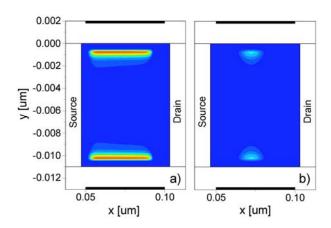

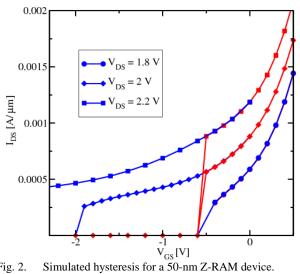

Memory is an indispensible component of any modern integrated circuit. While MOSFET scaling has advanced tremendously, traditional DRAM cell scaling is hampered by the presence of a capacitor which is difficult to reduce in size. Recently, an interesting concept of a DRAM memory cell based on a transistor alone was introduced. The ultimate advantage of this new concept is that it does not require a capacitor, and, in contrast to traditional 1T/1C DRAM cells, it represents a 1T/0C cell named Z(for zero)-RAM. The advanced Z-RAM bitcells built on a multiple-gate MOSFET (MuGFET) utilizes the bipolar transistor usually considered as parasitic [1]. The advantage is that the current flows through the body of the structure. The majority carriers are generated by impact ionization and stored under the gates. The charge stored opens the bipolar transistor guaranteeing high current (state 1). The stored charge can be flashed out by applying the voltage pulse to the gates returning the bipolar transistor into the low current state 0. The stored charge for the bipolar transistor in the high current and low current states is shown in Fig.1. The results [2] of current calculations as function of the gate voltage for a doublegate structure with 10nm thin body are shown in Fig.2. In a forward scan direction of the gate voltage, the current stays low until a certain critical value is reached. After that the source-drain current rapidly increases by several orders of magnitude. In a reverse gate voltage scan, the current first slowly decreases, however, due to the charge stored under the gates, the relatively large current value is maintained down to the negative gate voltages, where it abruptly decreases by several orders of magnitude completing the hysteresis loop [2]. The use of vertical gate-all around transistors extends the Z-RAM roadmap to future generations. One disadvantage of the Z-RAM cell is the relatively high operating voltage needed to ignite impact ionization. To reduce the operating voltage, a new concept of a 1T/0C cell was recently proposed [3].

Charge-based memories including flash are, however, gradually approaching the physical limits of scalability, and the search for a new universal memory concept has accelerated. A new type of universal memory has to be nonvolatile and must exhibit low operating voltage, low power consumption, high operation speed, long retention time, high endurance, simple structure, and small size.

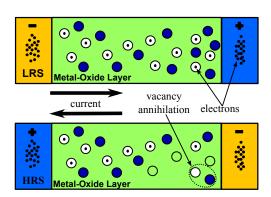

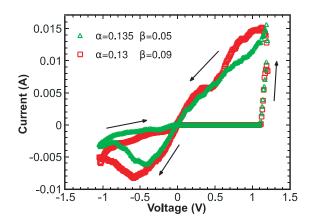

One of the promising candidates for future universal memory is the resistive random access memory (RRAM). It is based on new materials, such as metal oxides and perovskite oxides. This type of memory is characterized by high density, excellent scalability, low operating voltages (<2V), fast switching times (<10ns), and long retention time. We developed a stochastic model of the bipolar resistive switching mechanism based on electron hopping between the oxygen vacancies along the conductive filament (CF) in an oxide layer. The CF is formed by localized oxygen vacancies ( $V_o$ ) [4] or domains of  $V_o$  (Fig. 3). Formation and rupture of a CF is due to a redox reaction in the oxide layer under a voltage bias. The hysteresis cycles modeled [5] is shown in Fig.4.

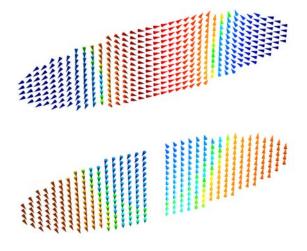

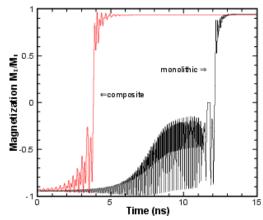

The spin transfer torque random access memory (STTRAM) is another promising candidate for future universal memory. The reduction of the current density required for switching and the increase of the switching speed are among the most important challenges in this area. A decrease in the critical current density for the penta-layer magnetic tunnel junction was reported in [6]. By numerically investigating the dynamics of the switching process illustrated in Fig.5 in a junction composed of five layers we demonstrate [7] that the switching time can be significantly decreased (Fig.6) by the removal of the switching bottleneck due to the central region of the free layer and by tilting the magnetization of the end domains in the magnetostatic field of the uncompensated pinned layers.

This research is supported by the European Research Council through the grant #247056 MOSILSPIN.

## REFERENCES

- [1] S. Okhonin et al, IEEE IEDM, 2007, pp. 925-928.

- [2] V. Sverdlov, S. Selberherr, Proc. International Conference on Computational & Experimental Engineering and Sciences (ICCES), 2010, pp. 232-247.

- [3] N. Rodrigues et al., IEEE Electron Dev. Lett., vol. 31, no. 9, pp. 972-974, 2010.

- [4] B. Gao et al., IEEE Electron Dev. Lett., vol. 30, no. 12, pp. 1326-1328, 2009.

- [5] A. Makarov et al., Journal of Vacuum Science & Technology B, vol. 29, no. 1, pp. 01AD03 (1-5), 2011.

- [6] G.D. Fuchs et al., Appl. Phys. Lett., vol. 86, pp. 152509 (1-3), 2005.

- [7] A. Makarov et al., Phys. Stat. Solidi (RRL), DOI: 10.1002/pssr.201105376, 2011.

Simulated hole concentration along the fin in states "1" (a) and "0" (b) for a 50-nm Z-RAM device.

Fig. 2.

Schematic illustration of the conducting filament in the low resistance state (top) and the high resistance state (bottom).

I-V characteristics showing the hysteresis cycle obtained from the stochastic model, for two sets of parameters.

Snapshots of the switching process for the monolithic (top) and composite (bottom) free magnetic layer.

Magnetization evolution in the free magnetic layer. Faster switching is predicted for the composite layer.