# Accurate Extraction of MOSFET Unstressed Interface State Spatial Distribution from Charge Pumping Measurements

Ivan Starkov $^{1,a}$ , Stanislav Tyaginov $^{2,b}$ , Hubert Enichlmair $^{3,c}$ , Jong Mun Park $^{3,d}$ , Hajdin Ceric $^{1,e}$ , and Tibor Grasser $^{2,f}$

<sup>1</sup>Christian Doppler Laboratory for Reliability Issues in Microelectronics at the

<sup>2</sup>Institute for Microelectronics, Vienna University of Technology, Gußhausstraße 27-29, A-1040 Wien, Austria

<sup>3</sup>Process Development and Implementation Department, Austriamicrosystems AG, Tobelbader Straße 30, A-8141 Unterpremstaetten, Austria

<sup>a</sup>starkov@iue.tuwien.ac.at, <sup>b</sup>tyaginov@iue.tuwien.ac.at, <sup>c</sup>hubert.enichlmair@austriamicrosystems.com, <sup>d</sup>jong-mun.park@austriamicrosystems.com, <sup>e</sup>ceric@iue.tuwien.ac.at, <sup>f</sup>grasser@iue.tuwien.ac.at

Keywords: interface states, charge pumping, hot-carrier degradation, TCAD, MOSFET.

**Abstract.** The interface state density profile for an unstressed transistor has been carefully extracted. The experimental evidence of profile non-uniformity is presented. A scheme to separate the bulk oxide trap contribution from the total charge pumping current is suggested as an improvement to the conventional extraction procedure. The obtained information is of high importance in the context of hot-carrier degradation modeling in order to allow for a more detailed verification of the model.

#### Introduction

The density of interface traps along the Si/SiO<sub>2</sub> interface of an unstressed metal-oxide-semiconductor field-effect transistor (MOSFET) considerably depends on the fabrication process and the device geometry. The necessity to consider a number of factors with a variety of physical properties results in the absence of an established model describing initial transistor defect profile even nowadays. Unfortunately, theoretical calculations of the defect concentration is a very complicated problem and no known solution exists. One of the most widely used experimental methods to obtain this information is the charge pumping (CP) technique [1]. In papers devoted to extraction algorithms of the lateral interface state density  $N_{\rm it}(x)$  profile from CP current, different assumptions on the initial interface trap concentration (of a fresh device) have been used. To our knowledge, in only a few papers the initial profile uniformity is checked [2, 3, 4]. At the same time, in most techniques for the  $N_{\rm it}(x)$  extraction from CP data it is commonly assumed that the initial  $N_{\rm it}(x)$  is homogeneous [5, 6]. This assumption is only a simplification, not supported by physical reasoning. The presence of a nonuniform pre-stressed  $N_{\rm it}$  profile is usually ignored while modeling the evolution of  $N_{\rm it}(x)$  during hot-carrier degradation (HCD). In fact, HCD-induced  $N_{\rm it}$  may easily reach  $10^{12}{\rm cm}^{-2}$ , while initial  $N_{\rm it}$  has typical values of  $\sim 10^{10} {\rm cm}^{-2}$ . However, the hot-carrier stress is usually performed at voltages higher than operating ones. Thus, at operating conditions and/or short stress times, the interface state density will be characterized by moderate values, comparable with pre-stressed  $N_{\rm it}$ . Therefore, for a proper description of HCD at operating conditions the information concerning the initial interface state concentration is of significant importance. We undertake an attempt to combine relevant approaches for  $N_{it}(x)$  extraction from CP measurements [1, 2, 3, 4, 7] within a single framework, thereby implementing an exhaustive technique. The suggested scheme takes a number of factors affecting the CP current behavior into account.

#### **Experimental Details**

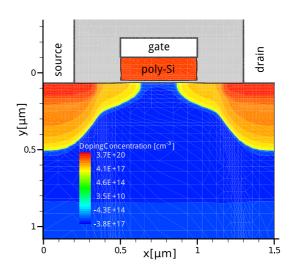

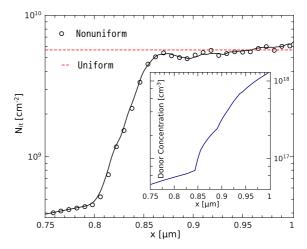

For our investigations we use an n-type MOSFET fabricated on a standard  $0.35\mu m$  CMOS process. The device architecture and the net doping profile are sketched in Fig. 1. All lateral coordinates x refer to an origin placed at the left edge of the source contact. Since we are dealing with a long-channel device (gate length  $L_{\rm gate} = 0.5 \mu \rm m$ ) the singleelectron mechanism of the Si - H bond dissociation process is dominant [8]. The constant baselevel charge pumping technique [9, 6, 5] with a fixed base level  $V_{\rm gl} = -5 \, \rm V$  and  $V_{\rm gh}$  increasing from -4 V to 4 V of the gate pulse has been employed to investigate the interface state density. A device channel width of  $W = 10 \mu \text{m}$  was chosen to obtain a sufficient charge pumping signal. A standard experimental scheme with the gate of the transistor connected to a pulse generator and a

Fig. 1: The topology of an n-MOSFET with the net doping profile represented by the color map.

small constant reverse bias applied to the source and drain was used. The substrate current ( $I_{cp}$ ) was monitored. Only the charge pumping current of the unstressed device is considered here.

#### **Interface State Distribution of Unstressed Device**

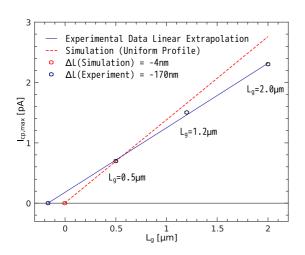

The uniformity of the initial interface trap distribution can be verified using the dependence of the maximum value of the charge pumping current  $(I_{\rm cp,max})$  versus the nominal gate electrode length  $(L_{\rm gate})$ . The linear relationship between  $I_{\rm cp,max}$  and  $L_{\rm gate}$  suggests an absence of disparity between the interface state density near the source-drain region and the center of the channel. In this case the assumption that the pre-stressed  $N_{\rm it}$  profiles are uniform along the channel is adequate [2]. Extrapolation to  $I_{\rm cp,max}=0$  reveals the difference  $(\Delta L)$  between the nominal  $(L_{\rm gate})$  and effective  $(L_{\rm eff})$  channel lengths which contributes to the CP current [1]. Essentially,  $L_{\rm eff}=L_{\rm gate}-\Delta L$ .

We are aware only of a limited number of works devoted to  $N_{\rm it}(x)$  extraction techniques from the CP current, where this dependence has been verified [2, 3, 4]. However, from our point of view, it is difficult to judge on the legitimacy of the obtained findings in the last two papers. In fact, in [3] only two gate lengths are used and a small spread of  $L_{\rm gate}$ , while a suspiciously linear behavior is presented in [4]. This suggests that this issue demands a more detailed analysis.

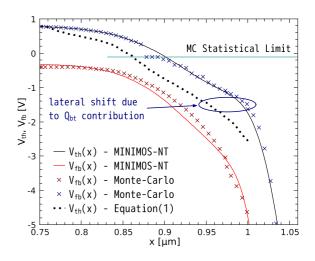

To determine the effective length  $L_{\rm eff}$ , a careful calculation of local flatband  $V_{\rm fb}(x)$  and threshold  $V_{\rm th}(x)$  voltage distributions as crucial quantities controlling the matter is performed. Due to the symmetry of the source and drain for the fresh device, we present results only for the drain half of the device, confirmed in [5]. For an unstressed transistor  $V_{\rm th}(x)$  and  $V_{\rm fb}(x)$  can be obtained with a widely-adopted routine [1, 2, 6] employing our device simulator MINIMOS-NT [10]. The carrier distribution required for the local threshold and flatband voltage calculation was estimated to be  $2\times 10^{13} {\rm cm}^{-3}$  and  $8\times 10^{14} {\rm cm}^{-3}$  for the simulation, respectively. The validity of the obtained curves has been verified using the Monte-Carlo device simulator MONJU [11]. Figure 2 shows a good agreement between the results. Note that in the low voltage region the agreement degrades due to the stochastic nature of the Monte-Carlo approach which can not provide enough precision in this area. As stated in [1, 2], the effective channel length in the case of constant base-level charge pumping technique is defined as  $L_{\rm eff}=2|l-L_{\rm c}|$  for  $V_{\rm gh}\geqslant V_{\rm th}(L_{\rm c})$ , where l is the solution of the equation  $V_{\rm fb}(l)=V_{\rm gl}$  and  $L_{\rm c}$  is the center point of the channel specified by the device geometry.

The simulation has yielded an effective channel length of  $0.504\mu\mathrm{m}$  while  $V_{\rm gl}$  was held at -5V for the fresh device. Figure 3 depicts  $I_{\rm cp,max}$  plotted vs.  $L_{\rm gate}$  and a simple linear extrapolation of CP

Fig. 2: Local threshold  $V_{\rm th}(x)$  and flatband  $V_{\rm fb}(x)$  voltage profiles of a pre-stressed device calculated using different approaches.

Fig. 3: Maximum value of the charge pumping current for different gate electrode lengths of the fresh device.

data gives  $L_{\rm eff}=0.670\mu{\rm m}$ , i.e. the position practically on the drain contact. Such an experimental value of the effective channel length is extremely dubious and supports the idea of  $N_{\rm it}(x)$  profile non-uniformity. Let us emphasize that in the case of a homogeneous  $N_{\rm it}$  distribution one may obtain a  $V_{\rm th}(x)$  profile directly from the charge pumping current  $I_{\rm cp}(V_{\rm gh})$  for the undamaged device employing the the method proposed in [2, 5]. According to this approach

$$V_{\text{th}}(x) = V_{\text{gh}}; \ x(V_{\text{gh}}) = L_{\text{c}} + \left(1 - \frac{I_{\text{cp}}(V_{\text{gh}})}{I_{\text{cp,max}}}\right) \frac{L_{\text{eff}}}{2}.$$

(1)

A comparison between this ``experimental" and the simulated threshold voltage profiles  $V_{\rm th}(x)$  can confirm the interface state density non-uniformity and is shown in Fig. 2.

However, such a huge discrepancy in the results can not be induced by the difference in initial  $N_{\rm it}$  because the  $V_{\rm th}$  shift corresponds to an interface trap density of  $10^{12} {\rm cm}^{-2}$ , i.e. for a heavily stressed device. This anomalous offset has a simple explanation. The method based on Eq.(1) does not work properly due to the border trap contribution to the CP current. As it was explained in detail in [12], a presence of trapped border charges  $Q_{\rm bt}$  requires special attention to distinguish between contributions to  $I_{\rm cp}$  induced by border  $(I_{\rm cp,bt}(V_{\rm gh}))$  and interface states  $(I_{\rm cp,it}(V_{\rm gh}))$

$$I_{\rm cp}(V_{\rm gh}) = I_{\rm cp,it}(V_{\rm gh}) + I_{\rm cp,bt}(V_{\rm gh}),$$

(2)

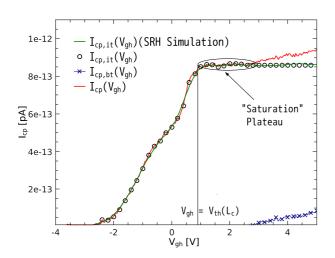

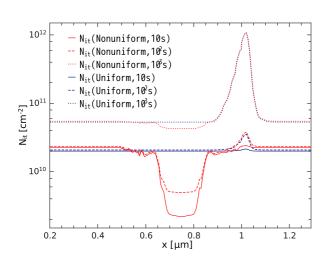

The presence of  $I_{\rm cp,bt}(V_{\rm gh})$  results in a spurious determination of  $I_{\rm cp,max}$  and  $L_{\rm eff}$  and, as a consequence, to an erroneous value for the uniform  $N_{\rm it}$  profile. Thus, an additional separation procedure of CP current components must be performed. This separation of  $I_{\rm cp,bt}(V_{\rm gh})$  from the total CP current relies on the following features of the employed charge pumping technique: at  $V_{\rm gh} \geqslant V_{\rm th}(L_{\rm c})$  the interface state density can not increase  $I_{\rm cp}$  because the active measurement area has already reached  $L_{\rm eff}$ . In other words,  $I_{\rm cp,it}(V_{\rm gh} \geqslant V_{\rm th}(L_{\rm c})) = {\rm const.}$  An explicitly revealed plateau (see Fig. 4) corresponds to the saturation of an interface trap induced dose of the charge pumping current and the absence of the  $Q_{\rm bt}$  contribution. This means, for  $V_{\rm gh} \geqslant V_{\rm th}(L_{\rm c})$  the border trap contribution to the CP signal is

$$I_{\rm cp,bt}(V_{\rm gh}) = I_{\rm cp}(V_{\rm gh}) - I_{\rm cp}(V_{\rm th}(L_{\rm c})).$$

(3)

This finding is supported by the interface state dynamics based on the Shockley-Read-Hall theory [13] (see Fig. 4). Let us mention that the experimental data in Fig. 3 was processed according to the described scheme.

Fig. 4: Charge pumping current of an undamaged device. Interface and border trap components are revealed.

Fig. 5: The lateral interface state density: comparison of uniform and nonuniform profiles.

Unfortunately, the method suggested above is not appropriate for the varying base-level technique because, for this technique, a continuous increase of the active measurement area occurs. Moreover, in the case of CP measurements with a lower gate pulse frequency (a few kHz [12]) it is not possible to expose the saturation plateau and a more complicated extraction scheme of border trap contribution (as that proposed in [14]) must be employed.

After the produced separation it is possible to use the technique for  $N_{it}$  extraction developed in [6]. The interface trap concentration of a pre-stressed device can be written as

$$N_{\rm it}(x) = \frac{1}{\mathsf{q}fW} \frac{\mathsf{d}I_{\rm cp,it}(V_{\rm gh})}{\mathsf{d}V_{\rm gh}} \frac{\mathsf{d}V_{\rm th}(x)}{\mathsf{d}x},\tag{4}$$

while using the uniform approach [2] results in

$$N_{\rm it,uni} = \frac{1}{afW} \frac{I_{\rm cp}(V_{\rm th}(L_{\rm c}))}{I_{\rm ceff}},\tag{5}$$

where q is the elementary charge. Figure 5 depicts a comparison between the uniform and nonuniform interface state density profiles. We believe that the gap in the center of the device can be linked to the peculiarities of the device fabrication process. The inset in Fig. 5 represents the donor doping concentration with increased gradient at  $0.85\mu m$  where  $N_{\rm it}(x)$  reaches a uniform value, i.e. the transistor alloying can affect the interface state density in this way.

#### **Results and Discussion**

The information on the initial interface state profile is crucial in the context of hot-carrier degradation modeling. We examine the impact of the initial  $N_{\rm it}$  distribution on the degraded device characteristics within our physics-based model of HCD [15]. This approach considers the interplay between the single- and multiple-carrier mechanisms (SC- and MC-processes) of Si - H bond-breakage. The bond is treated as a truncated harmonic oscillator with the corresponding ladder of eigenstates. The carriers striking the bond can induce bond rupture within a single collision (in the case of the SC-process) or bond heating (the MC-process). If the oscillator is highly excited, i.e. the hydrogen is situated on the last bonded level, the H ion can overcome the potential barrier separating the last bonded state and the transport state and induce the bond dissociation. Note that bond cooling accompanied by phonon desorption also takes place.

Fig. 6: Interface state density profile evolution calculated with our HCD model [15] under assumption of a uniform initial profile and employing  $N_{\rm it}(x)$  extracted according to the proposed scheme.

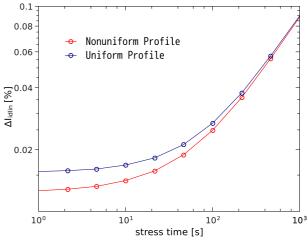

Fig. 7: Comparison of the  $I_{\rm dlin}$  degradation calculated with MINIMOS-NT using obtained  $N_{\rm it}(x)$  profiles (see Fig. 6) as input degradation characteristics.

All these oscillator transitions are considered within a system of rate equations describing the kinetics of the bond-breakage reaction [15]. The solution of the system relies on the initial conditions, that is the initial concentration of the virgin Si-H bonds. If some of these bonds are already prebroken, the density of bonds available to be ruptured is reduced. Therefore, the pre-existing dangling bonds already impact the characteristics of the fresh device which differ from those typical for an ideal transistor (with pre-stressed  $N_{\rm it}=0$ ) of the same configuration. Due to this initial interface state density profile the solution of the rate equation system -- i.e.  $N_{\rm it}(x,t)$  -- is modified.

Figure 6 (obtained for stress  $V_{\rm ds}=5.0{\rm V}$  and  $V_{\rm gs}=2.0{\rm V}$ ) illustrates this tendency showing the evolution of the interface state profile with stress time, calculated considering the uniform and the nonuniform initial  $N_{\rm it}$  distributions. The lack of details obtained from the uniform  $N_{\rm it}$  approach is apparent. One can see that the difference is more pronounced at short stress times because at longer times the total  $N_{\rm it}$  is already rather high, thereby screening the impact of the pre-stressed  $N_{\rm it}$  dose. This tendency is confirmed by Fig. 7 which demonstrates that the linear drain current change (calculated using real and uniform  $N_{\rm it}(x)$  profiles) is significantly different at stress times shorter than  $10^2{\rm s}$ . This trend means that an initial interface trap density can affect the device behavior only in the case of short stress times and relatively weak stresses. The second demand corresponds only to the case of real device operating conditions when the applied voltages are relatively low, compared to accelerated hot-carrier stresses.

#### Conclusion

We have undertaken a thorough extraction of the initial interface state density profile for a pre-stressed MOSFET. The improved extraction procedure of the interface trap distribution from the charge pumping current, as well as the experimental evidence of the distribution non-uniformity, is presented. The impact of the device pre-existing interface states on the subsequent  $N_{\rm it}$  profile evolution is demonstrated. A comparison between the change in the linear drain current calculated assuming a homogeneous initial  $N_{\rm it}$  profile and the real one can reach one percent of  $I_{\rm dlin}$  at short times. Therefore, the influence of the initial trap concentration on the simulated characteristics of the degraded device is most pronounced at short stress times and/or weak stresses. The second situation corresponds to the real device operating conditions and thus is of significant importance when evaluating the device operational life-time.

#### References

- [1] P. Heremans, J. Witters, G. Groeseneken, and H. Maes: IEEE Trans. Electron Dev., vol.36 (1989), p.1318.

- [2] M. Tsuchiaki, H. Hara, T.Morimoto, and H. Iwai: IEEE Trans. Electron Dev., vol.40 (1993), p.1768.

- [3] W. K. Chim, S. E. Leang, and D. S. H. Chan: Journ. Appl. Phys., vol.81 (1997), p.1992.

- [4] W. Emden, W. Krautschneider, G. Tempel, R. Hagenbeck, and F. Beug, in: *Proc. European Solid-State Device Research Conference (ESSDERC)*, (2007).

- [5] R. G.-H. Lee, J.-S. Su, and S. S. Chung: IEEE Trans. Electron Dev., vol.43 (1996), p.81.

- [6] S. Chung and J.-J. Yang, IEEE Trans. Electron Dev., vol.46 (1999), p.1371.

- [7] H.-H. Li, Y.-L. Chu, and C.-Y. Wu: IEEE Trans. Electron Dev., vol.44 (1997), p.782.

- [8] A. Bravaix and V. Huard, in: *Proc. European Symposium on Reliability of Electron Devices Failure Physics and Analysis (ESREF), tutorial,* (2010).

- [9] A. Elliot: Solid-State Electron., vol. 19 (1976), p.241.

- [10] Institute for Microelectronic, TU Wien, MiniMOS-NT Device and Circuit Simulator.

- [11] C. Jungemann and B. Meinerzhagen: Springer Verlag Wien/New York, (2003).

- [12] B. Djezzar, S. Oussalah, and A. Smatti: IEEE Trans. Nucl. Sc., vol.51 (2004), p.1724.

- [13] H.-H. Li, Y.-L. Chu, and C.-Y. Wu: IEEE Trans. Electron Dev., vol.43 (1996), p.1857.

- [14] T. Grasser, W. Gös, and B. Kaczer: ECS Transactions, vol.19 (2009), p.265.

- [15] I. Starkov, S. Tyaginov, H. Enichlmair, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Ceric, and T. Grasser: J. Vac. Sci. Techn. B, vol.29 (2011), p.01AB09--1.

### Gettering and Defect Engineering in Semiconductor Technology XIV

doi:10.4028/www.scientific.net/SSP.178-179

## Accurate Extraction of MOSFET Unstressed Interface State Spatial Distribution from Charge Pumping Measurements

doi:10.4028/www.scientific.net/SSP.178-179.267