# Hierarchical Simulation of Process Variations and Their Impact on Circuits and Systems: Results

Jürgen K. Lorenz, *Member, IEEE*, Eberhard Bär, Tanja Clees, Peter Evanschitzky, Roland Jancke, Christian Kampen, Uwe Paschen, Christian P. J. Salzig, and Siegfried Selberherr, *Fellow, IEEE*

Abstract—Process variations increasingly challenge the manufacturability of advanced devices and the yield of integrated circuits. Technology computer-aided design (TCAD) has the potential to make key contributions to minimize this problem, by assessing the impact of certain variations on the device, circuit, and system. In this way, TCAD can provide the information necessary to decide on investments in the processing level or the adoption of a more variation tolerant process flow, device architecture, or design on circuit or chip level. Five Fraunhofer institutes joined forces to address these issues. Their own software tools, e.g., for lithography/ topography simulation, mixed-mode device simulation, compact model extraction, and behavioral modeling, have been combined with commercial tools to establish a hierarchical system of simulators in order to analyze process variations from their source, e.g., in a lithography step, through device fabrication up to the circuit and system levels.

*Index Terms*—Circuit simulation, manufacturability, process modeling, semiconductor device modeling, sensitivity, yield.

### I. INTRODUCTION

A S DISCUSSED in the preceding paper [1] also published in this Special Issue, process variations are increasingly affecting the performance, the reliability, and the manufacturability of advanced semiconductor devices. Simulation is

Manuscript received November 16, 2010; revised February 23, 2011; accepted March 31, 2011. Date of publication June 16, 2011; date of current version July 22, 2011. This work was supported by the Fraunhofer Internal Programs under Grant MAVO 817 759. The review of this paper was arranged by Editor A. Asenov.

- J. K. Lorenz, E. Bär, P. Evanschitzky, and C. Kampen are with the Fraunhofer Institute for Integrated Systems and Device Technology (IISB), 91058 Erlangen, Germany (e-mail: juergen.lorenz@iisb.fraunhofer.de; eberhard.baer@iisb.fraunhofer.de; peter.evanschitzky@iisb.fraunhofer.de; christian.kampen@iisb.fraunhofer.de).

- T. Clees is with the Fraunhofer Institute for Algorithms and Scientific Computing (SCAI), 53754 Sankt Augustin, Germany (e-mail: tanja.clees@scai.fraunhofer.de).

- R. Jancke is with the Division Design Automation of the Fraunhofer Institute for Integrated Circuits (IIS/EAS), 01069 Dresden, Germany (e-mail: roland.jancke@eas.iis.fraunhofer.de).

- U. Paschen is with the Fraunhofer Institute for Microelectronic Circuits and Systems (IMS), 47057 Duisburg, Germany (e-mail: uwe.paschen@ims.fraunhofer.de).

- C. P. J. Salzig is with the Fraunhofer Institute for Industrial Mathematics (ITWM), 67663 Kaiserslautern, Germany (e-mail: christian.salzig@itwm.fraunhofer.de).

- S. Selberherr is with the Institute for Microelectronics, Vienna University of Technology, 1040 Vienna, Austria (e-mail: Selberherr@TUWien.ac.at).

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2011.2150226

the only realistic possibility for a holistic investigation of the impact of the large manifold of relevant process variations on circuits and systems. A hierarchical approach is required to investigate process variations from their sources, which are largely at the equipment level, to their impact on devices, circuits, and systems. Simulation tools are needed, which accurately predict not only nominal values but also their variability, both along the chain of technological processes and at all levels

Based on the assessment of process variability and the state of the art summarized in [1], in the following relevant application results obtained in the "HIErarchische Simulation von PArameterschwankungen in NAnoelektronischen Systemen" (HIESPANA) project at Fraunhofer are presented.

#### II. HIESPANA PROJECT

In the HIESPANA project [2], five Fraunhofer institutes, i.e., the Institute for Integrated Systems and Device Technology (IISB), the Division Design Automation of the Institute for Integrated Circuits (IIS/EAS), the Institute for Microelectronic Circuits and Systems (IMS), the Institute for Industrial Mathematics (ITWM), and the Institute for Algorithms and Scientific Computing (SCAI), have joined forces to develop a software system that allows simulating the impact of process variations. Further contributions have been made by the Vienna University of Technology and the University of Cologne. Own software tools have been combined with third-party tools from software houses and academic sites to establish a hierarchical system of simulators to analyze process variations from their source, e.g., in a lithography process, through device fabrication up to circuit and system levels. Aside from software integration issues, the activities have particularly focused on extension of the lithography (Dr.LiTHO [3], [4]), deposition, and etching simulation tools from IISB; commercial circuit simulators by IIS/EAS to allow for the appropriate simulation of variations; and the behavioral modeling tool Analog Insydes [5] of ITWM to treat variations with statistical reduction methods. SCAI has focused on the improvement and the use of advanced tools for efficiently solving systems of sparse equations (SAMGp [6]), mixed-level device/circuit simulation MECS [7], and PRO-CHAIN [8]. The project software has been evaluated with a demonstrator chip fabricated by IMS. Some examples for the application of these programs for the hierarchical simulation of the impact of variations are given in the following section.

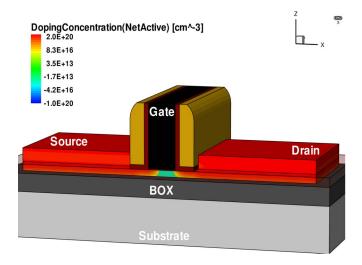

Fig. 1. Geometry and doping concentration of a 32-nm nominal FD SOI transistor, simulated with *Sentaurus Process*.

## III. RESULTS

Planar fully depleted silicon-on-insulator (FD SOI) transistors are among the most promising device architectures for scaling beyond the 22-nm node. For the single-gate (SG) FD SOI transistor shown in Fig. 1, the geometry has been generated with the solid modeling feature of *Sentaurus Process* [9]. Doping and electrical properties of the nominal device have been simulated with *Sentaurus Process* and *Sentaurus Device* [9], respectively.

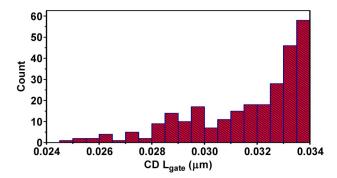

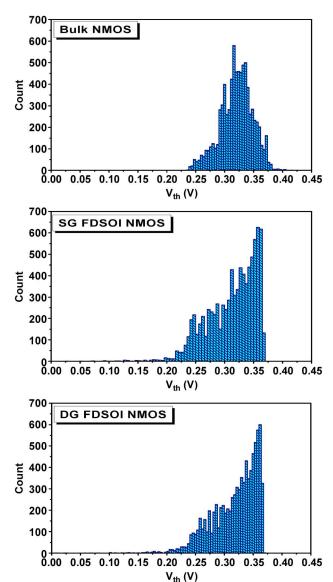

The first example deals with the impact of focus and dose variations in optical lithography on the threshold voltage of 32-nm transistors with different architectures. 32-nm bulk, SG and double-gate (DG) FD SOI devices were investigated. A basic difference in the impact of these variations on bulk and the SOI transistors is shown in this example. Using *Dr.LiTHO*, the lithography process window analysis [allowing up to 10%] critical dimension (CD) variation for the 193-nm water immersion process employed yielded a depth of focus of 52 nm and a "threshold latitude" of 8.5% (see the drawn rectangle in [1, Fig. 1]). In order to study the impact of process variations not only under best conditions, the variation range has been increased to  $\pm 40$  nm around best focus and to a threshold range of 0.25-0.4 (broken-line rectangle in [1, Fig. 1]). A fixed etch bias of 13 nm was assumed. The inherent nature of the lithography process, as discussed in [1, Sec. II], yields the highly asymmetric probability distribution function (pdf) of the CD, as shown in Fig. 2. Process and device simulations using Sentaurus—assuming the gate length distribution from lithography as previously explained—then predict only for the bulk metal-oxide-semiconductor (MOS) field-effect transistor a symmetric threshold-voltage distribution because of the dominating role of the pockets.

For both SOI devices, quite similar highly asymmetric generalized-extreme-value (GEV) distributions result. The pdf's for the bulk and the FD SOI n-channel MOS (NMOS) transistors are shown in Fig. 3. More details on the setup of this simulation, the interpretation, and the additional results are presented in [10].

Fig. 2. Pdf of the transistor gate length subject to variations of focus and dose in optical lithography.

Fig. 3. Pdf of the threshold voltage for different transistor architectures. Bulk NMOS transistor—(top) normal distribution and (middle) SG and (bottom) DG FD SOI NMOSs—both GEV distributed.

In other simulation studies, the impact of across-wafer inhomogeneities in etching [11], silicon thickness variations of SOI wafers [12], and variations in the peak temperature of millisecond anneals [13] has been investigated. Furthermore, a method

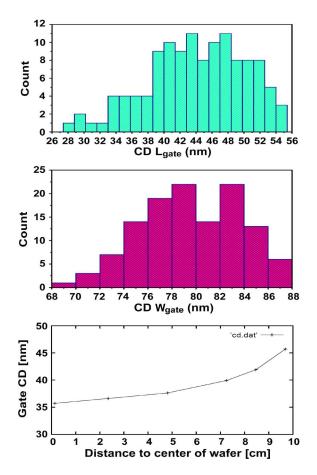

Fig. 4. Variations of gate (top) length and (middle) width due to defocus and dose variations in optical lithography. (Bottom) Variations of gate CD due to variations of etch bias across the wafer, assuming nominal CD after lithography.

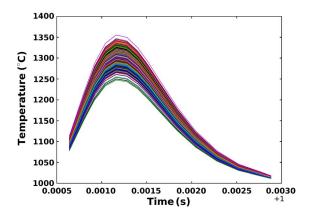

to derive variation-aware compact models was shown [12]. In the following, a comprehensive study is presented, which includes all these effects and methods, including the treatment of correlations as outlined in [1, Sec. IV]. The fabrication of SOI transistors has been simulated, using Dr.LiTHO linked to Sentaurus Process and Sentaurus Device. The impact of focus and dose variations in lithography was included, affecting both the gate width and length (see Fig. 4). The apparent double peak, particularly in the pdf of the gate width, results from the overlay of the highly asymmetric pdf's due to focus variations [10] and a linear pdf due to dose variations. Absolute CD variations are comparable for the gate length and width. However, because a nominal width twice as large as the gate length was used, relative variations are smaller for the width than for the length. The variation of the etch bias was simulated using equipment simulation with the CFD-ACE [14] tool coupled with the 3-D etching simulator ANETCH [11] from IISB (see Fig. 4). For the variation of temperature profiles during millisecond anneal, an approximation already used before [13] was applied (see Fig. 5) and fed into the simulation of annealing with Sentaurus Process.

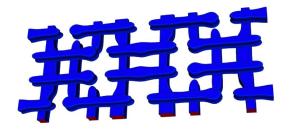

Similar to the first example, 193-nm water immersion lithography has been used. The focus was varied between -80 and 10 nm, and the dose was varied between 21.7 and 24.7 mJ/cm<sup>2</sup>. Two relevant layers (active n+/p+ and polygate) of a standard six-transistor static random-access memory (6T SRAM)

Fig. 5. Variation of temperature profile during millisecond annealing.

Fig. 6. Resist profiles of (vertical) the active n+/p+ layers and (horizontal) the poly layer of four 6T SRAM cells investigated, for fixed values of dose and defocus. The simulated area is  $1.764~\mu m \times 0.754~\mu m$ . The pattern sizes are 45, 55, 65, and 105 nm. Due to periodic boundary conditions in the etching simulations, four cells had to be simulated.

cell were simulated with rigorous mask simulation (solving Maxwell's equations), full vectorial image simulation, and a full resists model, after applying simple optical proximity correction to the attenuated phase-shift mask used. The simulated resist layers are shown in Fig. 6. An etch bias with variations as previously outlined was used. Doping processes were simulated with *Sentaurus Process*, assuming two implantations for source/drain (S/D) extensions and contact formation after the formation of the elevated S/D, respectively. Doses and energies used were low enough to avoid damage concentrations above  $10^{21}$  cm<sup>-3</sup>. Combined spike (nominal peak of 1070 °C) and Flash annealing (1280 °C) was used, as discussed in [12].

Simulation splits were performed as follows: 11 equally distributed values each for both defocus variables and both dose values; 11 equally distributed positions along the wafer radius for the determination of the etch bias; and 11 values for the peak temperature in the Flash annealing, equally distributed between 1230 °C and 1330 °C. Standard BSIM3SOI [15] parameters were extracted from three dimensional (3-D) process and device simulations using *Sentaurus*, including the length and width variations previously mentioned. As demonstrated before [12], temperature variations only affect contact resistances and were therefore only considered as resistance variations in the SRAM cell, together with the width and length variations.

In total, 11<sup>6</sup> variations were simulated with the compact model as previously described. The six transistors in the cell were subject to identical variations, however partly starting from different nominal values due to the layout in lithography. A python interface was used to transfer the process variations that resulted from lithography, etching, and annealing to the

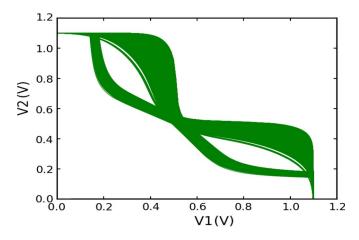

Fig. 7. Classical butterfly characteristic in the READ operation mode of the 6T SRAM cell under the influence of the six statistically independent process variations

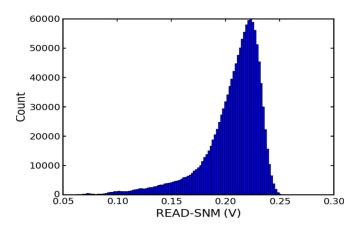

Fig. 8. Variation of the READ SNM of the 6T SRAM cell due to the six statistically independent process variations.

SPICE level. Using this interface, the values of the gate length and width were first included in the SPICE netlist and second used to recalculate the contact resistances of the SRAM cell in combination with the annealing peak temperature, using a compact model extracted before from the 3-D process and device simulations. This procedure was repeated after each simulation step until each combination of process variations was simulated. The computational effort amounted to about 20 days on three conventional 2.5-GHz central processing unit cores.

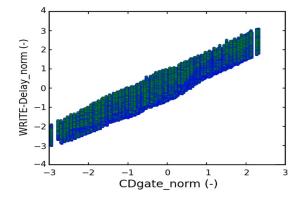

In the following, some key results are presented. Fig. 7 shows the static behavior of the SRAM cell in the READ state, indicating a large spread of the static noise margin (SNM). Fig. 8 shows the pdf of the SNM of the SRAM cell. In both figures, a large variability is visible. As an example for the treatment of the correlations, Fig. 9 shows the strong correlation between the normalized WRITE delay and the normalized variation of the gate length. The spread of the WRITE delay at the fixed gate length indicates the impact of the other variations. Although the nominal values for the gate length differ in the SRAM cell from transistor to transistor, due to proximity effects in lithography, the normalized length variations were identical.

A further detailed discussion of the various correlations and conditional distributions is just a straight-forward postprocessing of the data obtained.

Fig. 9. Correlation between the normalized WRITE delay of the 6T SRAM cell and the normalized transistor gate CD. The values are given as deviation of the varying quantity (e.g., CD) from its mean value normalized to the standard deviation of the varying quantity.

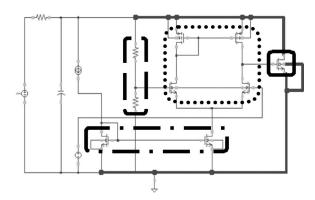

Fig. 10. Voltage-limiter circuit subject to local and global process variations.

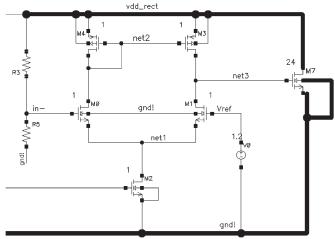

In the next example, the simulation of the impact of local and global process variations on the circuit level is presented for a voltage-limiter circuit, as shown in Fig. 10. This analog building block is used in larger mixed-signal applications, where full-chip verification requires replacement by an equivalent behavioral model. The block model needs to represent the statistical characteristics of the circuit including correlations. The divided voltage at node "in—" is compared with reference  $V_{\rm ref}$ , which, in effect, opens transistor M7 accordingly until the target value for the voltage at node vdd\_rect is reached.

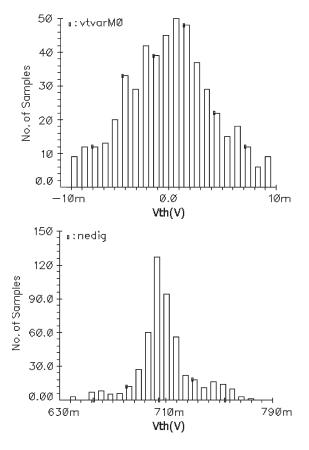

Fig. 11 shows assumed local and global variations of the threshold voltage  $V_{\rm th}$ , which can be readily obtained from coupled equipment, process, and device simulations. Here, it is important to note that not only the sources of variations previously discussed can be considered but also others that may be important for the device or the circuit in question, e.g., dopant fluctuations in the case of transistors with doped channels.

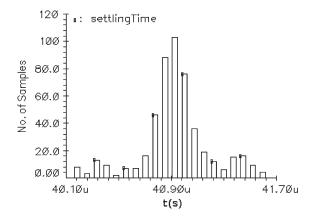

Starting from a SPICE model of the voltage-limiter circuit, the threshold voltages of the respective transistors are changed according to these pdf's. For the local variations, the transistors are independently treated of each other, whereas global variations affect all transistors in the same way. In this example, we examine the variations of the settling time at node vdd\_rect when a voltage ramp is applied.

Fig. 11. Assumed threshold-voltage variations as combination of (bottom) global variations for all NMOS devices and (top) local variations for device M0 in the differential pair of the voltage-limiter circuit.

We obtained the influence of the  $V_{\rm th}$  variations on the settling time separately for local and global variations. This yields two new random variables for the locally and globally induced settling-time variations, respectively.

Now, it is possible to parameterize multiple instances of that block correctly in a hierarchical manner. Again, variations of the locally induced settling time are independently treated, whereas global variations affect all blocks simultaneously. This enables the variation analysis of complex circuits where only a simulation with behavioral models is feasible.

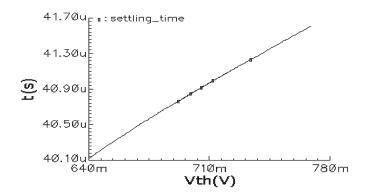

This separated propagation of local and global variations is only possible in the case of linear block behavior. Fig. 12 depicts the nearly linear relation between the threshold voltage and the settling time. Therefore, both distinct distributions yield the same result as the combined distribution that is shown in Fig. 13. Further refinements of the simulations are straightforward, using the approach described in [1, Sec. IV].

For larger circuits or systems, behavioral models, as discussed in [1, Sec. III-G], can be used. In the next step, behavioral models have been extracted using the program Analog Insydes from Fraunhofer ITWM [16], [17]. Due to the symbolic modeling of analog circuits in this tool, it is possible to calculate the sensitivities of output parameters  $y_i$  (here: the output voltage) on input parameters  $p_j$  in an analytical way. Starting with a static behavioral model f(x, p) = 0, where

$$f: R^n \times R^m \to R^n \tag{1}$$

Fig. 12. Observed relation between the threshold voltage and the settling time for the voltage-limiter circuit.

Fig. 13. Simulated frequency distribution of the characteristic settling time when local and global variations of the threshold voltage are present.

sensitivities S are calculated by

$$S = \frac{dy}{dp}\Big|_{(x_0, y_0)} \in R^{q \times m} \tag{2}$$

which is the solution of the equation system

$$\left. \frac{df}{dp}(x,p) \right|_{(x_0,p_0)} = 0 \tag{3}$$

where  $x \in R^n$  denotes the state vector,  $p \in R^m$  is the vector of distributed parameters,  $x_0 \in R^n$  is the operating point, and  $p_0 \in R^m$  is the nominal design point. The system output vector  $y \in R^q$  is a subvector of state x. Then

$$y|_{p} \approx y|_{p_0} + S \cdot (p - p_0) \tag{4}$$

is a first-order approximation of the system output.

The sensitivities in  $(x_0, p_0)$  yield information about the output change depending on parameter variations. Using this approach, the importance of the accuracy of parameters in the production of a circuit can be estimated.

Table I shows the normalized sensitivity  $S \cdot y/p$  of the output voltage of the voltage-limiter circuit to various parameters such as resistances R3 and R5, and the transistor gate width W, length L, oxide thickness  $T_{\rm ox}$ , and threshold voltage  $V_{\rm th}$ , with the frames referring to those in Fig. 14. Obviously, variations of the parameters of the dashed block, i.e., the matching resistors,

TABLE I

SENSITIVITY OF THE OUTPUT VOLTAGE OF THE VOLTAGE-LIMITER

CIRCUIT WITH RESPECT TO VARIOUS DEVICE PARAMETERS

| normalized sensitivity | parameters                        |

|------------------------|-----------------------------------|

| ~ 0.65                 | R3, R5                            |

| ~ 0.56 – 0.72          | Tox, Toxm                         |

| ~ 0.51 – 0.53          | Vth0                              |

| ~ 0.039 - 0.045        | NLX                               |

| ~ 0.035 - 0.037        | U0                                |

| ~ 0.02 - 0.03          | W, L                              |

| ~ 0.005                | Tox, Toxm, Vth0, NLX, U0,<br>W, L |

| ~ 0.003                | Tox, Toxm, Vth0, NLX, U0, W, L    |

Fig. 14. Voltage-limiter circuit. Some blocks are marked, which have different sensitivity with respect to variations.

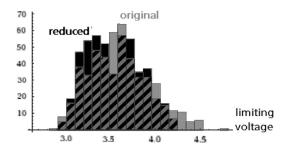

Fig. 15. Pdf of the output voltage of the current-limiter circuit for the original and reduced behavioral models.

and of some parameters of the dotted block have the largest impact on the output voltage.

Furthermore, symbolic statistical order reduction, including treatment of the variations, has been implemented in *Analog Insydes*. This allows for the minimization of the number of equations in the behavioral model (1), largely maintaining accuracy while reducing simulation time. An example is given in Fig. 15, where the pdf of the output voltage is compared between the original and reduced models, yielding good agreement. Table II characterizes the reduced model in terms of the order reduction and the simulation time.

TABLE II

COMPARISON OF MODEL ORDERS AND SIMULATION TIME FOR

THE ORIGINAL AND REDUCED BEHAVIORAL MODELS

|          | model order    | simulation time [s] |

|----------|----------------|---------------------|

| original | 353            | 18.96               |

| reduced  | 157<br>(44.5%) | 3.14<br>(16.5%)     |

As a promising approach for enhancing the splitting process to obtain the  $\mathbb{R}^k$  vectors (see [1, Sec. IV]), as well as for controlling computational and data complexity, the PRO-CHAIN strategy [8], [18] has been recently transferred to the process-to-device/circuit simulation chains. PRO-CHAIN has been originally developed for the forming-to-crash and casting-to-crash chains arising in the automotive industry. Corresponding mathematical software modules have been integrated into the DesParO software [19] for parameter sensitivity analysis, interpolation, and robust multiobjective optimization. The main steps of the current PRO-CHAIN version for the process-to-device/circuit simulation chain are:

- 1) at the process level

- a) input: parameters, along with ranges, distribution functions (determined or assumed), and correlations;

- b) iterative analysis by means of *DesParO*: process simulations performed based on a first experimental design [design of experiment (DoE)] followed by a sensitivity analysis of results (functionals on discretization grids; DF-ISE format [9]) and an interpolation and a compression of these functionals and statistical measures for the overall parameter range; principal component analysis combined with interpolation based on radial basis functions and polynomial detrending is used here; *DesParO* sets up an extended DoE and requests another analysis if the current DoE does not allow for a sufficient interpolation; etc.;

- c) output: database (compressed) describing simulation results, along with interpolated statistics on, e.g., the final grid of the nominal simulation (without variations);

- 2) at the device level or the coupled circuit and device level [Multiphysical Electric Circuit Simulator (MECS)]

- a) input: database from the process level, mapped to the grid for device simulation if necessary;

- b) iterative analysis by means of *DesParO* for results (functionals on grids and/or device characteristics);

- c) output: database (compressed) including statistics; and

- 3) at the circuit level

- a) input: mapped database from the device level or parameters, along with variations and correlations;

- b) iterative analysis by means of *DesParO*.

In particular *PRO-CHAIN* together with the mixed-level simulator *MECS* allows for a deep analysis of the impact of

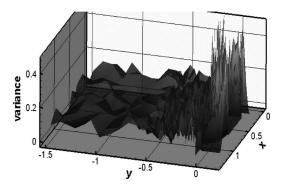

Fig. 16. Variance of the potential for the p-channel MOS (PMOS) based on a DoE with 17 experiments for variations of the gate length and the channel implantation. On the x- and y-axes, spatial coordinates are shown in micrometers. The nitride spacers and the oxide areas are located on the right-hand side.

parameter variations on the process level to the circuit level if, at least for some devices, compact modeling shall be avoided and replaced by a tightly coupled circuit and device simulation.

The exemplary output of the statistical analysis of the process-to-device simulation chain for the HIESPANA demonstrator is shown in Fig. 16. The gate length and the channel implantation have been simultaneously varied for a PMOS and an NMOS in an inverter by means of a DoE with 17 experiments in total. *Sentaurus Process* and *MinimosNT* have been used. The results of the device simulations have been mapped (interpolated) to the resulting grid of the nominal device simulation. Variances are substantial, particularly in and/or around nitride and oxide.

#### IV. CONCLUSION

Hierarchical coupled equipment, process, device, circuit, and system simulation is a valuable approach to assess the impact of variations and to decide about the best equipment, process, and device architectures options and the best tradeoffs to be taken. Technologies with normal distributions of process parameters can lead to highly asymmetric parameter distributions at the device level. A cooptimization of the nominal performance of devices, circuits, and systems and of their variability is of paramount importance because these targets may compete against each other.

## ACKNOWLEDGMENT

The authors want to acknowledge the contributions from their colleagues at Fraunhofer A. Burenkov, T. Fühner, D. Kunder (IISB), T. Klick, C. Sohrmann (IIS/EAS), T. Feldengut, S. Kolnsberg, A. Strack, J. Wang (IMS), T. Halfmann, M. Hauser, P. Lang, O. Schmidt (ITWM), C. Hettkamp, B. Klaassen, N. Männig. P. Thum, L. Torgovitski (SCAI), and of J. Cervenka (TU Vienna), C. Tischendorf, M. Selva Soto (Univ. Köln).

## REFERENCES

- [1] J. Lorenz, E. Bär, T. Clees, R. Jancke, C. Salzig, and S. Selberherr, "Hierarchical simulation of process variations and their impact on circuits and systems: Methodology," *IEEE Trans. Electron Devices*, vol. 58, no. 8, pp. 2218–2226, Aug. 2011.

- [2] [Online]. Available: www.hiespana.fraunhofer.de

- [3] [Online]. Available: www.drlitho.com

- [4] P. Evanschitzky, F. Shao, A. Erdmann, and D. Reibold, "Simulation of larger mask areas using the waveguide method with fast decomposition technique," in *Proc SPIE*, Grenoble, France, 2007, vol. 6730, pp. 1–9.

- [5] [Online]. Available: www.analog-insydes.de

- [6] K. Stüben and T. Clees, SAMG User's Manual v. 22c. Sankt Augustin, Germany: Fraunhofer Inst. SCAI, 2005.

- [7] M. Selva Soto and C. Tischendorf, "Numerical analysis of DAEs from coupled circuit and semiconductor simulation," *Appl. Numer. Math.*, vol. 53, no. 2–4, pp. 471–488, May 2005.

- [8] D. Steffes-lai and T. Clees, "Efficient stochastic analysis of process chains," in *Proc. 1st Int. Fraunhofer Multiphys. Conf.*, Bonn, Germany, 2010, accepted for publication.

- [9] [Online]. Available: www.synopsys.com

- [10] J. Lorenz, C. Kampen, A. Burenkov, and T. Fühner, "Impact of lithography variations on advanced CMOS devices," in *Proc. Int. Symp. VLSI Technol.*, Syst. Appl., Hsinchu, Taiwan, 2009, pp. 17–18.

- [11] E. Bär, D. Kunder, P. Evanschitzky, and J. Lorenz, "Coupling of equipment simulation and feature-scale profile simulation for dry-etching of polysilicon gate lines," in *Proc. SISPAD*, Bologna, Italy, 2010, pp. 57–60.

- [12] C. Kampen, A. Burenkov, J. Lorenz, and H. Ryssel, "FDSOI MOSFET compact modeling including process variations," in *Proc. ULIS Conf.*, Glasgow, U.K., 2010, pp. 173–176.

- [13] C. Kampen, A. Burenkov, and J. Lorenz, "On the influence of Flash peak temperature variations on Schottky contact resistances of 6-T SRAM cells," in *Proc. ESSDERC*, Sevilla, Spain, 2010, pp. 289–292.

- [14] Simulator CFD-ACE+, ESI Group, 2009.

- [15] BSIMSOI3.1 MOSFET MODEL, User's Manual, Dept. Elect. Eng. Comput. Sci., Univ. California, Berkeley, CA, 2003.

- [16] C. Salzig, M. Hauser, and A. Venturi, "Using sensitivities for symbolic analysis and model order reduction of systems with parameter variation," in *Proc. 16th ECMI*, Wuppertal, Germany, 2010, in print.

- [17] C. Salzig and M. Hauser, "Design of robust electronic circuits for yield optimization," in *Proc. XIth Int. Workshop SM2ACD*, Tunis-Gammarth, Tunesia, 2010, pp. 1–5.

- [18] D. Steffes-lai, L. Nikitina, and T. Clees, "Vorrichtung und Verfahren zum Bearbeiten einer Prozess-Simulationsdatenbasis eines Prozesses," Aug. 5, 2010, International patent application PCT/EP2010/061450.

- [19] T. Clees, N. Hornung, L. Nikitina, I. Nikitin, and D. Steffes-lai, *DesParO v.1.9 User's Manual*. Sankt Augustin, Germany: Fraunhofer SCAI, 2009. [Online]. Available: www.scai.fraunhofer.de/desparo.html

Jürgen K. Lorenz (M'01) was born in Stockelsdorf, Germany, in 1957. He received the "Diplom-Mathematiker" and "Diplom-Physiker" degrees from the Technical University of Munich, Munich, Germany, in 1982 and 1984, respectively, and the Dr.-Ing. degree in electrical engineering from the University of Erlangen–Nuremberg, Erlangen–Nuremberg, Germany, in 2000.

He joined Fraunhofer in 1983. Since 1985 he is in charge of the technology simulation department of the then newly founded Fraunhofer IISB in Erlangen.

His main subjects are the development of physical models and programs for semiconductor process simulation and the required algorithms. He authored or co-authored about 120 papers. During the last 18 years he has been involved in 27 European projects, for 7 of which he acted as coordinator.

Dr. Lorenz is member of the Electrochemical Society, and has repeatedly been or is a member of the technical committees of the ESSDERC, SISPAD, and IEDM conferences. Following requests from industry, he has been contributing since 2000 as expert to the preparation of the International Technology Roadmap on Semiconductors and has been the chairman for its Modeling and Simulation chapter since 2002.

**Eberhard Bär** was born in Darmstadt, Germany, in 1967. He received the "Diplom-Physiker" degree with specialization in experimental solid-state physics from Darmstadt University of Technology, Darmstadt, in 1992 and the Dr.-Ing. degree in electrical engineering with specialization in semiconductor technology from the University of Erlangen–Nuremberg, Erlangen–Nuremberg, Germany, in 1998.

Since 1992, he has been with the Fraunhofer Institute for Integrated Systems and Device Technology

(IISB), where he is currently in charge of the topography simulation group. His current research interests focus on the development and application of topography simulation tools in semiconductor technology. He is author or coauthor of 40 publications in journals and conference proceedings.

process variability.

**Christian Kampen** received the Dipl.-Ing. degree in electrical engineering from the Technical University of Munich, Munich, Germany, in 2006.

Since August 2006, he has been with the Fraunhofer Institute of Integrated Systems and Device Technology (IISB), Erlangen, Germany. He has authored or coauthored about 20 technical publications. His main research interests are technology computer-aided design simulations of complementary metal–oxide–semiconductor devices, integrated circuits, contact resistances, mechanical stress, and

Tanja Clees was born in Aachen, Germany, in 1977. She received the "Diplom-Mathematikerin" degree with minor subject of physical chemistry and the Dr. rer. nat. degree in applied mathematics from the University of Cologne, Cologne, Germany, in 1999 and 2004, respectively.

She joined Fraunhofer SCAI (till 2001 GMD SCAI) in Sankt Augustin, Germany in 1998. From 2000 to 2006 she worked as a scientist for and chief software developer of the linear solver library *SAMG*. Since 2007, she has been in charge of the

robust design group and its two software packages *DesParOand DiffCrash*. Her main subjects are hierarchical solvers for large sparse linear systems, as well as statistical analysis and exploration of dependences of highly resolved simulation results from parameter variations and robust multiobjective parameter optimization.

development.

**Uwe Paschen** received the Diploma in physics from the University Frankfurt am Main, Frankfurt am Main, Germany, and the Ph.D. degree in physics from the Technical University of Karlsruhe, Karlsruhe, Germany.

He was a Postdoctoral Fellow with the University of Oregon, Eugene. Since 1998, he has been with the Fraunhofer Institute for Microelectronic Circuits and Systems (IMS), Duisburg, Germany. He is heading a group that is responsible for complementary metal–oxide–semiconductor process and device

Peter Evanschitzky received the Diploma in electrical engineering from the Universität des Saarlandes, Saarbrücken, Germany, and the Ph.D. degree in the field of optical surface measurement techniques from the Technische Universität München, Munich, Germany, where he developed a simulator for interferometrical speckle measurement systems and a new interferometrical surface shape measurement system for rough surfaces.

He is currently a scientist with the Fraunhofer Institute for Integrated Systems and Device Technol-

ogy (IISB), Erlangen, Germany. His field of research is lithography simulation. He has coauthored the lithography simulator *Dr.LiTHO*.

Christian P. J. Salzig was born in Boppard, Germany, in 1980. He received the Diplom-Technomathematiker degree with minor subject of electrical engineering from the Technische Universität (TU) Kaiserslautern, Kaiserslautern, Germany.

From 2005 to 2008, he was awarded with a Ph.D. scholarship of the Graduate School with the Department of Mathematics, TU Kaiserslautern. Since 2008, he has been a scientific assistant at the Fraunhofer Institute for Industrial Mathematics (ITWM). His main subjects are statistics, modeling

of nonlinear systems, and control theory.

Mr. Salzig has been a member of the developer team of the symbolic electronic design automation tool *Analog Insydes* since 2001.

**Roland Jancke** was born in Berlin, Germany, in 1970. He received the Diploma in electrical engineering from the Technical University of Dresden, Dresden, Germany, in 1996.

Since 1996, he has been with the Division Design Automation of the Fraunhofer Institute for Integrated Circuits (IIS/EAS), Dresden, where he is currently heading the group for technology oriented modeling. His main scientific interest is in behavioral modeling of analog and mixed-signal circuits, with focus on reliability and technology-induced effects.

Mr. Jancke is a member of the Verband der Elektrotechnik, Elektronik und Informationstechnik (VDE) and is actively participating in its working group on design methods for analog circuits.

**Siegfried Selberherr** (M'79–SM'84–F'93) was born in Klosterneuburg, Austria, in 1955. He received the Diplomingenieur degree in electrical engineering and the Ph.D. degree in technical sciences from the Technische Universität Wien, Vienna, Austria, in 1978 and 1981, respectively.

Since 1984, he has been holding the *venia docendi* on computer-aided design. Since 1988, he has been the Chair Professor of the Institut für Mikroelektronik. From 1998 to 2005, he was the Dean of the Fakultät für Elektrotechnik und Informationstechnik.

His current research interests are modeling and simulation of problems for microelectronics engineering.

Dr. Selberherr is a member of the ACM, the ECS, the SIAM, and the VDE.