## Modeling Spin-Based Devices in Silicon

V. Sverdlov, H. Mahmoudi, A. Makarov, D. Osintsev, J. Weinbub, T. Windbacher, and S. Selberherr

Institute for Microelectronics, TU Wien, Gußhausstraße 27–29/E360, 1040 Wien, Austria e-mail: sverdlov@iue.tuwien.ac.at

Continuous miniaturization of CMOS devices made the breath taking increase in performance of integrated circuits become a magnificent reality. Numerous tough problems were solved on this exciting journey; however, growing technological challenges and soaring costs will gradually bring CMOS scaling to an end. This puts foreseeable limitations to the future performance increase, and research on alternative technologies and computational principles becomes paramount.

The spin of an electron possesses several exciting properties suitable for future devices. It is characterized by two projections on a chosen axis – up or down, and it can change its orientation rapidly by utilizing an amazingly small amount of energy. Employing spin, as a compliment to electron charge, opens new exciting opportunity for developing conceptually new non-volatile nanoelectronic devices for future low power applications [1].

Silicon, the main material of microelectronics, is characterized by weak spin-orbit interaction and zero-spin nuclei, which gives rise to a long spin lifetime. This makes silicon perfectly suited for spin-driven applications. Spin propagation through an undoped 350µm thick silicon wafer [2] gives hope for fabrication of silicon spin-based devices in the near future increasingly likely.

The success of microelectronics has been assisted by smart Technology Computer-Aided Design tools. Because a commercial support for spin applications is entirely absent it is mandatory to develop a simulation environment for spin-based devices in silicon [3]. Understanding spin-polarized transport in silicon and in compatible hysteretic materials facilitates inventing, modeling, and optimizing prototypes of spin-based switches and memory devices for the 21<sup>st</sup> century.

The canonical spin field-effect transistor (SpinFET) proposed by Datta and Das [4] is a switch which employs the electron spin to modulate the current through the device. The

SpinFET is composed of a semiconductor channel region sandwiched between two ferromagnetic contacts. The source contact injects spin-polarized electrons in the semiconductor. The gate-voltagedependent spin-orbit interaction in the channel is used to modulate the current through the SpinFET. It causes the electron spin to precess during the electron propagation through the channel. Only the electrons with their spins aligned to the drain contact's magnetization can leave the channel through the drain contact, thus contributing to the current. For practical realization of a SpinFET it is mandatory to solve the problem of spin injection and detection as well as spin propagation, control, and manipulation [5]. Successful spin injection from different ferromagnets into a number of semiconductors through several oxides has been demonstrated [5-7]. Regardless the undoubted progress, the level of spin accumulation which displays several orders of magnitude discrepancy [5] with the standard theory is not yet understood.

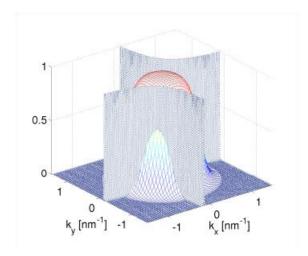

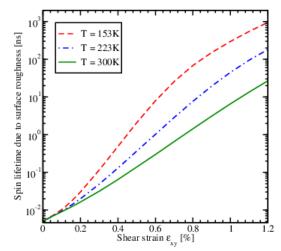

Close to interfaces the spin diffusion length and relaxation time at room temperature appear to be shorter with much weaker temperature dependence than in the bulk [7]. Thus, external spin relaxation mechanisms due to the presence of a Si/SiO<sub>2</sub> interface become central, and methods to boost the spin lifetime in MOSFETs are needed. We utilize a spin-dependent k·p Hamiltonian [8], where only the [001] valleys are included. Without strain the subbands are degenerate. unprimed degeneracy produces a large mixing between the spin-up and spin-down states from the opposite valleys, resulting in hot spots characterized by strong spin relaxation. The hot spots are defined by the condition  $D\varepsilon_{xy} - \hbar^2 k_x k_y \left(\frac{1}{m_t} - \frac{1}{m_0}\right) = 0$ , where D = 14 eV is the shear strain deformation potential,  $m_t$  is the transverse mass, and  $\varepsilon_{xy}$  is shear strain. In strained samples the hot spots are moved away from the center of the twodimensional Brillouin zone (Fig.1), which reduces their contribution to spin relaxation. Thus, strain used to enhance on-current in nano-CMOS can significantly boost spin lifetime [9] (Fig.2).

The spin-orbit interaction in silicon films is due to the interface-induced inversion symmetry breaking [10]. Silicon nanowires with [100] orientation display a stronger modulation of the conductance as function of spin-orbit interaction and are preferred for practical realizations of SpinFETs [11]. However, the channel length required to manipulate spin is about a micron. The spin degree can be introduced into nano-CMOS by using ferromagnetic source and drain contacts [1], however, due to the low spin injection efficiency at room temperature [12], it has not yet been realized. Many new ideas to build spin-based devices have been recently introduced [5], [13]. To be successful, these devices must operate at room temperature and be compatible with CMOS. Albeit many exciting inventions are lying ahead, the practical option for the near future is to benefit from combining CMOS with magnetic tunnel junctions (MTJs). MTJ-based spin transfer torque MRAM is CMOS compatible, non-volatile, and close to production. A combination of a MTJ with a MOSFET to a pseudo-spin-MOSFET appears to be very beneficial [14]. Arrays made of MTJs offer new opportunities to build non-conventional non-volatile logic-in-memory systems [15].

This work is supported by the European Research Council through the grant #247056 MOSILSPIN.

Fig. 1. Spin relaxation hot spots in strained samples.

## REFERENCES

- [1] S. Sugahara and J. Nita, Spin-transistor electronics: an overview and outlook, Proc. IEEE 98, 2124 (2010).

- [2] B. Huang, D. J. Monsma, and I. Appelbaum, Coherent spin transport through a 350 micron thick silicon wafer, Phys.Rev.Lett. 99, 177209 (2007).

- [3] http://www.iue.tuwien.ac.at/index.php?id=software.

- [4] S. Datta and B. Das, Electronic analogue of the electrooptical modulator, Appl.Phys.Lett. 56, 665 (1990).

- [5] R. Jansen, Silicon spintronics, Nature Materials 11, 400 (2012).

- [6] C.H. Li, O.M.J. van t'Erve, and B.T. Jonker, Electrical injection and detection of spin accumulation in silicon with magnetic metal/silicon dioxide contacts, Nature Commun. 2, 245 (2011).

- [7] T. Suzuki et al., Room-temperature electron transport in highly doped Si channel, Appl.Phys.Express 4, 023003 (2011).

- [8] P. Li and, H. Dery, Spin-orbit symmetries of conduction electrons in silicon, Phys.Rev.Lett. 107, 107203 (2011).

- [9] D. Osintsev, V. Sverdlov, and S. Selberherr, Spin lifetime enhancement by shear strain in thin silicon-on-insulator films, Proc. 223<sup>rd</sup> ECS Meeting, accepted (2013).

- [10] M. Prada, G. Klimeck, and R. Joynt, Spin-orbit splittings in Si/SiGe quantum wells: from ideal Si membranes to realistic heterostructures, New J.Phys. 13, 013009 (2011).

- [11]D. Osintsev et al., Temperature dependence of the transport properties of spin field-effect transistors built with InAs and Si channels, Solid-State Electron. 71, 25 (2012).

- [12]S. Zhang et al., Electrical spin injection and detection in silicon nanowires trough oxide tunnel barrier, Nano Lett., online version **DOI:** 10.1021/nl303667v (2013).

- [13]J. Fabian et al., *Semiconductor spintronics*, Acta Physica Slovaca **57**, 565 (2007).

- [14]Y. Shuto et al., Design and performance of pseudo-spin-MOSFET using nano-CMOS devices, Proc. IEDM, 685 (2012).

- [15]H. Mahmoudi, V. Sverdlov, and S. Selberherr, MTJ-based implication logic gates and circuit architecture for largescale spintronic stateful logic systems, Proc. ESSDERC, 254 (2012).

Fig. 2. Spin lifetime enhancement by shear strain.