Contents lists available at SciVerse ScienceDirect

# Microelectronic Engineering

journal homepage: www.elsevier.com/locate/mee

# Gate current random telegraph noise and single defect conduction

B. Kaczer <sup>a,\*</sup>, M. Toledano-Luque <sup>a</sup>, W. Goes <sup>b</sup>, T. Grasser <sup>b</sup>, G. Groeseneken <sup>a,c</sup>

### ARTICLE INFO

Article history:

Available online 30 March 2013

Keywords: Metal-Oxide-Semiconductor Field-Effect Transistor (MOSFET) Random Telegraph Noise (RTN) Trapping Gate current

## ABSTRACT

The properties of Random Telegraph Noise (RTN) in the gate current of nanoscaled Metal-Oxide-Semiconductor Field-Effect Transistors (MOSFET) are discussed. While the gate current RTN capture and emission times depend strongly on temperature and gate voltage, the RTN amplitude, corresponding to single gate oxide leakage path, appears independent of temperature and scaling with the gate current. The RTN amplitude is observed to reach up to tens of percent of gate current. In carrier separation measurements the fluctuations typically appear in one component only. A correlation of drain and gate current fluctuations allows linking the charge and conduction states of a single gate oxide trap. A model for drain current RTN involving a metastable state is extended to include conduction through the single trap and gate current RTN.

© 2013 Elsevier B.V. All rights reserved.

### 1. Introduction

Although only a few defects will be present in the gate dielectric of deeply-downscaled CMOS devices, their relative impact will be considerable [1]. For example, an individual charged trap can significantly alter the channel current  $I_D$  of a nm-sized FET, thus affecting the performance of the entire circuit [2]. The ability to observe these single-carrier events has one advantage—it allows us to study time-dependent degradation mechanisms at the ultimate, "atomistic" level. In this "bottom-up" approach, the overall degradation is then described as a concomitant impact of an ensemble of individual defects, naturally yielding a physically-based description of the time-dependent variability.

The properties of individual defects and their impact on  $I_D$  have been investigated in great detail [3–7]. Recently reported observations linked the same defects to fluctuations in another important FET parameter—gate current  $I_G$  [8,9]. Here we discuss the mechanism responsible for gate leakage through an individual defect in both n- and pFETs, attempting to provide a unified picture for these fluctuations. Insights into the mechanism controlling individual defect conduction should in turn lead to better general understanding of gate leakage and its degradation during FET operation [10].

#### 2. Experimental

Both n- and p-channel FET devices were investigated with EOT = 2.3 nm SiON gate oxide, 70 nm nominal gate length corre-

sponding to  $\sim\!35$  nm effective channel length and 90 nm gate width [9]. The FET currents were simultaneously measured with a pair of Keithley 2636 units with a sampling rate of 20 ms. All measurements reported here were done at 25 °C unless noted otherwise.

# 3. Results and discussion

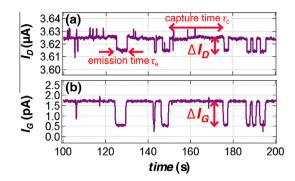

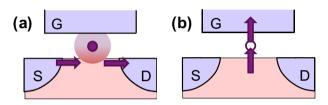

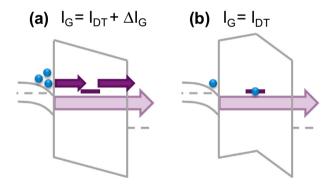

Intermittent capture and emission of charge in a single gate oxide defect will result in so-called random telegraph noise in the drain current ( $I_D$ -RTN; Fig. 1a). Note that the lower  $I_D$  level corresponds to the trap being occupied, resulting in Coulombic blocking of a part of the FET conduction channel (Fig. 2a). The process is characterized by defect capture time  $\tau_c$ , emission time  $\tau_e$ , and the change in  $I_D$  due to the single trap  $\Delta I_D$  (Fig. 1a).

Trapping and detrapping into this defect also result in *fluctuations in the gate current*  $\Delta I_G$  (Figs. 1b and 2b) [11]. Most notably, the  $I_G$  and  $I_D$  fluctuations are correlated [9], allowing us to link the charged state of the defect with the lower  $I_G$ -RTN level. This crucial information could not be obtained in previous work on large-area? MOS *capacitors* [11].

The  $\tau_c$  and  $\tau_e$  characterizing both correlated RTN processes are strongly voltage and temperature dependent [9] (widely distributed  $E_A \sim 0.1$ –1.5 eV), the latter suggesting exchange of energy with the lattice during the charge capture/emission process [12,13].

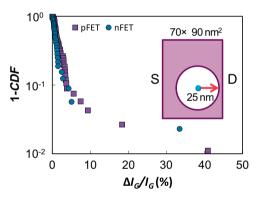

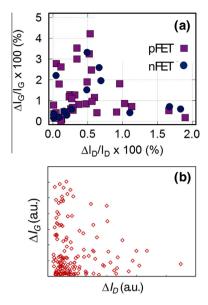

The crucial issue is the mechanism through which the captured charge affects  $I_G$ . Here we note the large magnitude of  $\Delta I_G$  fluctuations in Fig. 1b (about 70% of  $I_G$ ). The distribution of these fluctuations in other devices is shown in Fig. 3. We note that a change of 30% in  $\Delta I_G/I_G$  would correspond to uniform gate leakage being dis-

<sup>&</sup>lt;sup>a</sup> Imec, Kapeldreef 75, B-3001 Leuven, Belgium

<sup>&</sup>lt;sup>b</sup> TU Vienna, Vienna, Austria

c ESAT, KU Leuven, Leuven, Belgium

<sup>\*</sup> Corresponding author. Tel.: +32 16 281 557. E-mail address: kaczer@imec.be (B. Kaczer).

**Fig. 1.** Random telegraph noise (RTN) in (a) the drain current  $I_D$  ( $V_D$  = 100 mV) and (b) the gate current  $I_G$  ( $V_G$  = 0.7 V) is correlated in a deeply scaled nFET [9]. Data obtained at 45 °C.

**Fig. 2.** A schematic illustration of a single trap influencing both (a) the channel and (b) the gate currents.

**Fig. 3.** The relative magnitude of gate current fluctuations can reach more than 10% in about 3% of devices. Inset:  $\Delta I_G/I_G = 30\%$  corresponds to  $I_G$  being "disabled" over an area with  $\sim$ 25 nm radius around the charged defect.

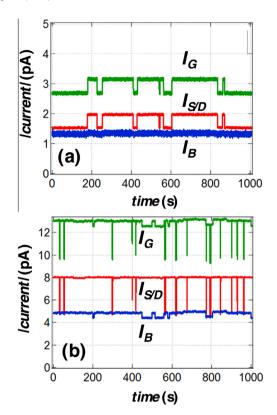

abled over a circular area with  $\sim\!25$  nm radius around the charged defect in our  $70\times90$  nm² devices [14]. Although a charge capture does result in the local increase of the gate oxide tunneling barrier, such extent suggests that this is an unlikely scenario. The same argument also rules out local electrostatic repelling of supply carriers in the injection electrode in the vicinity of the trapped charge as the origin of the fluctuations. This view is further corroborated by charge-separation experiments (Fig. 4) in which  $I_G$ -RTN is reflected in *either* hole *or* electron components (the above barrier modulation would affect both components).

A more likely process involves enhanced conduction through the trap when it is unoccupied by an electron (Fig. 5 for nFET, pFET not shown). Such a process would be most efficient for traps close to the center of the oxide [15], readily explaining why there are no defects causing both large  $\Delta I_G$  and large  $\Delta I_D$  (Fig. 6a) [9]. The same correlation (Fig. 6b) can be qualitatively constructed using this assumption, combined with the impact of a charged trap on  $I_D$  depending on the distance of the trap from the critical point of a source-drain percolation path [16].

**Fig. 4.** Carrier separation experiment ( $V_D = V_S = V_B = 0$  V) in nm-sized (a) nFET and (b) pFET in accumulation. In most cases, fluctuations in  $I_G$  are correlated with one component only.

**Fig. 5.** Schematic of the process in an nFET. (a) An *unoccupied* trap locally contributes to the extra current  $\Delta I_G$ , cf. Fig. 1. Overall direct tunneling (DT) component forms the background. (b) The *occupied* trap disables  $\Delta I_G$  conduction path. A local oxide barrier increase and a repulsion of supply carriers are also shown but are ruled out as decisive, cf. Fig. 3.

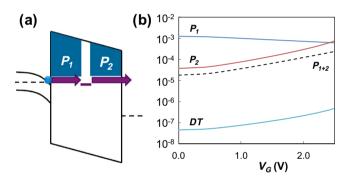

Decoherent tunneling through a trap near the center of the oxide (Fig. 7) will also result in a similar voltage dependence of the background  $I_G$  and the  $\Delta I_G$  component—an observation recorded (but not fully appreciated) already in [11] and confirmed in [9].

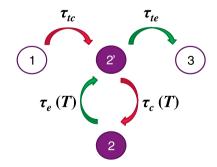

Finally, following the model in [4], the state diagram describing the entire  $I_G$ -RTN mechanism relying on a metastable state is shown in Fig. 8. In this picture, the temperature *independence* of the  $\Delta I_G$  component (observed in a T range of  $\sim 50$  K [9,11]) is associated with the very fast time constants  $\tau_{tc}$  and  $\tau_{te}$  ( $\Delta I_G \sim 10$  pA corresponds to  $\sim 10^{-8}$  s) describing tunneling into and out of the trap. The strong T dependence of the RTN constants  $\tau_c$  and  $\tau_e$  is then due to thermal barriers between the metastable and stable charged states of the trap [4].

**Fig. 6.** (a) Correlation plot of relative changes in  $I_D$  and  $I_G$  ( $I_G = \sim 10$  pA). Note that upper right corner (large  $I_D$  and large  $I_G$  fluctuations) is unpopulated. (b) The same trend can be qualitatively reproduced by the proposed picture.

**Fig. 7.** (a) Band diagram showing the tunneling probabilities into and out of the trap  $P_1$  and  $P_2$ . (b) A first-passage-time combination of  $P_1$  and  $P_2$  (for a trap positioned 25% into the oxide) will have voltage dependence very similar to the direct tunneling probability ( $\sim I_G$ ).

**Fig. 8.** State diagram describing the  $I_G$ -RTN process. A carrier tunnels from injecting electrode 1 into metastable state 2' and either continues to the opposite electrode 3, contributing to  $\Delta I_G$ , or becomes captured in state 2, disabling the conduction path.

## 4. Conclusions

The properties of Random Telegraph Noise (RTN) in the gate current of nanoscaled Metal-Oxide-Semiconductor Field-Effect

Transistors (MOSFET) have been discussed. A correlation of drain and gate current fluctuations allows us to link the charge and conduction states of a single gate oxide trap. A model for drain current RTN involving a metastable state is extended to include conduction through the single trap and gate current RTN.

# Acknowledgments

This work was performed as part of imec's Core Partner Program. It has been partially supported by the European Commission under the 7th Framework Programme (Collaborative project MORDRED, contract No. 261868).

#### References

- A. Ghetti, C.M. Compagnoni, A.S. Spinelli, A. Visconti, IEEE Trans. Electron Devices 56 (2009) 1746–1752.

- [2] B. Kaczer et al., in: Proceedings of International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2011, pp. XT.3.1–XT.3.5.

- [3] M. Toledano-Luque et al., Microelectron. Eng. 88 (2011) 1243–1246.

- [4] T. Grasser et al., in: Proceedings of International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 2010, pp. 16–25.

- [5] V. Huard et al., in: Proceedings of International Reliability Physics Symposium (IRPS), Phoenix, AZ, USA, 2008, pp. 289–300.

- [6] V. Huard et al., in: Proceedings of International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 2010, pp. 655–664.

- [7] T. Nagumo, K. Takeuchi, T. Hase, Y. Hayashi, in: IEEE International Electron Devices Meeting (IEDM), 2010, pp. 28.3.1–28.3.4.

- [8] C. Chia-Yu et al., in: Proceedings of International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2011, pp. 3A.2.1–3A.2.6.

- [9] M. Toledano-Luque et al., in: Proceedings of International Reliability Physics Symposium (IRPS), Anaheim, CA, USA, 2012, pp. XT.5.1–XT.5.6.

- [10] A. Teramoto et al., J. Vac. Sci. Technol. B 27 (2009) 435.

- [11] M.O. Andersson, Z. Xiao, S. Norrman, O. Engström, Phys. Rev. B 41 (1990) 9836–9842.

- [12] T. Grasser, Microelectron. Reliab. 52 (2012) 39–70.

- [13] L. Vandelli et al., in: Proceedings of the European Solid-State Device Research Conference (ESSDERC), 2010, pp. 388–391.

- [14] F. Crupi et al., J. Appl. Phys. 106 (2009) 073710.

- 15] D. Ielmini, A.S. Spinelli, A.L. Lacaita, A. Modelli, IEEE Trans. Electron Devices 49 (2002) 1955–1961.

- [16] J. Franco et al., IEEE Electron Device Lett. 33 (2012) 779–781.