#

M. Molnár<sup>1,2\*</sup>, V. Palankovski<sup>2</sup>, D. Donoval<sup>1</sup>, J. Kuzmík<sup>3</sup>, J. Kováč<sup>1</sup>, A. Chvála<sup>1</sup>, J. Marek<sup>1</sup>, P. Príbytný<sup>1</sup>, and S. Selberherr<sup>2</sup>

e-mail: marian.molnar@stuba.sk, molnar@iue.tuwien.ac.at

Abstract Promising material properties of GaN, e.g., wide bandgap, high saturation velocity, and high thermal stability, make it an excellent material for high-power, high-frequency, and high-temperature applications. For some specific applications which require the device to operate at elevated temperatures, modeling and simulation provide very meaningful insights about the thermal device behavior. In this work, the DC device behaviour at 300K and at elevated temperatures is studied, both experimentally and by means of two-dimensional device simulations. Very good agreement between the measurements and the simulation results with Minimos-NT is achieved using the hydrodynamic transport model including self-heating and carefully tuned impact ionization effects.

Keywords: HEMT, characterization, modeling, simulation, temperature

#### 1. INTRODUCTION

GaN-based HEMTs attract strong attention due to their material-related properties, such as wide bandgap (>3.4eV), high carrier saturation velocity (>2.5×10<sup>7</sup>cm/s), excellent thermal conductivity [1], and high breakdown field (4MV/cm), which are required for high-temperature, high-power, and high-speed applications [2]. Important utilizations include micro- and millimeter-wave power amplification and power switching [3], where maintaining efficiency at high power is a challenge, which is thought to be limited by parasitic thermal effects [4]. Thus, issues like current collapse and self-heating must be addressed. For further optimization a reliable simulation tool is needed, such as the two-dimensional device simulator Minimos-NT [5,6].

#### 2. DEVICE STRUCTURE

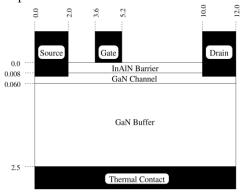

The HEMT device structure under investigation (Fig.1) is grown by metal-organic vapor phase epitaxy (MOVPE). A 300nm thick AlN layer is grown on a 6H-SiC substrate followed by a 2.5 $\mu$ m GaN buffer layer with a 1nm AlN spacer layer and a 7nm In<sub>0.12</sub>Al<sub>0.88</sub>N barrier layer on top. The thicknesses are nominal [7]. All layers are non-intentionally doped. The gate length is 1.6 $\mu$ m. The gate-to-source and the gate-to-drain distances are 1.6 $\mu$ m and 4.8 $\mu$ m, respectively. The device width is 400 $\mu$ m and there is no passivation. More details about the device fabrication process are reported in [7].

<sup>&</sup>lt;sup>1</sup> Inst. of Electronics and Photonics, Slovak University of Technology, Ilkovičova 3, 812 19 Bratislava, Slovakia

<sup>&</sup>lt;sup>2</sup> Institute for Microelectronics, TU Wien, Guβhausstraβe 27-29, 1040 Vienna, Austria <sup>3</sup> Institute of Electrical Engineering, Slovak Academy of Sciences, Dúbravská cesta 9, 841 04 Bratislava, Slovakia

## 3. NUMERICAL AND PHYSICS-BASED MODELING

Two-dimensional numerical simulations are performed employing Minimos-NT. Selfheating effects are accounted for by the lattice heat flow equation. The AlN/InAlN barrier system is represented by a 8 nm thick InAlN in the model [8]. This simplification is acceptable because the sum of polarization charges on both sides of AlN equals the polarization charge at InAlN/GaN interface. We can accept this simplification at elevated temperature, as well. Well-calibrated two-valley electron mobility and bandgap energy models are implemented in the simulator [9]. For In<sub>0.12</sub>Al<sub>0.88</sub>N a bandgap energy  $E_g$ =4.84 eV at room temperature is obtained [10]. Due to the divergence of the polarization fields at the InAlN/GaN heterointerface, a two-dimensional electron gas (2DEG) is formed in the quantum well with a density  $n_{\rm 2DEG}$ =2.6×10<sup>13</sup> cm<sup>-2</sup>. This value, which also depends on the Indium content in the InAlN layer, gives the best agreement to measured data [10]. The interface between the GaN buffer layer and the AlN nucleation layer is described by a value of the polarization charge  $\sigma = -2.5 \times 10^{11}$  cm<sup>-2</sup>. Performing hydrodynamic simulations with self-heating, we introduce a substrate thermal contact (Fig.1). We obtain the best agreement with experimental data by using a thermal contact resistance  $R_{\rm th}=10^{-3}{\rm Kcm^2/W}$ . This value lumps the thermal resistance of the nucleation layer and the SiC substrate, and possible three-dimensional thermal effects [11]. The  $R_{\rm th}$ value nicely coincides with that obtained from optical measurements [12]. A new impact ionization model, based on Monte Carlo simulation results [13], was developed and implemented in Minimos-NT.

0.6 Oexp. A 🔷 exp. B 0.5 -∆ sim.  $V_{GS}=1V$ 0.4 0.3  $V_{GS}=0V$ 0.2 0.1 0.0 L 300 350 400 450 Temperature [K]

Fig. 1 Schematic view of the investigated InAlN HEMT structure. The dimensions are given in microns.

Fig. 2 Measured and simulated drain current vs. temperature for  $V_{\rm DS}{=}10{\rm V}$  and a  $V_{\rm GS}$  sweep from  $-2{\rm V}$  to  $1{\rm V}$ .

### 4. RESULTS AND DISCUSSION

DC *I-V* characteristics were measured employing the fully automated Agilent 4155C semiconductor parameter analyzer with wolfram contact probes. The equipment consists of four source/monitor units (SMUs), two voltage monitor units (VMUs), and two voltage source units (VSUs). These standard measurement resources satisfy the vast majority of

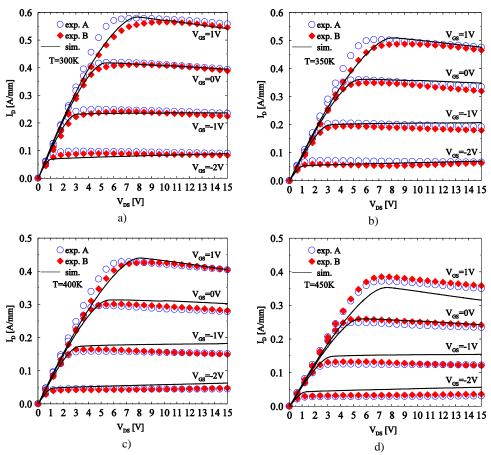

Fig. 3 Measured and simulated output characteristics at a) 300 K, b) 350 K, c) 400 K and d) 450 K for a  $V_{\rm GS}$  sweep from  $-2{\rm V}$  to  $1{\rm V}$ .

parametric characterization needs. The highly accurate laboratory bench top parameter analyzer for advanced device characterization was used in conjunction with a thermal chuck where the temperatures are set with an accuracy of 0.1 K. Two device samples were chosen to represent the whole collection of measurements. All samples were measured in the relevant temperature range between 300 K and 450 K. The devices exhibit a threshold voltage of about -2.5V. Fig. 2 shows the drop of the drain current with increasing temperature at  $V_{\rm DS}$ =10V for different gate biases. Fig. 3 presents comparisons of measured and simulated output device characteristics for a  $V_{\rm GS}$  sweep from -2V to 1V at 300 K, 350 K, 400 K, and 450 K, respectively. A very good agreement between measurements and simulation results is achieved using the hydrodynamic transport model including self-heating and impact ionization effects up to 400 K, while for 450 K the experimental results exceed those calculated by the model, particularly at  $V_{\rm GS}$ =1V. This phenomenon could be caused by a different scattering mechanism at high 2DEG density, i.e. efficient screening arising from the 2DEG [14]. For low drain biases the decrease of the drain

current with temperature is mostly caused by the reduction of the low-field electron mobility which follows a power law with power -1.5. For  $V_{\rm GS}$ =1 V and  $V_{\rm DS}$ =10 V the peak temperature in the device varies between 380 K (300 K at the substrate) to 500 K (450 K).

# 5. CONCLUSION

Results from electrical high-temperature measurements and two-dimensional numerical simulations of  $In_{0.12}Al_{0.88}N/GaN$  HEMTs are presented. Very good agreement between experiment and simulation at 300 K and at elevated temperatures was obtained using the hydrodynamic transport model with self-heating and a carefully tuned impact ionization model.

### Acknowledgement

This work was supported by the Austrian Science Funds START Project Y247-N13, by the ENIAC JU project no. 324280/2012 E2COGaN, and by the Slovak R&D Agency grant APVV-0367-11.

#### References

- [1] M. Levinshtein, S. Rumyantsev, and M. Shur, *Properties of Advanced Semiconductor Materials*, Wiley, New York (2001).

- [2] R. Quay, *Gallium Nitride Electronics*, Springer, Berlin Heidelberg (2008).

- [3] W. Saito, Y. Takada, M. Kuraguchi, K. Tsuda, I. Omura, T. Ogura, and H. Ohashi, *IEEE Trans. Elec. Dev.* 50, 2528-2531 (2003).

- [4] A. Matulionis, In: *Proc. Device Research Conference* 146-149 (2004).

- [5] V. Palankovski, R. Quay, *Analysis and Simulation of Heterostructure Devices*, Springer, Wien New York (2004).

- [6] S. Vitanov, Simulation of High Electron Mobility Transistors, Dissertation, TU Wien (2010).

- [7] H. Behmenburg, C. Giesen, R. Srnanek, J. Kovac, H. Kalisch, M. Heuken, and R.H. Jansen, *J. Crystal Growth* 316, 42-45 (2011).

- [8] M. Gonschorek, J.-F. Carlin, E. Feltin, M. A. Py, N. Grandjean, V. Darakchieva, B. Monemar, M. Lorenz, and G. Ramm, J. Appl. Phys. 103, 093714 (2008).

- [9] S. Vitanov, V. Palankovski, S. Maroldt, R. Quay, S. Muray, T. Roedle, and S. Selberherr, *IEEE Trans. Elec. Dev.* 59, 685-693 (2012).

- [10] M. Molnár, G. Donnarumma, V. Palankovski, J. Kuzmík, D. Donoval, J. Kováč, and S. Selberherr, In *Proc. APCOM'12* 190-194 (2012).

- [11] S. Vitanov, V. Palankovski, G. Pozzovivo, J. Kuzmík, and R. Quay, In *Proc. HETECH'08*, 159-160 (2008).

- [12] J. Kuzmik, S. Bychikhin, D. Pogany, C. Gaquière, E. Pichonat, and E. Morvan, *J. Appl. Phys.* 101, 054508 (2007).

- [13] R. Redmer, J. R. Madureira, N. Fitzer, S. M. Goodnick, W. Schattke, and E. Scholl, J. Appl. Phys. 87, 781 (2000).

- [14] R. Tülek, A. Ilgaz, S. Gökden, A. Teke, M. K. Öztürk, M. Kasap, S. Özçelik, E. Arslan, and E. Özbay, *J. Appl. Phys.* 105, 013707 (2009).