#### TWO DIMENSIONAL MOS-TRANSISTOR MODELING

S. SELBERHERR, A. SCHÜTZ and H. PÖTZL

Institut für Allgemeine Elektrotechnik und Elektronik

Abteilung für Physikalische Elektronik

Technische Universität Wien

Gußhausstraße 27

A-1040 Wien, AUSTRIA

and

Ludwig Boltzmann Institut für Festkörperphysik

ABSTRACT - The advent of Very Large Scale Integration has been an incentive to concentrate persistently on device modeling. fundamental properties which represent the basis for all device modeling activities are summarized. The sensible use of physical and technological parameters is discussed and the most important physical phenomena which are required to be taken into scrutinized. The assumptions necessary for finding a reasonable trade-off between efficiency and effort for a model synthesis are recollected. Methods to bypass limitations induced these assumptions are pin-pointed. Simple and easy to use formulae for the physical parameters of major importance presented. The necessity of a careful parameter-selection, based physical information, is shown. Some glimpses on numerical solution of the semiconductor equations are given. discretisation of the partial differential equations with finite differences is outlined. Linearisation methods and algorithms for the solution of large sparse linear systems are sketched. Results of our two dimensional MOSFET model - MINIMOS - are discussed with typical applications. Much emphasis is laid didactic potential of such a complex high order model. addition to its academic importance, the role of modeling as tool to optimize transistor performance is stressed.

#### 1. INTRODUCTION

The first integrated circuits which just contained a few devices became commercially available in the early 1960's. Since that time an evolution has taken place so that today the manufacture of integrated circuits with over 400.000 transistors per single chip is possible. This advent of the so-called Very-Large-Scale-Integration (VLSI) certainly revealed the need of a understanding of the basic device physics. miniaturization of the single transistor, which is one of the inseparable preconditions of VLSI, brought about a collapse of the classical device models, because totally new phenomena emerged and even dominated the device behaviour. One consequence of this evidence led to an unimaginable number of suggestions of how to modify the classical models to incorporate various of the Additionally new activities have been initiated new phenomena. to explore the physical principles which make a operationable. The number of scientific publications which utilize the terms "device analysis", "device simulation" and "device modeling" (c.f./4/, /53/, /83/) grew in an incredible manner.

At first it seems necessary to clarify these frequently used terms to facilitate the intelligibility of the subsequent chapters. Consulting a dictionary one will find among many more the following interpretations:

#### Analysis

- separation of a whole into its component parts, possibly with comment and judgement

- examination of a complex, its elements, and their relations in order to learn about

#### Simulation

- imitative representation of the functioning of one system or process by means of the functioning of another

- examination of a problem not subject to experimentation

## Modeling

- to produce a representation or simulation of a problem or process

- to make a description or analogy used to help visualize something that cannot be directly observed

Therefore, analysis is at least intended to mean "Exact Analysis" and simulation must inferentially mean "Approximate Simulation" using only to some extent physically motivated models. Modeling is necessary for analysis and simulation, but with a different objective. However, any model should at least reflect the underlying physics.

The characteristic feature of early modeling was the separation of the interiour of the device into different regions, the treatment of which could be simplified by various assumptions like special doping profiles, complete depletion and quasineutrality. These separately treated regions were simply connected to produce the overall solution. If analytic results are intended, any other approach is prohibitive. Fully numerical modeling based on partial differential equations /172/ which describe all different regions of semiconductor devices in one unified manner was first suggested by Gummel /69/ for the one dimensional bipolar transistor. This approach was further developed and applied to pn-junction theory by De Mari /39/, /40/ and to IMPATT diodes by Scharfetter and Gummel /132/.

A two dimensional numerical analysis of a semiconductor device was carried out the first time by Kennedy and O'Brien /85/ who investigated the junction field effect transistor. Since then two dimensional modeling has been applied to fairly all important semiconductor devices. There are so many papers of excellent repute that it would be unfair to cite only a few. Recently also the first results on three dimensional device modeling have been published. The time dependence has been investigated by e.g. /96/, /107/ and models for three space dimensions have been announced by e.g. /25/, /185/, /186/.

In spite of all these important and successful activities, the need for economic and highly user oriented computer programs became more and more apparent in the field of device modeling. Especially for MOS devices which have evolved since their invention by Kahng and Atalla /82/ to an incredible standard, modeling has become inherently important because current flow controlled by a perpendicular field is an intrinsically two dimensional problem. One such program which has been applied successfully in many laboratories is called CADDET /165/. We have also tried to bridge that gap and developed MINIMOS /140/ for the two dimensional static analysis of planar MOS transistors.

In the next chapter the fundamental properties which are the basis for all device models are summarized. Much effort is laid on the documentation of various physical effects which possibly have to be taken into account when synthezising a device model for some special application. The assumptions which are usually made to ease modeling are presented and their validity is, at least qualitatively, discussed. Simple and easy to use formulae are presented which allow phenomenological simulation of the most important physical parameters with which the modelist has to deal.

In the third chapter the numerical solution of the basic semiconductor equations is discussed. The two main methods for the solution of differential equations (i.e. finite differences and finite elements) are briefly compared. The discretisation of the general quasiharmonic equation is explained, because Poisson's equation as well as the continuity equations can be classified as quasiharmonic equations. A few linearisation schemes are presented and judged for adaequacy in terms of effort and efficiency. Classical algorithms for the solution of the sparse algebraic systems which are obtained by linearisation of the discrete semiconductor equations are explained.

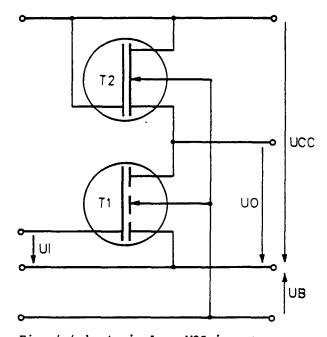

fourth chapter entirely deals with applications of MINIMOS. A didactic example which should make transparent the applicability of a high order model like MINIMOS for the analysis of device behaviour is given first. This example has been chosen to demonstrate the influence of ion implantation in the channel region of a very small scale MOSFET on threshold voltage punch through. Secondly, an example of a process sensitivity analysis is presented which is an application ideally suited for numerical investigations. A more sophisticated application is shown next to demonstrate that it is possible to comprehend some complex interaction of different physical phenomena with device modeling. This is accomplished by explaining the reasons for the snap-back effect in the characteristics of a miniaturized MOSFET. The final sections deal with the analysis of coupled devices. For that purpose an n-Mos Inverter with a depletion transistor and a CMOS inverter are investigated. examples are intended to stress the power and versatility of its informative potential device modeling and for the semiconductor industry.

This paper cannot intend to be any more than a summary with only moderate impact on details. The influence of process modeling, for instance, on the accuracy of the final result, important as it is, could not be dealt with. The reader with specific interest in any single subject will find the references useful for further information.

Throughout this paper all constants and quantities are given in the following units, if not specified otherwise: lengths in cm, times in s, temperature in K, voltages in V, currents in A. The units are often omitted to gain transparency in the formulae.

#### 2. SOME FUNDAMENTAL PROPERTIES

To accurately analyze an arbitrary semiconductor structure which is intended as a self-contained device under various operating conditions, a mathematical model has to be given. The equations which form this mathematical model are often called the fundamental semiconductor equations; these will be discussed in the first section of this chapter.

The second section will deal with assumptions which have to be made for special applications additionally to those which have already been used in the derivation of the equations and which are beyond the scope of this presentation. Furthermore, all quantities which are involved in the basic equations will be outlined more or less qualitatively.

It will become apparent that the fundamental equations employ a set of physical and technological parameters. An in-depth analysis of all these parameters is far from being finished at the moment - or the results of such an analysis are of overwhelming complexity - because of inherent methodical difficulties.

The third section will deal with additional assumptions which can be made to ease and speed up models for MOS-devices.

The topic of the fourth section of this chapter is the description of some suggestions for a heuristic simulation of the most important parameters based, as it were, on physical principles.

### 2.1 The Fundamental Semiconductor Equations

The most familiar model of carrier transport in a semiconductor device has been proposed by Van Roosbroeck /172/. It consists of Poisson's equation (2.1-1), the current continuity equations for electrons (2.1-2) and holes (2.1-3) and the current relations for electrons (2.1-4) and holes (2.1-5)

div

$$\xi$$

grad  $\Psi = -q (p - n + C)$  (2.1-1)

$$\operatorname{div} \overrightarrow{J}_{n} = -q \left( G - R \right) \tag{2.1-2}$$

$$div \vec{J}_{p} = q (G - R)$$

(2.1-3)

$$\vec{J}_n = -q \quad ( \mathbf{p}_n \quad \text{n grad } \mathbf{\Psi} - \mathbf{D}_n \quad \text{grad } \mathbf{n} )$$

(2.1-4)

$$\vec{J}_{D} = -q ( p_{D} p \text{ grad } \Psi + D_{D} \text{ grad } p )$$

(2.1-5)

These relations form a system of coupled partial differential equations. Poisson's equation, which is one of Maxwell's laws, describes the charge distribution in the interior of a semiconductor device. The balance of sinks and sources for electron— and hole currents is characterized by the continuity equations. The current relations describe the absolute value, direction and orientation of electron— and hole currents. The continuity equations and the current relations can be derived from Boltzmann's equation by not at all trivial means. The ideas behind these considerations cannot be presented here due to limited space. The interested reader should refer to /172/ and its secondary literature or text books on semiconductor physics e.g. /18/, /78/, /136/, /148/.

However, it is of prime importance to note that the equations (2.1-4) and (2.1-5) do not characterize effects which are caused by degenerate semiconductors (e.g. heavy doping). /97/, /171/, /174/ discuss some modifications of the current relations, which partially take into account the consequences introduced by degenerate semiconductors (e.g. invalidity of Boltzmann's statistics, bandgap narrowing). These modifications are not at all simple and lead to problems especially for the formulation of boundary conditions /116/, /173/. In case of modeling MOS devices, degeneracy is, owing to the relatively low doping in the channel region, practically irrelevant. For modern bipolar devices, though, bearing in mind shallow and extraordinarily heavily doped emitters, it is an absolute necessity to account for local degeneracy of the semiconductor.

Furthermore, (2.1-4) and (2.1-5) do not describe velocity overshoot phenomena which become apparent at feature lengths of 0.12m for silicon and 12m for gallium-arsenide /60/; and certainly no effects which are due to ballistic transport, the existence of which is still questionable /77/, are included. The latter start to become important for feature sizes below 0.012m for silicon and 0.12m for gallium-arsenide /61/. Considering the state of the art of device miniaturization, neither effect has to bother the modelists of silicon devices. For gallium-arsenide devices new ideas are mandatory for the near future /60/, /110/, /111/.

### 2.2 Assumptions and Discussion of Parameters

It is imperative to discuss the parameters of the semiconductor equations to get some insight into the complexity of that mathematical model and the difficulty of a more or less rigorous solution.

The permittivity  $\boldsymbol{\xi}$  in Poisson's equation in the most general

case is a rank two tensor. Because all common semiconductor materials grow in cubic crystal structure and because silicondioxide is amorphous no anisotropy exists and the permittivity can be treated as a scalar quantity. Furthermore, one can savely assume that the permittivity is homogenous with sufficient accuracy for even degenerate semiconductors.

The electrically active net doping concentration C Poisson's equation is the most important technological parameter. To obtain this quantity by mathematical analysis /51/ is at least as cumbersome as to accurately analyze some semiconductor device, because the physics of the technological processes which determine the doping concentration still lacks The need of modeling in this area is drastically understanding. increasing in view of VLSI devices. One-dimensional process modeling is fairly well established nowadays, but two-dimensional simulation is just appearing /51/, /164/. Some glimpses of modeling doping profiles with handy analytical expressions will be given in section 2.4.1. One assumption which is usually made with fairly satisfactory success is the total ionization of all dopants (2.2-1).

$$C = N_D - N_A = N_D^+ - N_A^-$$

(2.2-1)

As long as the Fermi level is separated several thermal voltages from the impurity level, this assumption holds quite nicely. For modern bipolar transistors, however, it certainly becomes questionable for the emitter region (degenerate material).

The electron density n and the hole density p are commonly assumed to obey Boltzmann's statistics (2.2-2).

$$n = n_i \cdot e^{(\mathbf{\psi} - \mathbf{\psi}_n)/U_T}$$

$p = n_i \cdot e^{(\mathbf{\psi}_p - \mathbf{\psi})/U_T}$  (2.2-2)

This assumption principally neglects degeneracy; but moderate degeneracy can be included /55/ by introducing an effective, doping dependent intrinsic number (2.2-3).

$$n_{i} = n_{i}(T,N)$$

$$n_{i}(T,N) = n_{i}(T) e^{52.7(1n(N/10^{17}) + \sqrt{(1n(N/10^{17}))^{2} + 0.5})/T}$$

$$n_{i}(T) = 3.88 \cdot 10^{16} \cdot T^{1.5} \cdot e^{-7000/T}$$

$$N = N_{D} + N_{A}$$

(2.2-3)

The temperature dependence of the intrinsic number is based on the influence of the effective carrier masses and the bandgap. More elaborate formulae for these effects which might be imperative for low temperature applications can be found in /62/. The formula for bandgap narrowing in (2.2-3) was first suggested by Slotboom /146/. For a doping concentration of  $1.3 \cdot 10^{17}$  cm<sup>-3</sup> the intrinsic number has already increased by twenty percent.

The mobility of electrons **p**n and holes **p**p is in principle a rank two tensor function of many arguments. One ends up with a so called "mobility" after averaging and combining various physical mechanisms which are still not analyzed thouroghly enough to be modeled satisfactorily /79/. Some formulae for a mobility model for silicon will be summarized in section 2.4.2.

Another assumption which is unfortunately not at all free of doubts is the validity of the Einstein-Nernst relations (2.2-4).

$$D_{n} = \mathbf{y}_{n} \cdot U_{T} \qquad D_{p} = \mathbf{y}_{p} \cdot U_{T} \qquad (2.2-4)$$

Some guidelines on how to extend these relations for degenerate material are given in e.g. /8/. It is important to remember that the current relations (2.1-4) and (2.1-5) do not differentiate between lattice temperature and electron temperature. Therefore, if one has to deal with hot electrons in a precise manner, the current relations have to be updated; in particular the mathematical structure of the diffusion current term has to be refined.

The last parameter which remains to be dealt with for a qualitative characterization is the net generation/recombination rate (G-R) in (2.1-2) and (2.1-3). This quantity has to describe a number of physical processes which are responsible for generation/recombination of electron-hole pairs. These processes and their interactions are also not analyzed to a satisfactory level so that one has to use heuristic expressions for a model which is at least plausible in the underlying physics. Some suggestions for these formulae will be given in section 2.4.3.

### 2.3 Additional Assumptions for MOS-Models

The fundamental semiconductor equations describe the internal behavior of any semiconductor device. However, for certain devices these equations may be simplified without significant loss of accuracy. As the MOSFET is a minority carrier device, the current is given mainly by the continuity equation of one carrier type. If avalanche is neglected, only little carrier generation occurs in the MOSFET.

Therefore, the eqs. (2.1-2)-(2.1-3) may be rewritten as

$$\text{div } \vec{J}_{n} = 0$$

(2.3-1)

$$\vec{J}_{p} = 0 \tag{2.3-2}$$

for the n-channel device and

$$\text{div } \vec{J}_{p} = 0$$

(2.3-3)

$$\vec{J}_{n} = 0 \tag{2.3-4}$$

for the p-channel device. However, it should be kept in mind that these assumptions are valid only if the avalanche effect is neglected.

The channel width of a MOSFET is usually much larger than the depletion widths. As a consequence the partial derivatives in that direction can be neglected and the semiconductor equations reduce to two dimensions. The neglection of the derivative of the potential in source-drain direction is a proper assumption only for long-channel devices. The so called "gradual-channel approximation" was the basis of a lot of one-dimensional models. These models fail to predict accurately the behavior of modern miniaturized devices.

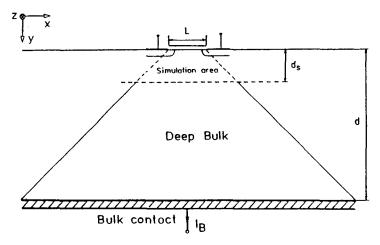

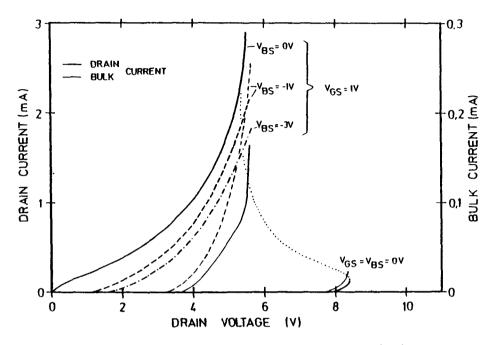

If the avalanche effect should be included, the assumptions (2.3-1)-(2.3-4) are no longer valid and both continuity equations have to be solved with inhomogeneity terms. As a consequence, the ionization-generated majority carriers (holes n-channel MOSFET) flow to the substrate as they are repelled from the source and drain junctions. There are several options to account for the voltage drop which is induced by the substrate current: (a) a truly three-dimensional analysis; (b) extension of simulation over the entire bulk area; (c) extension of the two-dimensional simulation over the depletion region and using an (effective) bulk resistor (Fig. 2.3-1). If one wants to avoid excessive computing time associated with (a), option (c) is to be preferred because it allows inclusion of current spread into the third dimension and, also, consumes less computing time than (b). In that way the voltage drop across the parasitic bulk resistor simulates a more positive bulk bias and, if large enough, is able to forward-bias the parasitic bipolar npn transistor (according to source, bulk, and drain). This causes a larger drain current and facilitates the breakdown which then will occur at smaller drain voltages /133/.

Fig. 2.3-1: Current flow in deep bulk

In the following we should like to suggest an easy method to estimate the value of the bulk resistor. It is assumed that the current spreads at an angle of 45 degrees /15/ into both directions perpendicular to its flow (x- and z- direction in Fig. 2.3-1). This assumption is arbitrary but not implausible, and, furthermore, if we neglect any diffusion current, we obtain the following expression for the electric field in the deep substrate.

$$\frac{d\mathbf{\Psi}}{d\mathbf{y}} = \frac{\mathbf{I}_{\mathbf{B}}}{\mathbf{K}_{\mathbf{A}}} = \frac{\mathbf{I}_{\mathbf{B}}}{\mathbf{K}(\mathbf{L}+2\mathbf{y})(\mathbf{W}+2\mathbf{y})}$$

(2.3-5)

with K standing for the conductivity of the substrate and A the area of the current flow. L and W are channel length and channel width, respectively. Integrating this equation along y from the end of the simulation area d to the bulk contact we obtain

$$R_{\text{Bulk}} = \frac{\int_{\text{B}}^{\text{d}} \frac{d\mathbf{W}}{dy} dy}{I_{\text{B}}} = \frac{1}{2\mathbf{K}(\text{W-L})} \left( \ln\left(\frac{L+2d}{L+2d}\right) - \ln\left(\frac{W+2d}{W+2d}\right) \right) . \quad (2.3-6)$$

L=W this equation simplifies to

For L=W this equation simplifies to

$$R_{\text{Bulk}} = \frac{d-d_s}{K(L+2d)(L+2d_s)}$$

(2.3-7)

This calculation is fairly crude compared to the elaborate solution of the basic equations. However, any more precise calculation would be very complicated and the present method is sufficient to investigate the influence of the parasitic bulk resistance at least qualitatively.

### 2.4 Models of Physical Parameters

#### 2.4.1 Formulae for Modeling Doping Profiles

A one dimensional doping profile which can be calculated fairly accurately with a process simulation program (e.g. /6/) may be heuristically converted to two dimensions for a structure with an ideal oxide mask as shown in Fig. 2.4-1 using (2.4-1).

Fig. 2.4-1 Coordinate nomenclature for an ideal oxide mask

$$C(x,y) = C(y^2 + \max(x/f,0)^2)$$

(2.4-1)

This formula is extraordinarily simple to use and needs only one fitting parameter: f which controls the amount of lateral diffusion. For most applications f lies in the range of 0.5 to 0.9. An elliptic rotation at x=0 (c.f. Fig. 2.4-1) of the one-dimensional profile is performed to obtain the doping concentration below the oxide mask. Out-diffusion effects which occur near the mask edge are not at all taken into account.

Lee /89/, /90/ recently published expressions which are still fairly simple to use, but which are based on more physical reasoning. (2.4-2) can be used for the simulation of a predeposition step. Ld denotes the diffusion length; D: diffusion constant, t: diffusion time,  $N_s$ : desired surface concentration.

$$Ld = 2 \cdot \sqrt{D \cdot t}$$

$$C_{p}(x,y) = 0.5 \cdot N_{s} \cdot e^{-(y/Ld)^{2}} \cdot erfc(x/Ld)$$

(2.4-2)

The distribution of implanted ions under mask edges has also been investigated extensively e.g. /128/. The formulae (2.4-3) which have been taken from /89/, /90/ allow simulation of diffusion with an initial ion-implantation. Rp denotes the projected range, ARp: projected standard deviation, Dose: implantation dose.

$$a = (2 + (Ld/\Delta R_p)^2)^{-1/2}$$

$$K(y) = e^{-(a \cdot (R_p - y)/\Delta R_p)^2} \cdot erfc(-a \cdot ((R_p/\Delta R_p) + \sqrt{2} \cdot y/Ld))$$

$$C_i(x,y) = (a/(4 \cdot \Delta R_p \cdot \sqrt{\pi})) \cdot Dose \cdot (K(y) + K(-y)) \cdot erfc(x/Ld)$$

In the derivation of (2.4-2) and (2.4-3) it is assumed that the diffusion "constant" is really constant. This limits the application to relatively low peak values of the implanted profile. For high peak values one might fit the diffusion lengths Ld to obtain a desired junction depth.

The diffusion constant D can be estimated, again for fairly low concentrations, with the classical exponential law (2.4-4).

$$D = D_0 \cdot e^{T_a/T}$$

Element  $D_0/(cm^2s^{-1})$   $T_a/(K)$

$$B = 0.5554 -3.975 \cdot 10^4$$

$$P = 3.85 -4.247 \cdot 10^4$$

$$Sb = 12.9 -4.619 \cdot 10^4$$

$$As = 24. -4.735 \cdot 10^4$$

The projected range parameters Rp and App which are nonlinear functions of the implantation energy can be looked up in standard tables /64/. These tables are principally tedious to implement in computer programs, so that one might prefer some polynomial fit (2.4-5); x denotes here the implantation energy.

$$R_{p} = \sum_{i=1}^{n} \cdot x^{i} \qquad (\mathbf{p}_{m})$$

$$i=1$$

$$n$$

$$\Delta R_{p} = \sum_{i=1}^{n} \cdot x^{i} \qquad (\mathbf{p}_{m})$$

$$i=1$$

$$(2.4-5)$$

The coefficients for such polynomials are given in Fig. 2.4-2 for Rp in silicon, in Fig. 2.4-3 for Ap in silicon and in Fig. 2.4-4 for Rp in silicon-dioxide.

| Element               | В                      | P          | Sb                     | As                      |

|-----------------------|------------------------|------------|------------------------|-------------------------|

| <b>a</b> <sub>1</sub> |                        |            | 8.887.10-4             |                         |

| a 2                   | $-3.308 \cdot 10^{-6}$ |            | $-1.013 \cdot 10^{-5}$ |                         |

| <sup>a</sup> 3        |                        | 1.290.10-9 | 8.372.10 <sup>-8</sup> | -                       |

| a <sub>4</sub>        |                        |            |                        | $-3.442 \cdot 10^{-10}$ |

| <b>a</b> <sub>5</sub> |                        |            | 4.028.10               | $4.608 \cdot 10^{-13}$  |

Fig. 2.4-2 Coefficients for Rp in silicon

| Element        | В                       | P | Sb                     | As                     |

|----------------|-------------------------|---|------------------------|------------------------|

|                |                         |   | 2.674.10-4             |                        |

| ь <sub>2</sub> | $-2.086 \cdot 10^{-5}$  |   |                        |                        |

| b <sub>3</sub> |                         |   | 2.311.10 <sup>-8</sup> |                        |

|                | $-4.545 \cdot 10^{-10}$ |   |                        |                        |

| b <sub>5</sub> | $5.525 \cdot 10^{-13}$  |   | $1.084 \cdot 10^{-13}$ | $1.601 \cdot 10^{-13}$ |

Fig. 2.4-3 Coefficients for  $\triangle$ Rp in silicon:

| Element        | В                      | P                      | Sb                     | As                      |

|----------------|------------------------|------------------------|------------------------|-------------------------|

| *1             |                        |                        | 7.200.10-4             |                         |

| <b>a</b> 2     | $-2.113 \cdot 10^{-6}$ | $-2.240 \cdot 10^{-7}$ | $-8.054 \cdot 10^{-6}$ |                         |

| a <sub>3</sub> |                        |                        |                        | 7.029·10 <sup>-8</sup>  |

| a <sub>4</sub> |                        |                        |                        | $-2.653 \cdot 10^{-10}$ |

| a <sub>5</sub> |                        |                        | $3.191 \cdot 10^{-13}$ | $3.573 \cdot 10^{-13}$  |

Fig. 2.4-4 Coefficients for Rp in silicon-dioxide

The maximum error of the projected range parameters culated with these coefficients and (2.2-5) is in the energy ge of 5keV to 300keV only a few percent compared to /64/. e data are given in /141/.

If an implantation is performed through an oxide, the projected range in the semiconductor has to be reduced /129/ e.g. with (2.4-6).

$$Rp = Rp_{se} \cdot (1 - T_{iox}/Rp_{ox})$$

(2.4-6)

$T_{iox}$  denotes the thickness of the oxide,  $Rp_{se}/Rp_{ox}$ : projected range in semiconductor/oxide.

# 2.4.2 Formulae for Mobility Modeling

The mobility of carriers is, as already mentioned, an eminently complex quantity. Additionally it is an important parameter, because all errors in the mobility lead to a proportional error of the current through the multiplicative dependence. This is certainly one of the primary results any model should yield reliably. The formulae which will be given below describe phenomenologically the mobility in silicon; the subscripts n and p denote electrons and holes, respectively.

To model mobility at least plausibly, several scattering mechanisms have to be taken into account, the basis of which is lattice scattering. This effect can be described by a simple power law /79/, /136/ in dependence of temperature (2.4-7).

$$\mathbf{P}_{L}(T) = A \cdot T^{-g} \qquad (cm^{2}/v_{s})$$

$$A_{n} = 7.12 \cdot 10^{8}$$

$$g_{n}^{n} = 2.3$$

$$A_{p} = 1.35 \cdot 10^{8}$$

$$g_{p}^{p} = 2.2$$

(2.4-7)

The pure lattice mobility is reduced through the scattering processes at ionized impurities. (2.4-8) is a well established formula which models temperature dependent ionized impurity scattering /24/ and electron-hole scattering /55/. The latter is extremely important in low doped regions where high injection takes place.

$$\mathbf{P}_{LI}(N,T) = \mathbf{P}_{L}(T) \cdot a + \mathbf{P}_{min} \cdot (1 - a) \quad (cm^{2}/Vs)$$

$$a = \frac{1}{1 + (T/300)^{b} \cdot (N/N_{0})^{c}}$$

$$N = 0.67 \cdot (N_{D}^{+} + N_{A}^{-}) + 0.33 \cdot (n + p)$$

$$\mathbf{P}_{minn} = 55.24 \qquad \mathbf{P}_{minp} = 49.7$$

$$b_{n} = -3.8 \qquad b_{p} = -3.7$$

$$c_{n} = 0.73 \qquad c_{p} = 0.7$$

$$N_{0n} = 1.072 \cdot 10^{17} \qquad N_{0p} = 1.606 \cdot 10^{17}$$

Similar expressions which have been partly deduced from measurement and/or theory have been presented in /7/, /41/, /47/, /92/, /132/.

To properly simulate the mobility in MOS transistors, one has to deal with surface roughness and field dependent surface scattering. /30/, /130/, /153/ presented interesting measured results on inversion layer mobility; /162/, /163/ gave some excellent ideas on how to treat theoretically these and other scattering mechanisms; /182/ suggested a heuristic formula for field dependent surface scattering which is applicable for two-dimensional simulations, but whose adequacy is questioned in /162/. However, we have developed (2.4-9) which models phenomenologically with best fit to measurement surface roughness as well as field dependent surface scattering /143/.

$$\mathbf{p}_{LIS}(y, E_{p}, E_{t}, N, T) = \mathbf{p}_{LI}(N, T) \cdot \frac{y+y_{r}}{y+b \cdot y_{r}} \quad (cm^{2}/Vs)$$

$$y_{r} = y_{0}/(1+E_{p}/E_{p0})$$

$$b = 2+E_{t}/E_{t0}$$

$$E_{p} = max(0, (E_{x} \cdot J_{x}+E_{y} \cdot J_{y})/(J_{x}^{2}+J_{y}^{2})^{1/2})$$

$$E_{t} = max(0, (E_{x} \cdot J_{y}-E_{y} \cdot J_{x}) \cdot J_{x}/(J_{x}^{2}+J_{y}^{2}))$$

$$y_{0n} = 5 \cdot 10^{-7}$$

$$y_{0p} = 4 \cdot 10^{-7}$$

$$E_{p0n} = 10^{4}$$

$$E_{p0n} = 1 \cdot 8 \cdot 10^{5}$$

$$E_{t0p} = 3 \cdot 8 \cdot 10^{5}$$

In regions with a high electric field component parallel to current flow, drift velocity saturation has to be taken into account. (2.4-10) combines, also phenomenologically, this physical effect and the lattice-impurity-surface mobility using a Mathiessen-type rule with a weakly temperature dependent saturation velocity /23/, /79/, /80/.

$$\mu_{\text{tot}}(y, E_{p}, E_{t}, N, T) = (\mu_{\text{LIS}}(...)^{8} + (v_{s}/E_{p})^{8})^{1/8}$$

$$v_{\text{sn}} = 1.53 \cdot 10^{9} \cdot T^{-0.87}$$

$$v_{\text{sp}} = 1.62 \cdot 10^{8} \cdot T^{-0.52}$$

$$\theta_{n} = -2$$

$$\theta_{p} = -1$$

(2.4-10)

## 2.4.3 Formulae for Modeling Generation/Recombination

To simulate satisfactorily transfer phenomena of majority carrier current and minority carrier current in just a simple diode, it is an absolute necessity to model carrier recombination and generation as carefully as possible. (2.4-11) represents the well known Shockley-Read-Hall term for modeling thermal generation/recombination. The carrier lifetimes can be simulated as being doping dependent /35/, /103/.

$$(G - R)_{th} = \frac{n_i^2 - p \cdot n}{\mathbf{t}_n(p+p_1) + \mathbf{t}_p(n+n_1)}$$

(1/cm<sup>3</sup>s) (2.4-11)

$$\mathbf{t}_{n} = 3.95 \cdot 10^{-5} / (1 + \text{N}/7.1 \cdot 10^{15}) \ \mathbf{t}_{p} = 3.52 \cdot 10^{-5} / (1 + \text{N}/7.1 \cdot 10^{15})$$

Surface generation/recombination /74/ can be treated in a fairly similar manner by (2.4-12).

$$(G - R)_s = \frac{n_i^2 - p \cdot n}{(p+p_1)/s_n + (n+n_1)/s_p} \cdot d(y)$$

(1/cm<sup>3</sup>s) (2.4-12)

d(y): Dirac-Delta function, y=0 denotes an interface

$$s_n = 100$$

$s_p = 100$

Impact ionization can be modeled by an exponentially field dependent generation term /27/, /28/. The constants in (2.4-13) are essentially taken from /170/.

$$G_{a} = \frac{|\vec{J}_{n}|}{q} \quad A_{n} \exp \left(-\frac{B_{n}|\vec{J}_{n}|}{\vec{E} \cdot \vec{J}_{n}}\right) + \frac{|\vec{J}_{p}|}{q} \quad A_{p} \exp \left(-\frac{B_{p}|\vec{J}_{p}|}{\vec{E} \cdot \vec{J}_{p}}\right) \quad (1/\text{cm}^{3}\text{s})$$

$$A_{n} = 7 \cdot 10^{5} \qquad A_{p} = 1.588 \cdot 10^{6}$$

$$B_{n} = 1.23 \cdot 10^{6} \qquad B_{p} = 2.036 \cdot 10^{6}$$

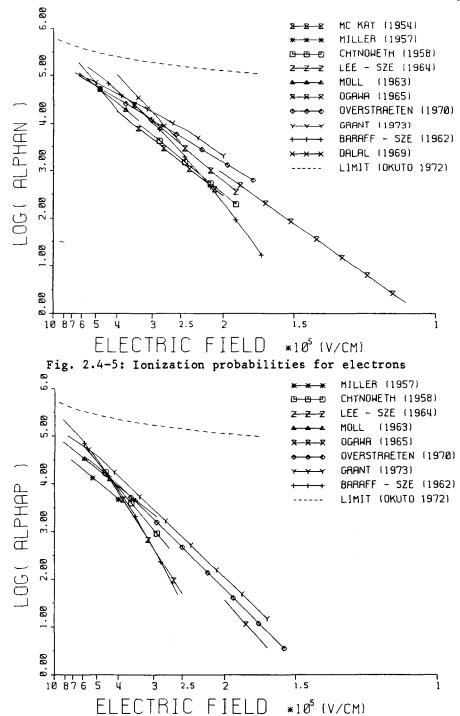

It should be noted that this form of simulating avalanche is relatively crude compared to more exact considerations, but the underlying physical principles are so complex that a trade-off in accuracy and complexity leads to that type of formula. ionization probabilities  $\mathbf{c}_{n,p}$  for silicon as a function of the electric field have been measured by various authors: Mc Kay /101/, /102/, Miller /105/, /106/, Chynoweth /27/, /28/, Lee /88/, Moll /112/, /113/, Ogawa /118/, Van Overstraeten /170/, Grant /65/, Dalal /36/. Their results are summarized in Fig. 2.4-5 for electrons and in Fig. 2.4-6 for holes. Additionally, the measured results are compared to theoretical results of Baraff /10/ (material constants from Sze /157/, /158/). Also drawn in Fig. 2.4-5 and Fig. 2.4-6 are theoretical limits published by Okuto /122/, /123/, which imply that all the energy the carriers can obtain from the electric field is used to generate additional carriers. Furthermore, the energy loss per single ionization has been taken to be 1.6eV for electrons and 1.8eV for holes (see also /75/). A more concise treatment of the ionization probabilities has been undertaken theoretically by /5/, /26/, /91/, /145/, /160/, /161/, /162/, /169/, /181/ and experimentally by /95/, /131/, /149/.

To analyze high injection conditions, Auger recombination has to be included as an antagonism to avalanche generation. Already the use of a simple formula like (2.4-14) in general gives satisfactory results /31/, /35/, /52/, /55/.

$$(G - R)_{Aug} = (n_i^2 - p \cdot n) (C_n \cdot n + C_p \cdot p)$$

(1/cm<sup>3</sup>s) (2.4-14)

$C_n = 2.8 \cdot 10^{-31}$   $C_p = 9.9 \cdot 10^{-32}$

Finally, all generation/recombination phenomena have to be combined to one total quantity. The usual way to do so is to simply sum up all terms (2.4-15). However, that means that no interaction of the different phenomena does exist.

$$(G-R)_{tot} = (G-R)_{th} + (G-R)_{s} + (G-R)_{Aug} + G_{a}$$

(2.4-15)

Fig. 2.4-6: Ionization probabilities for holes

### 3. NUMERICAL SOLUTION OF SEMICONDUCTOR EQUATIONS

The major difficulty in designing a high order numerical model of a semiconductor device is the adaption of adequate numerical methods for the solution of the basic semiconductor equations and their associated, often very complex, physical parameters, as outlined in the previous chapter.

In section 3.1 we should like to discuss the discretisation of the basic equations. The classical method of replacing derivatives with finite differences will be explained. The last part of that section will deal with automatic and adaptiv mesh generation which is a task of primary importance for user oriented models, but which has as yet not been scrutinized thoroughly.

The linearization of discrete equations will be treated in section 3.2 with some emphasis on the severely strong nonlinearity of the semiconductor equations. For that purpose some modified Newton schemes are presented which yield an incredible gain in computer efficiency.

Algorithms for the solution of the linearized discrete equations are discussed in section 3.3. A review of the most attractive methods for linear systems with special sparsity structure is given and also some cautious judgement is ventured.

### 3.1 Discretisation of Semiconductor Equations with Finite Differences

Unfortunately, the basic semiconductor equations cannot be solved in closed form by analytical methods. To utilize a numerical method, first of all the domain in which a solution is wanted has to be split into a finite number of small parts. These parts have to be sufficiently small so that all dependent variables of the basic equations behave like some arbitrarily chosen, but nevertheless simple functions; the equations have to be discretised. However, one should always bear in mind that one can, following the above sketched outline, obtain only an exact solution of the discretised problem, which is just an approximate analytically formulated equations. of the difference between the discrete solution and the solution of the real problem depends obviously on the partitioning of the domain and the selection of the approximating functions.

There exist basically two classical methods for obtaining algebraic equations, which approximate the differential equation and which can be solved numerically, namely: the Finite Difference method and the Finite Element method. The fundamental

difference between these two methods can be summarized, at qualitatively, as follows. By applying the finite difference method, all derivatives in the differential equation are replaced by finite differences between discrete points in the interior of the domain and the residual of the resulting difference equation The finite is set to zero on every discrete point. method in its residual formulation demands that the weighted residuum integrated over the whole domain be zero. This can be achieved algebraically by setting all residual integrals for every finite element for which the solution is assumed to obey some simple functional relation to zero. From our point of view it is impossible to favourize one method distinctly; both methods have their advantages and bottlenecks. Following the literature many renowned authors have concentrated their work on finite elements e.g. /1/, /13/, /20/, /21/, /22/, /25/, /32/, /70/, /71/, /119/, or finite differences e.g. /56/, /66/, /67/, /76/, /84/, /85/, /93/, /94/, /107/, /108/, /109/, /121/, /154/. We have also concentrated our activities on finite differences, because the mathematical background required to produce a running program seems to be somewhat smaller for the finite difference method than for the finite element method. Some interesting extensions of the finite difference method have been recently proposed by Adler /2/, /3/. When fully utilizing these ideas, one advantage of the finite element method, high flexibility at partitioning task, should also be reached with the finite difference method.

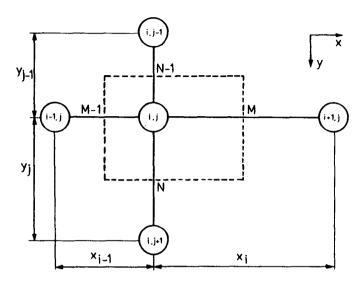

should like to explain the discretisation with five-point-star differences, which is probably the best known approach of the finite difference method for two dimensional partial differential equations (PDEs). The domain in which solution of a PDE is desired is first partitioned into small areas by grid lines parallel to some arbitrary coordinate system. For the sake of simplicity a rectangular domain and a cartesian coordinate system will be assumed. By laying NX vertical grid lines (parallel to y-axis) and NY horizontal grid lines (parallel to x-axis) one gets  $NX \cdot NY$  intersections. On these intersections one wants to obtain an approximate solution of the PDE of sufficient accuracy. For that purpose the PDE is replaced on every inner point (i,j) (see Fig. 3.1-1) by a difference equation which uses the inner point (i,j) and its four nearest neighbours (i+1,j), (i-1,j), (i,j+1) and (i,j-1). The major assumption for the derivation of the difference equation is that the solution can be approximated with a piecewise linear function along the verteces between the inner point (i,j) and its neighbours. Thus one gets  $(NX-2)\cdot(NY-2)$  difference equations because that is exactly the number of inner points. At the boundary of the domain the solution of the PDE has to fulfill some boundary conditions from which one can obtain equations for the boundary

points in a similar manner; there exist 2 · (NX+NY-2) boundary points. The total number of equations equals, therefore, the total number of points and a unique solution can be found.

Fig. 3.1-1: The index convention used

In the next section the discretisation of the quasiharmonic equation in a precise manner will be dealt with, because the linearized forms of Poisson's equation as well as continuity equations belong to this important category of PDEs and many publications have been written on that subject e.g. /58/, /59/, /98/, /147/.

## 3.1.1 The Quasiharmonic Equation

Let G be a finite domain in the (x,y) plane bounded by R which is piecewise continuously differentiable. Furthermore, let the functions P(x,y), S(x,y) and F(x,y) be piecewise continuous in G. P(x,y) be positive and not vanishing anywhere; S(x,y) be positive or zero. Then (3.1-1) represents the quasiharmonic equation with solution u(x,y).

$$div(P(x,y)\cdot grad(u(x,y))) - S(x,y)\cdot u(x,y) = F(x,y)$$

(3.1-1)

subject to the boundary conditions:

$$A(x,y) \cdot u(x,y) + B(x,y) \cdot u(x,y)_{n} = C(x,y)$$

(3.1-2)

where A(x,y), B(x,y) and C(x,y) are defined in R, piecewise continuous and positive or zero, and A(x,y)+B(x,y) is not vanishing anywhere.  $u(x,y)_n$  denotes the derivate of u(x,y) perpendicular to the boundary.

For a solution of this problem the differential equation has to be integrated in every area  $g_{ij}$ , obtained by partitioning as outlined above, around the inner point (i,j). The area  $g_{ij}$  is drawn with dashed lines in Fig. 3.1-1; it is represented by the rectangle around point (i,j).

$$\iint_{g_{ij}} div(P \cdot grad(u)) \cdot dx \cdot dy - \iint_{g_{ij}} S \cdot u \cdot dx \cdot dy = \iint_{g_{ij}} F \cdot dx \cdot dy$$

(3.1-3)

Using Green's theorem, the area integral can be transformed into a closed boundary integral around  $\mathbf{g}_{i\,j}$ .

$$\iint_{\mathbf{div}(\mathbf{P}\cdot\mathbf{grad}(\mathbf{u}))\cdot\mathbf{dx}\cdot\mathbf{dy}} = \int_{\mathbf{P}\cdot(\mathbf{\partial}_{\mathbf{u}}/\mathbf{\partial}_{\mathbf{x}})\cdot\mathbf{dy}-\mathbf{P}\cdot(\mathbf{\partial}_{\mathbf{u}}/\mathbf{\partial}_{\mathbf{y}})\cdot\mathbf{dx}}$$

$$\mathbf{r}_{ij} \qquad \qquad \mathbf{r}_{ij} \qquad \qquad (3.1-4)$$

Let  $x_i$  be the geometrical distance between the i.th and i+1.st vertical grid line and  $y_i$  the distance between the j.th and j+1.st horizontal grid line (cf. Fig. 3.1-1). Let  $P_M$  be the value of function P(x,y) at point M which is placed exactly between points (i,j) and (i+1,j); and assume the analogous relations for  $P_{M-1}$ ,  $P_N$  and  $P_{N-1}$ , which can be easily made clear with Fig. 3.1-1. Then the following holds:

$$\int_{(P^{\cdot}(\mathbf{a}_{u}/\mathbf{a}_{x}) \cdot dy-P^{\cdot}(\mathbf{a}_{u}/\mathbf{a}_{y}) \cdot dx)} =$$

$$r_{ij} = 0.5 \cdot (y_{j} + y_{j-1}) \cdot (P_{M} \cdot (u_{i+1}, j^{-u}_{i}, j) / x_{i} +$$

$$+ P_{M-1} \cdot (u_{i-1}, j^{-u}_{i}, j) / x_{i-1}) +$$

$$+ 0.5 \cdot (x_{i} + x_{i-1}) \cdot (P_{N} \cdot (u_{i}, j+1^{-u}_{i}, j) / y_{j} +$$

$$+ P_{N-1} \cdot (u_{i}, j-1^{-u}_{i}, j) / y_{j-1}) +$$

$$+ o(x_{i-1} + x_{i}) + o(y_{j-1} + y_{j})$$

$$(3.1-5)$$

The second and third integral of Eq. 3.1-3 can be approximated straightforwardly under the assumptions that the functions S(x,y) and F(x,y) and the solution u(x,y) are sufficiently smooth in the area  $g_{ij}$ .

$$\iint_{\mathbf{S} \cdot \mathbf{u} \cdot d\mathbf{x} \cdot d\mathbf{y}} = 0.25 \cdot \mathbf{s}_{i,j} \cdot \mathbf{u}_{ij} \cdot (\mathbf{x}_{i} + \mathbf{x}_{i-1}) \cdot (\mathbf{y}_{j} + \mathbf{y}_{j-1}) \quad (3.1-6)$$

$$\mathbf{g}_{ij}$$

$$\iint_{\mathbf{F} \cdot d\mathbf{x} \cdot d\mathbf{y}} = 0.25 \cdot \mathbf{F}_{ij} \cdot (\mathbf{x}_{i} + \mathbf{x}_{i-1}) \cdot (\mathbf{y}_{j} + \mathbf{y}_{j-1})$$

$$\mathbf{g}_{ij}$$

$$(3.1-6)$$

After combining (3.1-5), (3.1-6) and (3.1-7) and separating the unknowns, one obtains for each inner point (i,j) a linear equation of the following form:

$$\begin{array}{c} u_{i,j} \cdot ((y_{j} + y_{j-1}) \cdot (P_{M}/x_{i} + P_{M-1}/x_{i-1}) + \\ + \quad (x_{i} + x_{i-1}) \cdot (P_{N}/y_{j} + P_{N-1}/y_{j-1}) + \\ + \quad 0.5 \cdot s_{i,j} \cdot (x_{i} + x_{i-1}) \cdot (y_{j} + y_{j-1})) = \\ = u_{i+1,j} \cdot ((y_{j} + y_{j-1}) \cdot P_{M}/x_{i}) + \\ + u_{i-1,j} \cdot ((y_{j} + y_{j-1}) \cdot P_{M-1}/x_{i-1}) + \\ + u_{i,j+1} \cdot ((x_{i} + x_{i-1}) \cdot P_{N}/y_{j}) + \\ + u_{i,j-1} \cdot ((x_{i} + x_{i-1}) \cdot P_{N-1}/y_{j-1}) - \\ - 0.5 \cdot F_{i,j} \cdot (x_{i} + x_{i-1}) \cdot (y_{j} + y_{j-1}) \end{array} \tag{3.1-8}$$

In Eq. 3.1-8 no estimate of the discretisation error is given. For a non-aequidistant mesh  $(x_i \neq x_{i-1}, y_j \neq y_{j-1})$  the discretisation error decreases approximately linearly with the mesh spacings. Some ideas on proper mesh selection to sufficiently bound that error will be given in section 3.1.4. However, more exact consideration should be looked up in the classical mathematical literature e.g. /58/, /147/.

The discretisation of the boundary conditions is basically no problem. It is treated quite carefully in many lecture books on numerical mathematics e.g. /47/ so that we can refrain from an explanation.

All equations obtained by the discretisation procedure can be combined to a sparse linear operator B (3.1-9) applied to a vector u of unknowns which represent the solution at the mesh points.

$$B(u) = 0 (3.1-9)$$

Therefore, the rank of the operator B equals the total number of meshpoints which is usually rather large. However, B is also very sparse; there exist at most five elements per row. The treatment of these specially structured equations will be outlined in the following sections.

## 3.1.2 Poisson's Equation

Poisson's equation (3.1-10) is an exponentially nonlinear elliptic equation.

div

$$\boldsymbol{\xi}$$

grad  $\boldsymbol{\psi} = -q \cdot (n_i \cdot e^{(\boldsymbol{\phi}_p - \boldsymbol{\psi})/Ut}) - n_i \cdot e^{(\boldsymbol{\psi} \boldsymbol{\phi}_n)/Ut} + C)$  (3.1-10)

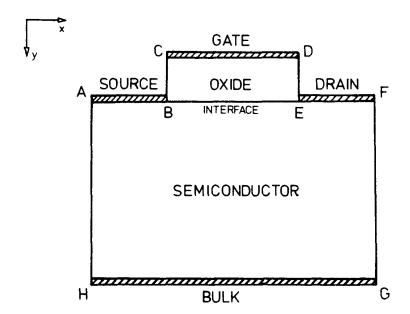

The geometry for the simulation of MOS transistors which we and many others use is shown in Fig. 3.1-2. Poisson's equation (also the continuity equations) has to be solved for the rectangular area A-F-G-H which represents the silicon region. In the area C-D-E-B which represents the gate oxide, only the Laplacian equation has to be solved because no space charge exists there. The boundary conditions are usually treated as follows: The contacts (A-B: source, E-F: drain, G-H: bulk) are assumed to be ideally ohmic. The potential is kept constant at the sum of the applied bias plus the built-in potential which is caused by the doping. At the vertical boundaries (A-H, F-G) the derivative of the potential perpendicular to the boundary (i.e. the lateral electrical field component) has to be zero. Certainly, this condition is only valid from the physical point of view if the source contact A-H and the drain contact E-F are sufficiently long. At the silicon to silicon dioxide interface the potential must obey Gauß's law (3.1-11). The existence of fixed surface states can be treated directly with Gauß's law, confer to /155/; however, we think it is more economic and sufficiently accurate to account for fixed surface states with the flatband voltage, because fixed surface states should be kept small anyway and, should, therefore, not effect the solution very much.

$$\mathbf{\varepsilon}_{ox} \cdot (\partial \psi \partial y)_{ox} = \mathbf{\varepsilon}_{si} \cdot (\partial \psi \partial y)_{si}$$

(3.1-11)

Fig. 3.1-2: The simulation geometry for planar MOSFETs

The Laplacian equation in the oxide is coupled with Poisson's equation via (3.1-11). At the gate contact (C-D) the potential is kept constant at the applied bias minus the flatband voltage; at the vertical boundaries of the oxide (C-B, D-E) the lateral electric field has to vanish.

It is interesting to note that many authors suggest a one dimensional voltage drop in the oxide e.g. /166/. In that manner one can obtain a mixed boundary condition (c.f. Eq. 3.1-2) for the potential at the interface. However, we feel that this is too crude an assumption for miniaturized MOS transistors.

# 3.1.3 Current Continuity Equations

Only the discretisation of the continuity equation for electrons will be treated in the following because the continuity equations for holes can be handled in an analogous manner. The major difficulty of the discretisation of the continuity equations is to find a proper, numerically stable formulation of the divergency of the current by just using information of physical quantities at meshpoints. A naive discretisation of the current relation (c.f. (3.1-12) for electrons) as only published in very early papers has been proved by various authors to be unstable.

However, Scharfetter and Gummel suggested already in 1969 a stable discretisation which has been physically motivated /132/. Their work can certainly be interpreted mathematically which helps in understanding various numerical phenomena associated with that discretisation. By assuming the validity of Boltzmann's statistics one gets with the substitution:

$$s = e^{-\frac{\Phi}{n}/Ut}$$

(3.1-13)

the following expression for the divergence of the electron current:

$$\operatorname{div} \overrightarrow{J}_{n} = \operatorname{q'div}(D_{n} \cdot n_{i} \cdot e^{\Psi Ut} \cdot \operatorname{grad} s)$$

(3.1-14)

This substitution is, as a matter of fact, essential because we have now a self-adjoint elliptic operator in s for the divergence of the current. For that type of operators the mathematical analysis is relatively easy and well investigated.

Recalling now the elliptic operator of the quasiharmonic equation (3.1-1), an analogy becomes evident. With:

$$P(x,y) = D_n \cdot n_i \cdot e^{\frac{2M}{2}Ut}$$

(3.1-15)

we can use the results of section 3.1.1 for the discretisation. The fundamental problem, however, is to find a proper interpolation of (3.1-15) to obtain the mid-vertex values  $P_M$  etc. A naive linear interpolation of the exponential of the electric potential is definitely not appropriate. The very best one can do from the mathematical point of view is to use an exponential interpolation. (3.1-16) is an example for this type of interpolation between points (i,j) and (i+1,j). We should like to refrain from a proof of this relation as it is fairly lengthy. The interested reader should consult e.g. /124/.

$$e_{M}^{\mathbf{u}} = e_{1}^{\mathbf{u}_{1}}, j \cdot (\mathbf{u}_{1}, j - \mathbf{u}_{1+1}, j) / (e_{1}^{\mathbf{u}_{1}}, j - \mathbf{u}_{1+1}, j - 1)$$

$$= e_{1}^{\mathbf{u}_{1}}, j \cdot ber(\mathbf{u}_{1}, j - \mathbf{u}_{1+1}, j)$$

(3.1-16)

with:

$$ber(x) = x/(e^{x}-1)$$

(Bernoulli function) (3.1-17)

The actual programming of the Bernoulli functions (3.1-17) has to be undertaken with care to avoid underflow and overflow traps /73/. Furthermore, it should be noted that only differences of potential values occur in the Bernoulli functions.

Numerical stability is, therefore, greatly increased. The leading explicit exponential of  $\Psi$  in (3.1-16) vanishes if it is combined with the s values (3.1-13) to electron densities which are numerically in an acceptable range compared to the exponentials of  $\Psi$  and  $\Psi_n$ .

The mystery of the stability of the discretisation which has just been outlined lies in the fact that it represents a so-called "windward" difference approximation. For a large potential drop between neighbouring meshpoints the windward scheme degenerates in a forward- or backward difference scheme depending on the sign of the potential difference (i.e. electric field). Therefore the propagation of local errors is very small.

The boundary conditions are very simple for the continuity equations. At the contacts (A-B, E-F, G-H in Fig. 3.1-2) the carrier densities are set constant to their equilibrium value. At the remaining boundaries (B-E, F-G, A-H) no current component perpendicular to the boundary must exist.

A very interesting and successfully applied alternative to the outlined discretisation has been proposed by Mock /108/ for the MOS transistor. Through the introduction of so-called "stream-functions" one also obtains a self-adjoint operator for the divergence of the current with similar problems in the interpolation of exponentials of the electric potential. The treatment of inhomogeneities i.e. recombination/generation, however, is more complicated with stream-functions. Therefore we favour the other discretisation.

### 3.1.4 Grid Generation

To keep computer time as well as memory requirements reasonably small, it is necessary to limit the number of mesh points. A suitable tradeoff between accuracy and computing costs can be found once the discretisation errors are estimated. In critical regions with large discretisation errors grid spacing has to be kept small whereas it may be large in regions in which only small errors occur. Such considerations make it evident that an equidistant mesh is not suitable because in that case grid spacing has to be adapted to the critical regions and the number of mesh points would be very large.

As the discretisation errors depend on the distribution of the quantities ,n,p a suitable mesh cannot be estimated a priori, that is without knowledge of the solution. Therefore, grid generation is performed adaptively, i.e. a priliminary solution is calculated on the basis of an initial mesh, then the mesh is adapted to this solution and again the basic equations

are solved. Regeneration of the mesh can be done repeatedly if necessary.

Let f(x) be a four times continuously differentiable function; then one can savely write;

$$f_{i+1} = f_i + f'_i h_i + f'_i \frac{h_i^2}{2} + f'_i \frac{h_i^3}{6} + f^{IV}(\xi) \frac{h_i^4}{24}$$

(3.1-18)

$$f_{i-1} = f_i - f_i h_{i-1} + f_i' \frac{h_{i-1}^2}{2} - f_i'' \frac{h_{i-1}^3}{6} + f^{IV}(\xi) \frac{h_{i-1}^4}{24}$$

(3.1-19)

and we get for the second order differential quotient:

$$f''(x_{i}) = 2 \cdot \frac{(f_{i+1} - f_{i})/h_{i} + (f_{i-1} - f_{i})/h_{i-1}}{h_{i} + h_{i-1}} + f_{i}'' \cdot \frac{h_{i} - h_{i-1}}{3} + f^{IV}(\xi) \cdot \frac{h_{i}^{2} - h_{i}h_{i-1} + h_{i-1}^{2}}{12}$$

(3.1-20)

The first term on the right hand side of eq. (3.1-20) is the finite difference approximation. The other two terms represent the discretisation error. For an aequidistant mesh  $(h_i=h_{i-1})$  the second term on the right hand side vanishes and only differentials of at least fourth order cause discretisation errors. Principially eq. (3.1-20) can be used to fix the mesh spacing  $h_i$  for given largest acceptable error, knowledge of the fourth differential provided, and also to bound the maximum mesh progression  $F_i$  when knowing the third differential

progression

$$V_i$$

when knowing the third differential

$$V_i = \max \left(\frac{h_i}{h_{i-1}}, \frac{h_{i-1}}{h_i}\right). \tag{3.1-21}$$

The errors which are induced by the finite difference approximation of the inhomogeneity terms are going to be considered in the following. The inhomogeneities around each mesh point up to the next midpoint are approximated by

$$x_{i} + \frac{h_{i}}{2} \quad y_{j} + \frac{k_{j}}{2}$$

$$\int_{\mathbf{F}(\mathbf{x}, \mathbf{y}) \cdot d\mathbf{x} \cdot d\mathbf{y}} \mathbf{f}(\mathbf{x}, \mathbf{y}) \cdot d\mathbf{x} \cdot d\mathbf{y} = 0.25 \cdot \mathbf{F}_{i, j} (h_{i} + h_{i-1}) (k_{j} + k_{j-1}) \quad (3.1-22)$$

$$x_{i} - \frac{h_{i-1}}{2} y_{j} - \frac{k_{j-1}}{2}$$

with F(x,y) being the inhomogeneity term. For a one dimensional error estimation a series expansion of F(x) yields:

$$x_{i} + \frac{h_{i}}{2}$$

$$\int_{h_{i-1}}^{F(x) \cdot dx} F(x) \cdot dx = \frac{1}{2}F_{i}(h_{i} + h_{i-1}) + F_{i}' + \frac{h_{i}^{2} - h_{i-1}^{2}}{8} + F''(\xi) + \frac{h_{i}^{3} + h_{i-1}^{3}}{24}$$

$$(3.1-23)$$

The first term in (3.1-23) is the finite difference approximation as given in (3.1-22) and the two other terms describe the local error. The global error is extremely difficult to estimate. However, it is often of by one reduced order.

If we consider Poisson's equation once again, the second differential of the space charge limits the mesh spacing and the first differential limits mesh progression.

$$\mathbf{r}_{i} - 1 = 4 \frac{\mathbf{r}_{max}}{\mathbf{r}_{i}^{!} \cdot \mathbf{h}_{i-1}}$$

(3.1-24)

$$h_i^2 = 12 \frac{\epsilon_{max}}{F^{(i)}(\xi)}$$

(3.1-25)

As already discussed earlier ionisation rates are very sensitive to the electric field. Therefore, the generation rate exhibits an abrupt peak in the pinch-off region which can only be kept under control with a very fine discretisation. The integral of the generation rate over the total area gives the substrate current, and the discretisation error is, therefore, proportional to the error of the substrate current. If we consider only the first derivative of the electric field

$$E(x) \triangleq E(x,) + (x-x,) \cdot E'(x,)$$

we get for d'' on the basis of Chynoweth's law:

$$\mathbf{d}(\mathbf{x}) \doteq \mathbf{A} \cdot \exp \left[ \frac{-\mathbf{B}}{\mathbf{E}_{i}} \cdot (1 - \frac{(\mathbf{x} - \mathbf{x}_{i}) \mathbf{E}_{i}^{!}}{\mathbf{E}_{i}}) \right]$$

$$\mathbf{d}'(\mathbf{x}_{i}) \doteq \frac{\mathbf{B}}{\mathbf{E}_{i}^{2}} \cdot \mathbf{E}_{i}' \cdot \mathbf{d}'(\mathbf{x}_{i})$$

(3.1-26)

$$\mathbf{d''}(\mathbf{x}_{i}) \doteq \left[\frac{\mathbf{B}}{\mathbf{E}_{i}^{2}} \cdot \mathbf{E}_{i}^{1}\right]^{2} \cdot \mathbf{d}(\mathbf{x}_{i})$$

(3.1-27)

By substituting these expressions in (3.1-24), (3.1-25) we get some rules for the mesh generation. If one likes to limit the maximum relative error in the substrate current, it is useful to divide (3.1-26), (3.1-27) by the maximum ionization rate which occurs in the device.

## 3.2 Linearization of the Coupled System

In this section we should like to discuss some properties of one-step stationary iterative methods of the form (3.2-2) for the solution of systems of nonlinear equations (3.2-1).

$$\mathbf{F}(\mathbf{x}) = 0 \tag{3.2-1}$$

$$\mathbf{x}^{k+1} = \mathbf{G} \cdot \mathbf{x}^k \tag{3.2-2}$$

The problem (3.2-1) be properly defined /124/. Suppose the operator G has a fixed point  $x^*$ . Then (3.2-2) will converge to  $x^*$  if G is F-differentiable /124/ at  $x^*$  and if the spectral radius of it's Jacobian  $G'(x^*)$  satisfies Eq. (3.2-3).

$$\mathbf{Q}(G'(\mathbf{x}^*)) \leqslant 1 \tag{3.2-3}$$

This very important theorem (Ostrowski theorem) is the basis of all investigations on the convergence of one-step iterations for the solution of nonlinear equations. In the following we should like to write the discretised semiconductor equations in a more abstract form to simplify the formulae. Let (3.2-4) be Poisson's equation and (3.2-5), (3.2-6) the continuity equations for electrons and holes in the unknowns  $\psi$ ,  $\psi_n$  and  $\psi_p$  which represent vectors of the meshpoint values of the electrostatic potential, the quasifermilevel of electrons and holes, respectively.

$$F1 = F1(\mathbf{\Psi}, \mathbf{\Psi}_n, \mathbf{\Psi}_p) = 0 \tag{3.2-4}$$

$$F2 = F2(\Psi, \Psi_n, \Psi_p) = 0$$

(3.2-5)

$$F3 = F3(\Psi, \Psi_n, \Psi_n) = 0$$

(3.2-6)

Then F1, F2 and F3 represent a nonlinear system of equations with the rank 3 (NX·NY) which is three times the total number of meshpoints, usually a large number. We have now to find some operators G which are relatively easy to calculate and for which condition (3.2-3) holds. The best known method is certainly the classical Newton-Raphson method.

#### 3.2.1 Newton's Method and Modified Newton Methods

For Newton's method the iteration is defined as follows:

The operator G is, therefore, defined as:

$$G = (I - F^{-1} \cdot F) \tag{3.2-8}$$

It can be proved that the Jacobian G' of this operator has only zero eigenvalues at  $x^*$ ,  $F(x^*)=0$  and fulfills trivially condition (3.2-3). As all eigenvalues are zero, even quadratic convergence is anticipated as the solution is approached /124/, /126/. Although Newton's method is very attractive from the mathematical point of view, there are practical difficulties.

The main implementation problem is the evaluation of the derivative terms in equation (3.2-7), since the total equation (including modeled physical parameters) must be differentiated accurately with respect to the variables  $\psi$ ,  $\psi_n$  and  $\psi_p$ . This can be done analytically, in principle, but one loses much flexibility in changing the models of the physical parameters. Therefore, a numerical algorithm is necessary to automatically calculate the required derivatives. The best algorithm known at the moment has been published by Curtis and Reid /34/. Some very interesting comments on numerical differentiation have also been given in /81/.

Another fairly difficult problem when considering Newton's method is overshoot. The iteration process does not neccesarily converge monotonously to the solution. Especially, if one starts the iteration with a bad initial guess - which is the usual situation - monotonic convergence or convergence at all cannot be guaranteed. Therefore, one has to introduce a mechanism which dampens the increments resulting from the iteration process so that convergence is monotonic. The naive algorithms simply limit the increments to some maximum value e.g. /108/ or they use some function to continuously limit large increments e.g. /19/. Deuflhardt suggested a more elaborate method /44/, /45/. Roughly explained, he calculates a parameter y in the range y0,1y3 so that condition (3.2-9) holds.

$$\|\mathbf{F}^{-1}(\mathbf{x}^{k}) \cdot \mathbf{F}(\mathbf{x}^{k} + \mathbf{y} \cdot (\mathbf{x}^{k+1} - \mathbf{x}^{k}))\| < \|\mathbf{F}^{-1}(\mathbf{x}^{k}) \cdot \mathbf{F}(\mathbf{x}^{k})\|$$

(3.2-9)

After having found V, the solution  $x^{k+1}$  is calculated with Eq. (3.2-10).

$$x^{k+1} = x^k + \mathbf{y} \cdot (x^{k+1} - x^k)$$

(3.2-10)

This procedure guarantees monotonic convergence; for  ${\cal Y}\!\!=\!\!1$  it is the classical Newton method.

Another excellent method was proposed by Meyer /104/. He suggested to modify the iteration operator G by introducing a positive parameter  $\lambda$  as given in Eq. (3.2-11).

$$G = (I - (\lambda \cdot I + F')^{-1} \cdot F)$$

(3.2-11)

$\lambda$  has to be chosen as small as possible so that the norm of  $F(x^{k+1})$  is smaller than the norm of  $F(x^k)$ . Some practical guidelines on how to find this parameter  $\lambda$  with reasonable effort have been recently presented by Bank and Rose /9/.

It is very time and also memory consuming to solve the large linear system which, nevertheless, has to be done for every Newton step. Therefore, many authors use another iterative algorithm, suggested by Gummel /69/, for the linearization of the semiconductor equations.

#### 3.2.2 Block-Nonlinear Iteration

Gummel's idea, in essence, was to solve the semiconductor equations by independently linearizing each equation consecutively with respect to its dominant variable. The first step is to solve Poisson's equation with Newton's method assuming that the quasifermilevels are known functions of position; i.e. the best guess of the quasifermilevels is assumed to be correct. In the second step one of the continuity equations is solved assuming that the electric potential and the quasifermilevel of the other continuity equation are correct. In the third step the second continuity equation is solved under similar assumptions. These three steps are performed repeatedly until a consistent solution is found. The effort for one cycle of this blocknonlinear iteration is obviously less than for one Newton step because the rank of one decoupled equation system is only a third of the rank of the total system.

A complete theoretical proof of the convergence of the block-nonlinear iteration algorithm has as yet not been published. However, strong theoretical indications have been given by Mock /109/. One should also not underestimate the "practical" indications; many authors have used Gummel's iterative scheme with excellent success.

It should also be noted that a few authors have published modifications of the original Gummel method e.g. /14/, /133/, /156/. These modifications are basically motivated on intuition. They are, therefore, as arbitrary as the original approach itself. However, for special purpose applications some improvement in efficiency could be gained.

## 3.3 Solution of Large Sparse Linear Systems

For any of the linearization procedures which have been outlined in section 3.2 a large sparse linear equation system (3.3-1) has to be solved repeatedly.

$$A \cdot x = b \tag{3.3-1}$$

We assume that A has been derived by linearizing five-point-star discretized PDEs. Hence matrix A has at most five nonzero entries per row; A is very sparse. For a full Newton scheme these entries are 3x3 matrices; for Gummel's scheme they are scalars. For the solution of these special types of linear equation systems two classes of methods, can, in principle, be used: direct methods which are based on elimination and iterative methods. An excellent survey on that subject has been published recently by Duff /48/.

#### 3.3.1 Direct Methods

Classical Gaussian elimination is not feasible for our systems of equations because the rank of A in (3.3-1) is very large and A has many coefficients which are zero. Therefore, some modifications of the classical Gaussian elimination algorithm have to be introduced to account for the zero entries. There exist quite a few activities on that subject (c.f. /49/) and powerful algorithms which treat the nonzero coefficients only are available. Another serious drawback of direct methods lies in the fact that the upper triangular matrix which is created by the elimination process has to be stored for back substitution. This matrix has usually more nonzero entries than the matrix A. Therefore, memory requirement of direct methods is substantial.

In spite of all drawbacks of direct methods, their major advantage is high accuracy of the solution. However, we feel that for the semiconductor problems iterative algorithms are to be slightly favoured.

### 3.3.2 Relaxation Methods

The fundamental idea of relaxation methods is the splitting of the coefficient matrix A (3.3-1) into three matrices D, E, F (3.3-2).

$$A = D - E - F$$

(3.3-2)

D denotes the diagonal entries of A; -E denotes a lower triangular matrix which is formed from all sub-diagonal entries of A; and -F denotes an upper triangular matrix which is formed from all super-diagonal entries of A.

With an arbitrary non-singular matrix B which has the same rank as A the linear system (3.3-1) can be rewritten to (3.3-3).

$$B \cdot x + (A-B) \cdot x = b$$

(3.3-3)

One obtains an iterative schema by setting:

$$B \cdot x^{k+1} = b - (A-B) \cdot x^k \tag{3.3-4}$$

(3.3-4) can be solved for  $x^{k+1}$ :

$$x^{k+1} = (I-B^{-1} \cdot A) \cdot x^k + B^{-1} \cdot b$$

(3.3-5)

The iterative scheme (3.3-5) will converge if condition (3.3-6) holds.

$$\mathbf{Q}(\mathbf{I}-\mathbf{B}^{-1}\cdot\mathbf{A}) < 1 \tag{3.3-6}$$

(3.3-6) is a necessary and sufficient condition. The various relaxation methods can be won by differently setting matrix B with the matrices obtained by the splitting of A (3.3-2).

The simplest scheme, the point-Jacobi method, uses D for B. Matrix D is a diagonal matrix and is, therefore, easily invertible.

The Gauss-Seidel method uses D-E for B. The matrix D-E is a lower triangular matrix. Therefore one has only to perform a forward substitution process for its inversion.

The successive overrelaxation method (SOR) makes use of a parameter  $\boldsymbol{w}$  within the range  $\boldsymbol{J}_0, 2\boldsymbol{L}$ . The iteration matrix B is defined:

$$B = D/\mathbf{w} - E \tag{3.3-7}$$

As B is again a lower triangular matrix, its inversion is instantly reduced to a substitution.

The major advantage of these iterative methods lies in their simplicity. They are very easy to program and demand only low memory requirement. As already noted, they converge if condition (3.3-6) holds. However, it is difficult to prove that condition. A sufficient condition for convergence is that A is positive definite (3.3.-8) which is the regular case for five-point-star discretized PDEs.

$$\mathbf{x}^{\mathbf{T}} \cdot \mathbf{A} \cdot \mathbf{x} > 0 \text{ for all } \mathbf{x} \neq 0$$

(3.3-8)

These point-iterative schemes can by accelerated quite remarkably with the conjugate gradient method or the Chebyshev method. An excellent survey on these topics can be found in /68/.

## 3.3.3 Strongly Implicit Iterative Methods

The convergence rate of relaxation methods is relatively poor. Therefore, various activities can be observed for the development of more powerful algorithms with the advantages of iterative schemes.

One of the best known algorithms which has been established in semiconductor device analysis is perhaps Stone's strongly implicit procedure /151/. Stone's idea was to modify the original coefficient matrix A by the addition of a small matrix N so that a factorization of (A+N) involves much less computational effort than the standard decomposition of A and the norm of N is much smaller than the norm of A. Assuming this has been done, the development of an iterative procedure is then fairly straightforward because the equation can be written as:

$$(A+N) \cdot x = (A+N) \cdot x + (b-A \cdot x)$$

(3.3-9)

which suggests the iterative procedure:

$$(A+N) \cdot x^{k+1} = (A+N) \cdot x^k + (b-A \cdot x^k)$$

(3.3-10)

When the right hand side is known and (A+N) can be factorized easily, (3.3-10) gives an efficient method for directly solving for  $x^{k+1}$ . Furthermore, one would intuitively expect a rapid rate of convergence if N is sufficiently small compared to A. We will refrain from explaining in detail Stone's suggestion of how to choose the perturbation matrix N because this has been done thoroughly in many publications e.g. /59/, /147/, /151/.

There exist a few algorithms which are similiar in terms of underlying ideas compared to Stone's method. The most attractive are perhaps the method of Dupont et al. /50/, the "alternating direction implicit" methods e.g. /16/, /59/, /178/ and the Fourier methods /150/, /177/.

One disadvantage of all strongly implicit methods and also the direct methods is that they cannot be implemented efficiently on a computer with a pipe-line architecture (vector processor). Some comments on that subject have been given in /48/.

#### +. TYPICAL APPLICATIONS OF MINIMOS

# +.1 A Didactic Example

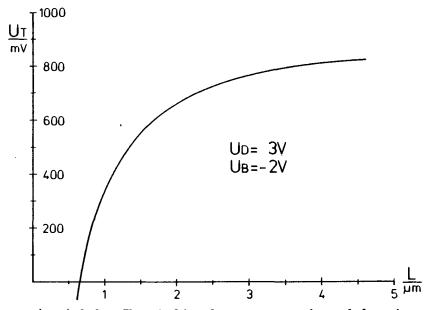

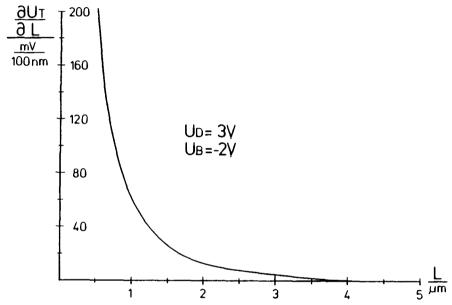

It is rather difficult to provide an interesting example for the experienced reader, which is also impressive and easy to understand for readers with general interest in modeling but without specific knowledge of device physics. We have chosen the effects of ion implantation on short channel MOS transistors for the purpose of demonstrating the use of two dimensional simulation. Three devices are calculated whose properties become apparent from the original simulation input decks presented in Fig. 4.1-1. The following discussion of Fig. 4.1-1 shall also demonstrate the ease of using MINIMOS /138/, /139/, /140/, /142/, our simulation program.

The first line is a title line, which is used only to identify the output of the program. The input syntax is totally based on a master key, key and value structure. The next input line which is the "DEVICE" statement, characterizes the device. Specified is an n-channel device (CHANNEL=N) with an n-doped polysilicon gate (GATE=NPOLY), an oxide thickness of nanometers (TOX=350.E-8), a channel width of 10 micrometers (W=10.E-4) and a channel length of one micrometer (L=1.E-4). "BIAS" statement specifies the operating point. A drain voltage of 3 volts (UD=3.) and a gate voltage of zero volts (UG=0.) has chosen. The substrate voltage is assumed to be zero by MINIMOS, if not specified otherwise.

The "PROFILE" statement is used to specify the substrate doping and the source/drain diffusion. In the examples presented here we used the simplest way of defining a doping profile, that is the direct calculation by MINIMOS. Another possibility would be to make use of a technology simulation program like SUPREM, the Stanford University PRocess Engineering Models program /6/, for the more accurate calculation of vertical profile shapes which are fitted in the lateral direction. For our simulation a substrate doping of 10 cm (NB=1.E15) and a source/drain implantation with phosphorus (ELEM=PH), an implantation dose of 10 cm (DOSE=1.E15) and an implantation energy of 40keV (AKEV=40) is specified. The implantation is performed through an isolation oxide of 35 nanometers (TOX=350.E-8) and followed by an annealing step at 1000 centigrades (TEMP=1000) for 1200 seconds (TIME=1200).

ONE-MICRON ANALYSIS (DEVICE 1)

DEVICE CHANNEL=N GATE=NPOLY TOX=350.E-8 W=10.E-4 L=1.E-4

BIAS UD=3. UG=0.

PROFILE NB=1.E15 ELEM=PH DOSE=1.E15 AKEV=40 TOX=350.E-8

+ TEMP=1000 TIME=1200

END

ONE-MICRON ANALYSIS (DEVICE 2)

DEVICE CHANNEL=N GATE=NPOLY TOX=350.E-8 W=10.E-4 L=1.E-4

BIAS UD=3. UG=0.

PROFILE NB=1.E15 ELEM=PH DOSE=1.E15 AKEV=40 TOX=350.E-8

+ TEMP=1000 TIME=1200

IMPLANT ELEM=B DOSE=3.5E11 AKEV=25 TEMP=925 TIME=1800

END

ONE-MICRON ANALYSIS (DEVICE 3)

DEVICE CHANNEL=N GATE=NPOLY TOX=350.E-8 W=10.E-4 L=1.E-4

BIAS UD=3. UG=0.

PROFILE NB=1.E15 ELEM=PH DOSE=1.E15 AKEV=40 TOX=350.E-8

+ TEMP=1000 TIME=1200

IMPLANT ELEM=B DOSE=3.5E11 AKEV=25 TEMP=925 TIME=1200

IMPLANT ELEM=B DOSE=1.5E11 AKEV=100

END

Fig. 4.1-1: Some typical input decks for MINIMOS

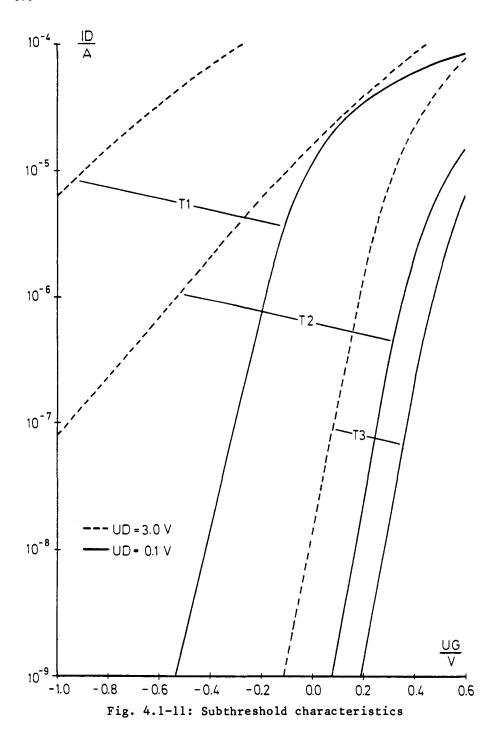

The second input deck further includes an "IMPLANT" statement which defines a channel implantation with boron (ELEM=B), a dose of  $3.5 \cdot 10^{11} \text{cm}^{-2}$  (DOSE=3.5E11), an energy of 25keV (AKEV=25), annealed at 925 centigrades (TEMP=925) for 1800 seconds (TIME=1800). The third input deck has an additional channel "IMPLANT" statement specifying a second, deeper channe implantation with boron (ELEM=B), a dose of 1.5·10 cm (DOSE=1.5E11) and an energy of 100keV (AKEV=100). It is assumed that both channel implantation steps are annealed at the same time. It is fairly well known that the first of these three devices is, owing to the short channel effect, "normally-on" and that the shallow implantation of device 2 effects a threshold shift to obtain a "normally-off" device. Furthermore, the deep implantation of device 3 is necessary to avoid punch through. These effects will now be demonstrated by birds-eye-view- and contour-plots of physically relevant quantities in the interior of the three model devices.

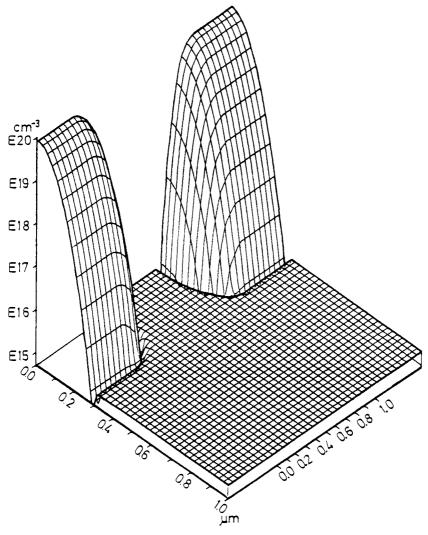

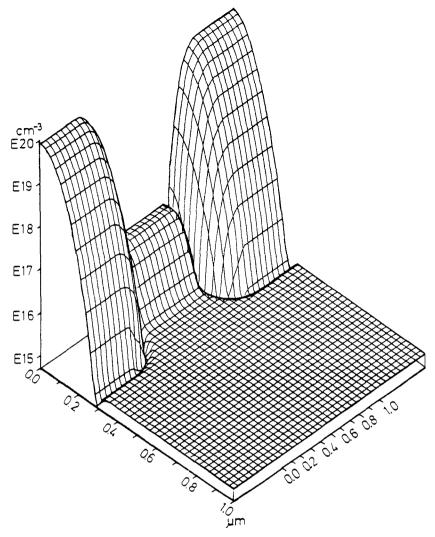

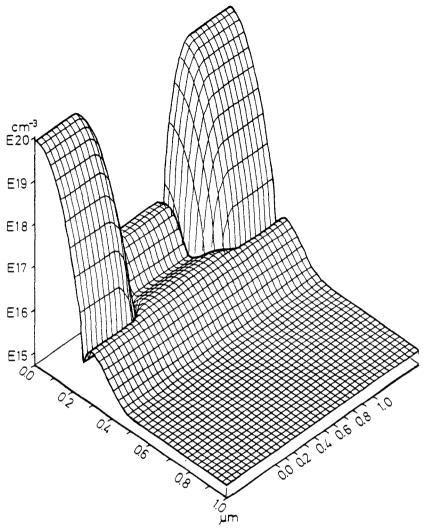

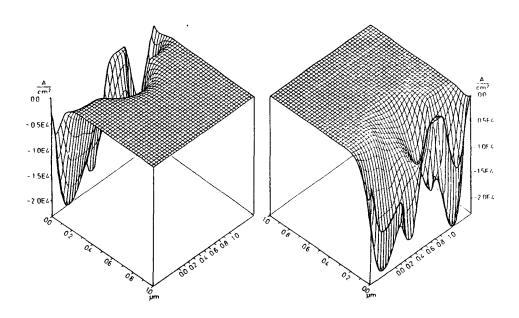

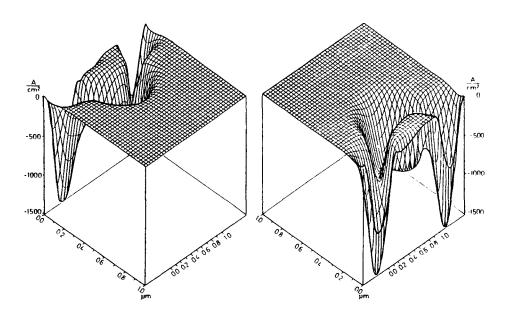

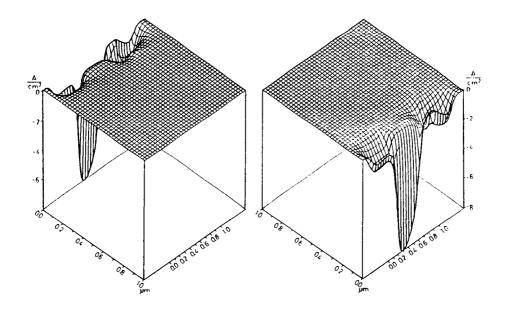

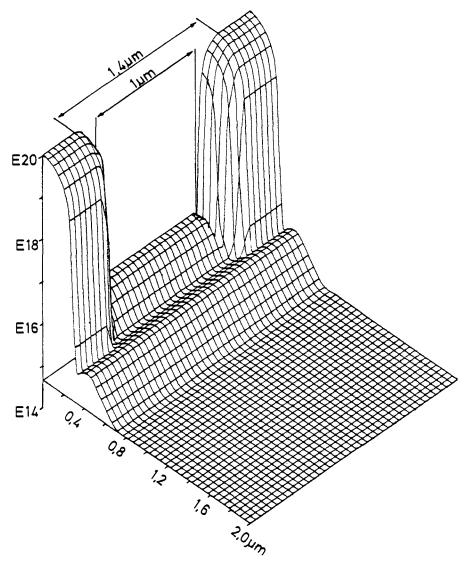

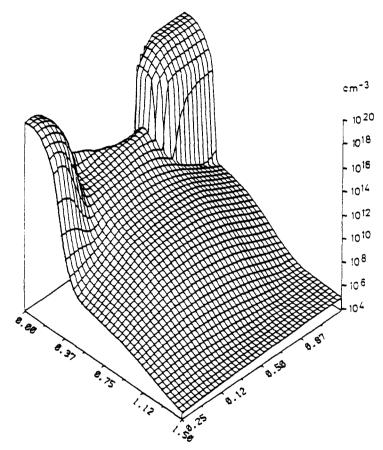

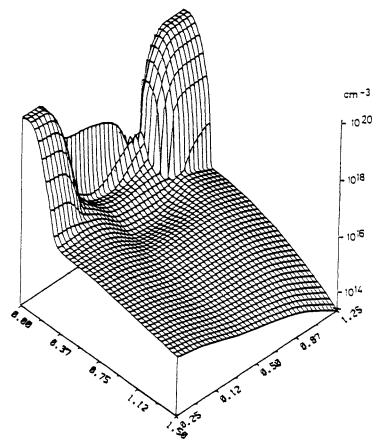

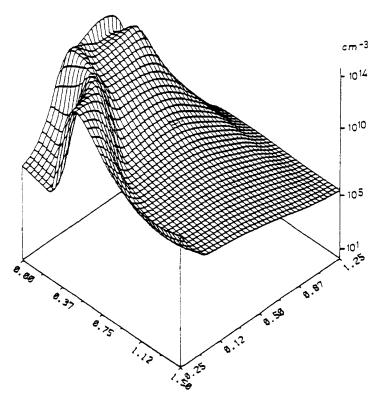

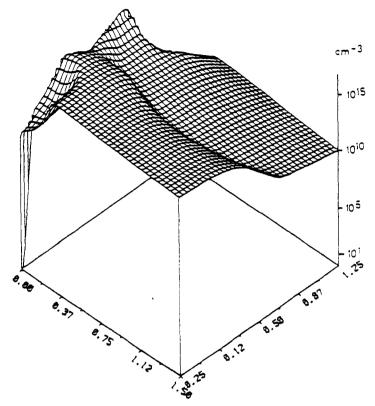

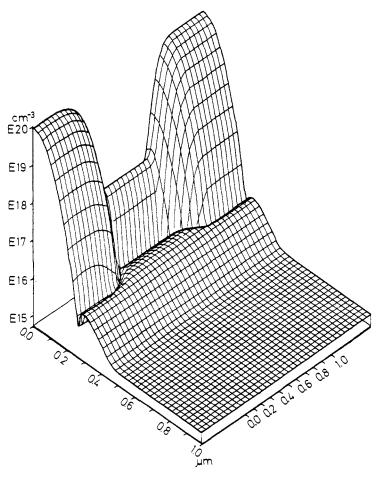

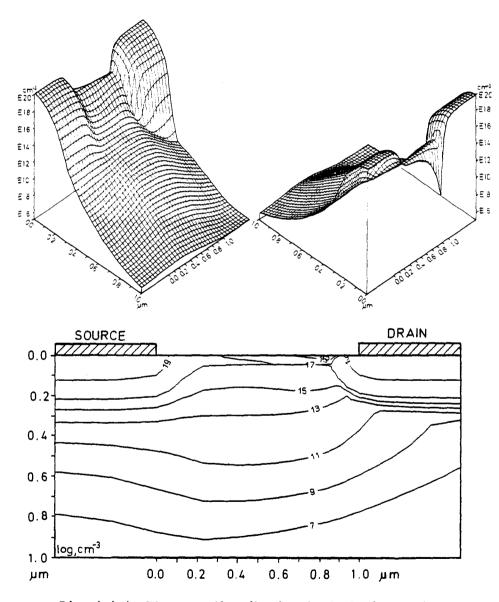

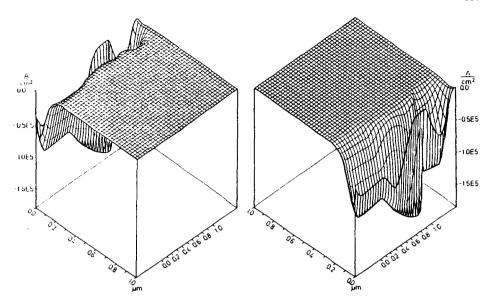

The calculated doping density distributions for our devices are shown in Figs. 4.1-2, 4.1-3, 4.1-4.

Fig. 4.1-2: Doping profile for device 1

From these figures one can read off the depth of the pn-junctions under source and drain being approximately 300 nanometers. The surface concentration of the source and drain regions is about  $10^{20} \, \mathrm{cm}^{-3}$ . The effective channel length is reduced by the lateral subdiffusion to about 0.6 micrometers. The shallow channel implantation for threshold tailoring can be seen in Figs. 4.1-3, 4.1-4. Additionally, Fig. 4.1-4 shows the deep implantation for punch through suppression. The threshold voltage is only marginally affected by the deep implantation.

Fig. 4.1-3: Doping profile for device 2

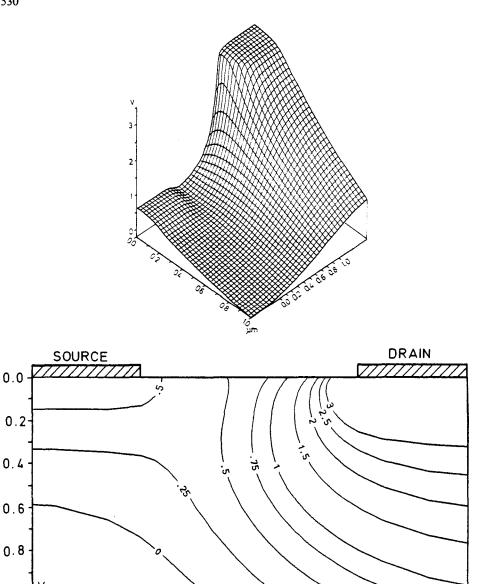

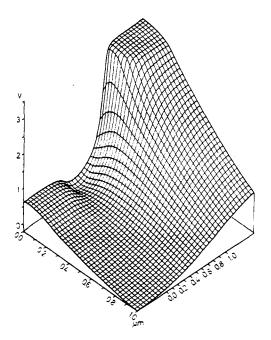

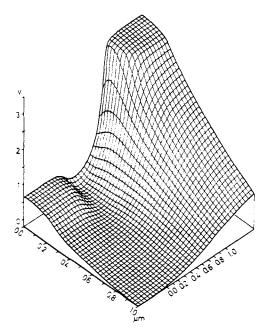

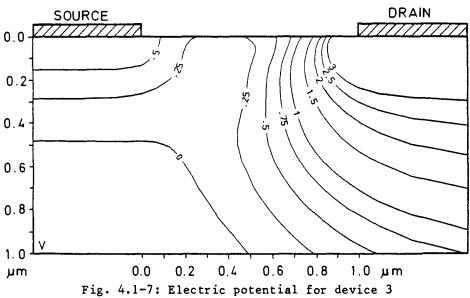

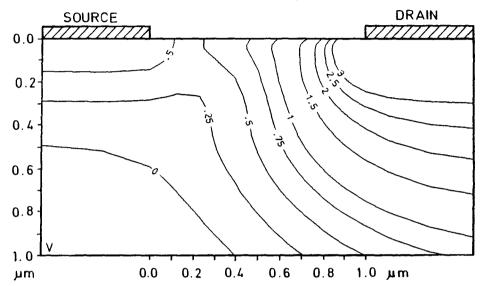

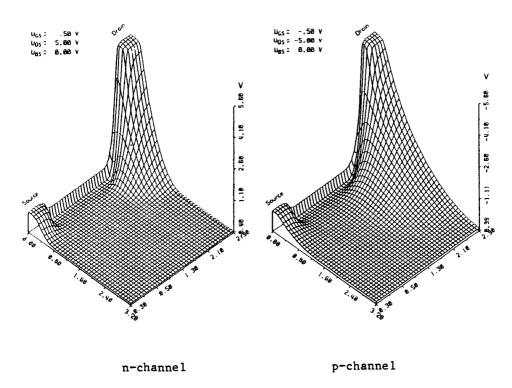

Fig. 4.1-5 shows the distribution of the electric potential for the first device. The drain contact is on the right. In the depletion region of the reverse biased drain-bulk diode the potential decreases monotonously and it is more or less constant in the highly doped source and drain regions. The barrier at the source channel diode is relatively small /168/. Fig. 4.1-6 shows the potential distribution in the second device. The birds-eye-view plot looks very similar to the plot in Fig. 4.1-5.

Fig. 4.1-4: Doping profile for device 3

The contour-plot, however, shows quite a pronounced potential basin directly below the interface. Of even greater importance than this basin itself is the saddlepoint below the basin. At this saddlepoint the electric field vanishes and current only can flow by carrier diffusion. This sort of saddle-point is, following the proposition of many authors (e.g. /12/, /87/), a typical indication of the punch-through effect. The electric field which is induced by the gate is unable to separate the depletion regions of source and drain.

1.0

μm

These depletion regions are in contact below the region of control by the gate. As it will become apparent later , the saddlepoint is a reliable indication of the punch-through effect, but it need not exist.

0.4

Fig. 4.1-5: Electric potential for device 1

0.6

0.8

1.0 µm

0.2

0.0

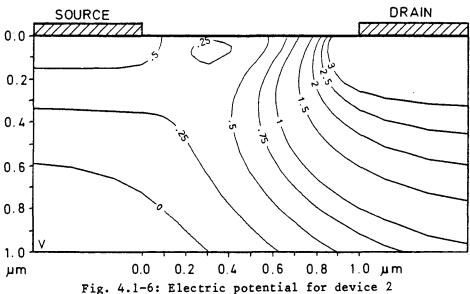

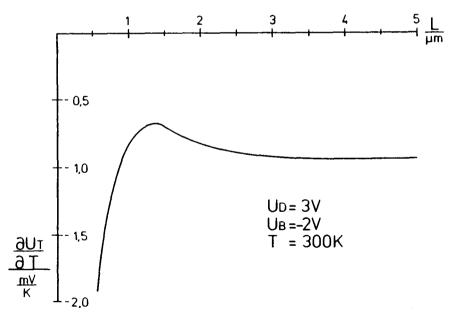

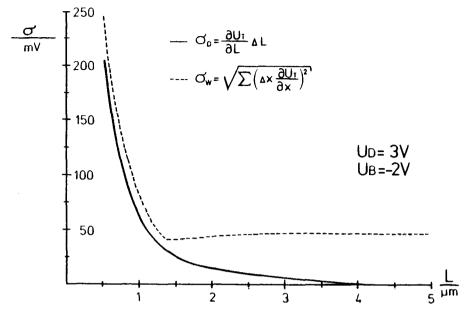

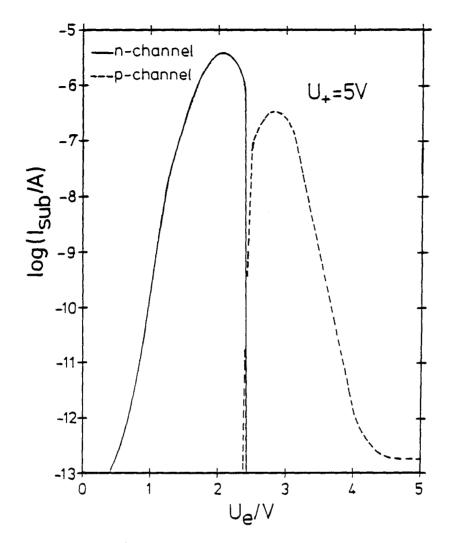

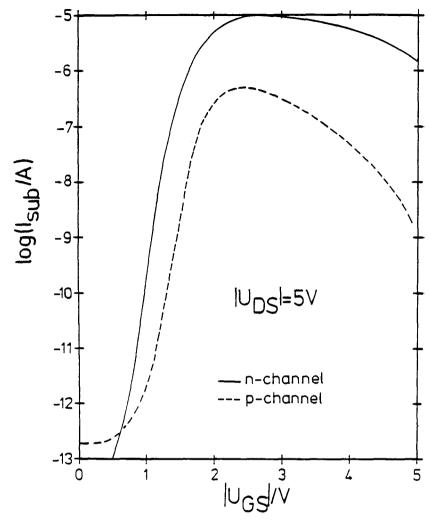

Fig. 4.1-7 shows the potential distribution in the third device. The birds-eye-view plot differs just marginally from the plot in Fig. 4.1-6. But from the contour plot one can see a well pronounced barrier between source and channel which guarantees the "normally-off" behaviour.