# Accurate High Temperature Measurements Using Local Polysilicon Heater Structures

Gregor Pobegen, Michael Nelhiebel, Stefano de Filippis and Tibor Grasser, Senior Member, IEEE

Abstract—Conventionally, measurements of temperaturedependent device parameters and degradation are performed using thermo chucks or dedicated test-furnaces. With such an equipment, the available temperature range is limited (typically to a maximum of 300 °C) and reliable temperature switches are rather slow, i.e. in the range of minutes to hours. We refine the recently suggested use of polycrystalline silicon wires - socalled poly-heaters - embedded directly on the chip next to a semiconductor device under test, to allow for fast, accurate and reliable local temperature control. Based on our previous experience with such structures, we extend the use of the polyheater to even higher temperatures using a simple methodology. For this we determine the temperature of the device by the electrical power dissipated in the heater wires where we take the temperature dependency of the thermal resistances of the materials surrounding the heater and the device into account. With this approach we obtain convincing agreement for comparisons with experimental data and a three-dimensional electrothermal FEM simulations.

### I. Introduction

NEARLY all parameters of a semiconductor depend strongly on the temperature of the material. These dependencies have a strong impact on the performance of semiconductor devices and their reliability. In particular, in metal-oxide-semiconductors field effect transistors (MOSFETs) temperature strongly impacts virtually all reliability limiting mechanisms, including the bias temperature instability (BTI) [1–4], random telegraph noise [5, 6], hot carrier degradation [7, 8] and time-dependent dielectric breakdown (TDDB) [9, 10]. In order to investigate device performance and reliability issues with respect to temperature, fast and accurate control of the device temperature is thus highly desirable.

Usually, the device temperature is controlled by thermo chuck systems (for measurements directly on the wafer) or by dedicated furnaces equipped with electrical connections for diced devices under test. Both approaches have the drawback that reliable changes of the device temperature are rather slow (i.e. in the range of minutes to hours). For wafer-level test systems it is usually not possible to maintain the bias applied to the junctions of the device during temperature switches

G. Pobegen, M. Nelhiebel and S. de Filippis are with KAI–Kompetenzzentrum für Automobil- und Industrieelektronik, 9500 Villach, Austria (e-mail: gregor.pobegen@k-ai.at).

S. de Filippis is with the Dipartimento di Ingegneria Biomedica, Elettronica e delle Telecomunicazioni, Università degli Studi di Napoli "Federico II", 80125 Napoli, Italy.

G.Pobegen and T. Grasser are with the Institute for Microelectronics, TU Vienna, 1040 Vienna, Austria.

Manuscript received January 29, 2013; revised May 23, 2013.

because the thermal expansion of the needles may push them off the pad. Furthermore, the experimental effort increases considerably in the temperature range above  $\approx 300\,^{\circ}\text{C}$  because the whole experimental setup needs to be built from materials which can sustain such temperatures mechanically [11].

1

The poly-heater [12–18] is a simple local heating structure which overcomes the limitations described above. It consists of two poly-crystalline silicon wires which closely surround the device under test directly on the chip (cf. [14, 17, 18] for layouts and cross sections of the poly-heater). When power is supplied to the poly-heater, the wires and the device in thermal contact become hot due to Joule heating. The underlying idea dates back to the year 1992, when on-chip heaters were first built from polycrystalline silicon and placed in the close vicinity of a MOSFET or a bipolar transistor [12].

Such poly-heaters are often used for fast wafer level reliability monitoring of process influences [17]. However, they have so far only rarely been used in degradation research or device development. This might be due to the disadvantage that the device temperature versus heater power characteristic usually has to be calibrated for every single device under test before use. As such, the various possibilities for testing the performance and reliability of semiconductor devices conveniently at temperatures above 300 °C are still largely unexplored [2, 18].

In order to prepare the use of the poly-heater for research and development, also for temperatures beyond 300 °C, we suggest a reliable, accurate and easy-to-use method to determine the temperature of the device under test. Compared to the conventional calibration method, our methodology reduces the experimental effort to a single electrical calibration step per technology. This calibration gives three coefficients which characterize the change of the thermal resistance of the substrate with temperature. These coefficients can then be used to directly calculate the device temperature from the power dissipated in the poly-heater with a simple formula.

### II. DETERMINATION OF THE DEVICE TEMPERATURE

The main reason why the poly-heater has only been rarely used in the scientific community might be related to doubts regarding the actual device temperature given a certain electrical power supplied to the poly-heater. The temperature of the poly-heater itself can be determined straightforwardly with the change of its electrical resistance, since the relative change of the poly-silicon resistivity is usually known to manufacturers or can be determined experimentally. But as there is a temperature difference between the Joule heated

poly-heater wires (hottest point) and the heat sink at the backside of the wafer (coldest point) [18], the temperature of the device under test can be significantly different from the temperature of the poly-heater and must be determined independently. As such, the temperature is usually determined using the temperature dependency of a device terminal current. The use of a device current as a temperature sensor prohibits to perform an arbitrary electrical experiment on the device during poly-heater use. Therefore, a relation of the device temperature versus the power dissipated in the poly-heater must be found prior to the experiment. If the target temperature of the experiment is within the range of the preceding calibration with a thermo chuck or a furnace, the device temperature can be easily determined by interpolation. However, if temperatures above the temperature range of thermo chucks or furnaces are targeted - and this is one of the main benefits of the poly-heater [2] - a calibrated extrapolation method for the device temperature as a function of the poly-heater power is needed. In the following we will describe a simple but still very accurate and reliable extrapolation method based on the temperature dependency of the thermal resistance of the semiconductor substrate.

### A. Device temperature measurement

Already in the first reported uses of the poly-heater the forward current of a p-n junction within the semiconductor was used to estimate the temperature of the whole device [13]. For example, the source-drain to bulk diode was typically used for MOSFETs [13, 14, 17]. Even though this approach ignores the temperature difference between the active MOSFET interface and the body diode, which can become significant for large heater powers or large area devices, the method has been used predominantly [13, 14, 17, 19]. To resolve this issue, the output resistance  $R_{\rm on}$  [15, 16] or the drain current  $I_{\rm D}$  [18] have been used to determine the temperature of the device interface.

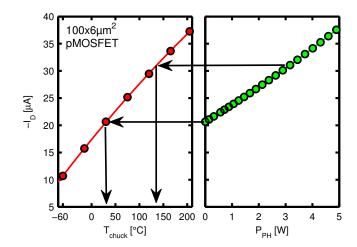

We also base our method for the determination of the device temperature on the temperature dependency of the drain current of the transistor. For this it is required to measure the transfer characteristics at several temperatures over the whole temperature range of the external heating system. From the transfer characteristics at different  $T_{\rm chuck}$  the drain current temperature dependency  $I_{\rm D}(T)$  can be extracted at an operating point  $(V_{\rm G}, V_{\rm D})$  different from the temperature compensation point [20]. This dependency  $I_{\rm D}(T)$  can be interpolated to map every change of the drain current with poly-heater power to an according device temperature change. This concept is explained in more detail in Fig. 1. Naturally, this method can only be used as long as the target temperature is within the range of the external heating system.

# B. Experimental issues

We remark that the thermal capacitances of the materials surrounding the device and the heater may require a wait time of up to approximately 10 s after a temperature switch for the whole setup to reach thermal equilibrium [18]. For the rather small steps of the sweep of the poly-heater power in Fig. 1, a

Figure 1. On the left hand side the temperature dependency of the drain current  $I_{\rm D}$  at a suitably chosen operating point  $(V_{\rm G},\,V_{\rm D})$  is depicted. This dependency allows to map the increase of the drain current with increasing poly-heater power supply (right) to an increase in temperature. The increase of the drain current is independent of the biasing polarity to the heater and fully reversible and repeatable.

wait time of roughly a second is sufficient for all investigated poly-heater technologies.

The increase of the drain current with heater power is independent of the actual current flow direction through the heater and fully reversible and repeatable. This proves that our electrical setup is such that the large currents (several 100 mA) and voltages (up to 40 V) needed for the heater power supply do not lead to voltage drops in the connection cables which may cause a ground shift. This indicates further that the parasitic electromagnetic fields which accompany the heater power supply do not alter the device performance. Another strong indication that the increase of the drain current when using the poly-heater is only due to a device temperature increase, can be given when using a strongly temperature dependent degradation mechanism like negative bias temperature instability (NBTI). To do so, we supplied the stress temperature either by the thermo chuck or by the poly-heater and measured the resulting degradation of a pMOSFET. We observed the same amount of degradation in both cases, which allows us to conclude that the poly-heater indeed increases and impacts only the device temperature [21].

Further, the placement of two polycrystalline silicon wires in the close vicinity of the device did not lead to any measurable differences in either the virgin characteristics or the degradation behavior of the device.

We remark that all the comments on potential experimental issues mentioned in this section apply only to the devices used and might not be transferable to other test structures, especially if they include a whole circuit of USLI technology.

# III. DEVICE TEMPERATURE EXTRAPOLATION

If the target device temperature is above the maximum temperature of the available external heat source, one would need to extrapolate  $I_{\rm D}(T)$  to extend the method described above. This extrapolation needs to be done with a TCAD device simulation with calibrated material parameters valid

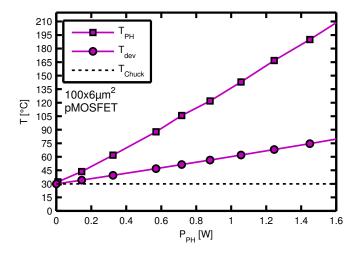

Figure 2. Change of the device and poly-heater temperature over power supply to the heater. The difference of the two temperatures is due to a vertical gradient of the temperature within the device stack, as can also be seen in the temperature distribution calculated with a three-dimensional electrothermal FEM simulation depicted in Fig. 6.

also in the high temperature regime. Such material parameters are rather difficult to characterize, especially when exceeding the point where the semiconductor becomes intrinsic [11, 19]. Furthermore, at such high temperatures already the low bias required to measure the temperature dependent drain current can lead to degradation of the device. To avoid those issues and to develop a method which has the potential to work up to arbitrary temperatures, we extrapolate the functional dependency of the device temperature instead of the drain current over power dissipated in the heater.

# A. Linear extrapolation

With increasing power supply to the poly-heater the differential electrical resistance of the poly-heater and the drain current of the transistor increase. Both changes are mapped to a poly-heater temperature  $T_{\mathrm{PH}}$  and a device temperature  $T_{\text{dev}}$ , respectively, cf. Fig. 2. The reason for the difference in the temperatures of the heater and the device are the finite thermal resistances of the materials between the heater wires and the device (mainly oxide, represented as  $R_{\text{FOX}}^{\text{th}}$ ) and between the device and the chuck (usually a semiconducting or insulating substrate, represented by  $R_{\mathrm{sub}}^{\mathrm{th}}$ ). Note that the thermal resistances also include the three-dimensional heat spreading in a phenomenological fashion. From the difference in the thermal conductivity of Si and SiO<sub>2</sub> (Si has  $\approx 100$  times lower  $R^{\rm th}$  than SiO<sub>2</sub>) and their thickness relation ( $\approx 200\,\mu{\rm m}$ Si to  $\approx 0.5\,\mu\mathrm{m}$  SiO<sub>2</sub>) one would expect that  $R_{\mathrm{FOX}}^{\mathrm{th}}$  is roughly four times smaller than  $R_{\rm sub}^{\rm th}$ . The measurement shows that it is the other way round, meaning that  $R_{FOX}^{th}$  is even larger than  $R_{

m sub}^{

m th}$ . This discrepancy is due to the completely different heat spreading in these two layers, as shown later with the help of the FEM simulation. If these thermal resistances were independent of temperature, the device temperature would depend linearly on  $P_{PH}$ . However, this is only true for small changes in temperature as the ones depicted in Fig. 2. The increase of the device temperature with power soon deviates from a linear

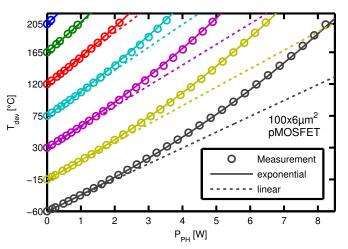

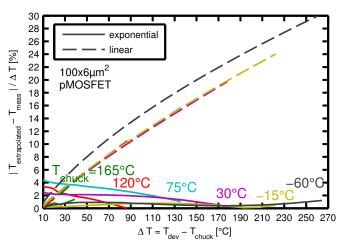

Figure 3. Device temperature  $T_{\rm dev}$  over poly-heater power supply  $P_{\rm PH}$  in the range of the thermo chuck between  $-60\,^{\circ}{\rm C}$  and  $205\,^{\circ}{\rm C}$ . A linear extrapolation from the first  $10\,^{\circ}{\rm C}$  change in device temperature would lead to serious errors for large powers. In comparison, the exponential extrapolation (5) can reproduce the rise in temperature more accurately.

relationship for larger temperature differences, as depicted in Fig. 3. From this follows that for larger temperature differences the temperature dependency of the thermal resistances have to be considered in order to accurately determine the device temperature.

### B. Exponential extrapolation

The electrical power  $P_{\rm PH}$  dissipated in the poly-heater is transformed through Joule heating to an equivalent amount of heat flow  $\dot{Q}$ . This heat flows mainly towards the chuck because at the top surface the heat may only transfer out of the solid through radiation or convection. Radiation from directly the die surface as well as adjacent areas for larger temperature switches is estimated by the Stefan–Boltzmann law to be negligibly small ( $\dot{Q} < 1\,\mathrm{mW}$  if  $T < 500\,^\circ\mathrm{C}$ ). Convection is estimated from Newton's law of cooling with a heat transfer coefficient of air at atmospheric pressure of about  $20\,\mathrm{Wm^{-2}K^{-1}}$  to  $30\,\mathrm{Wm^{-2}K^{-1}}$  to be on the order of some  $10\,\mathrm{mW}$  for the small area of a semiconductor test structure. As such, virtually all of the heat generated by the dissipated electrical power of up to  $10\,\mathrm{W}$  flows towards the chuck.

To measure the thermal resistance of the substrate  $R_{\rm sub}^{\rm th}(T_{\rm chuck})$  we record the relationship  $T_{\rm dev}(P_{\rm PH})$  at various different chuck temperatures. The thermal resistance is then given by

$$R_{\mathrm{sub}}^{\mathrm{th}}(T_{\mathrm{chuck}}) = \frac{T_{\mathrm{dev}}(P_{\mathrm{PH}}) - T_{\mathrm{chuck}}}{P_{\mathrm{PH}}} \text{ for } P_{\mathrm{PH}} \longrightarrow 0.$$

(1)

This value can be practically estimated by calculating the differential thermal resistance measured in a small power sweep of the poly-heater and taking the value at 0 W of a first order fit of the data in a small temperature range, e.g. 10 °C

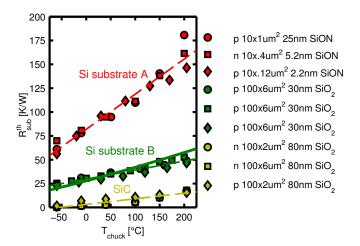

As depicted in Fig. 4, the change of the thermal resistance with temperature can reasonably well be approximated by the linear relationship

$$R_{\text{sub}}^{\text{th}}(T) = R_{\text{sub},0}^{\text{th}} \left( 1 + \alpha (T - T_0) \right)$$

(2)

Figure 4. Dependence of the effective thermal resistance  $R_{\rm sub}^{\rm th}$  on the chuck temperature. In the legend, n and p refer to n- or pMOSFET, respectively, the micro meter dimensions are the width times the length of the MOSFET,respectively, followed by the thickness and type of the gate oxide. The increase of the thermal resistance with temperature can be reasonably well approximated by linear functions for every technology (dashed lines). The thick solid line is the theoretical thermal resistance of silicon with  $\propto T^{1.324}$  after [22] for the area of the poly silicon wires and the actual substrate thickness.

with three constants  $R_{\mathrm{sub},0}^{\mathrm{th}}$ ,  $T_0$  and  $\alpha$ . The first parameter  $R_{\mathrm{sub},0}^{\mathrm{th}}=R_{\mathrm{sub}}^{\mathrm{th}}(T_0)$  is thereby not only due to the substrate material but includes also a temperature independent thermal resistance of the interface between the wafer and the chuck or the materials between the diced device and the heat sink of the package. If suitable test structures were available, we measured the thermal resistance on nMOSFETs or pMOSFETs, also for different device oxide thicknesses in the range of 2.2 nm to 30 nm. We observe that  $R_{\mathrm{sub}}^{\mathrm{th}}$  depends mostly on the type and thickness of the substrate material.

The thermal resistance is defined through the change of the temperature T with heat flow  $\dot{Q}$ . For Joule heating,  $\dot{Q}$  is equivalent with the dissipated electrical power P. We can therefore deduce

$$R^{\text{th}} = \frac{\mathrm{d}\,T}{\mathrm{d}\,\dot{Q}} \equiv \frac{\mathrm{d}\,T}{\mathrm{d}\,P} = T'(P),$$

(3)

which we have to base on the differential thermal resistance rather than the more commonly used absolute thermal resistance. With the assumption that the change of the thermal resistance with temperature can be approximated by a linear relationship we find the ordinary first order differential equation

$$T'(P) = R_{\text{sub }0}^{\text{th}} \left(1 + \alpha \left(T(P) - T_0\right)\right),$$

(4)

With the condition that T must equal the chuck temperature  $T_{\rm chuck}$  when there is no heater power applied we obtain the solution

$$T(P) = T_0 - \frac{1}{\alpha} + \left(\frac{1}{\alpha} + T_{\text{chuck}} - T_0\right) \exp\left(\alpha R_{\text{sub},0}^{\text{th}} P\right)$$

(5)

or, if  $\alpha = 0$

$$T(P) = T_{\text{chuck}} + R_{\text{sub 0}}^{\text{th}} \times P. \tag{6}$$

Figure 5. Comparison of the relative error of the linear and exponential extrapolation method from the first  $10\,^{\circ}\mathrm{C}$  temperature rise of the data of Fig. 3. The relative error increases with the temperature difference between the device and the chuck when taking the thermal resistances to be independent of the temperature ("linear"). When we consider a change of the thermal resistance of the substrate by using (5), the relative error stays below a few percent ("exponential").

This means that the temperature of the device rises exponentially with heater power. If there were no temperature dependency of  $R_{\rm sub}^{\rm th}$  ( $\alpha=0$ ) then  $T_{\rm dev}(P_{\rm PH})$  would be linear. The method therefore includes the conventional approach to extrapolate  $T_{\rm dev}(P_{\rm PH})$  linearly.

# C. Calibrated exponential extrapolation

The combination of (1), (2) and (5) is our main result: by small power sweeps at various chuck temperatures we measure  $R_{\rm sub}^{\rm th}(T_{\rm chuck})$  using (1) and then approximate the relationship of this curve by the linear regression (2). The device temperature is then estimated from (5) without any further fitting procedure. Thus, instead of estimating a  $T_{\rm dev}(P_{\rm PH})$  relation for every device and chuck temperature, which cannot be substantially supported by measured data points at the upper end of the thermo-chuck temperature range, we rather search for the  $R_{\rm sub}^{\rm th}(T_{\rm chuck})$  relation (2) which is much more robust in its linearity and readily measured on a large temperature range with corresponding high regression quality. As such, the  $T_{\rm dev}$  extrapolation method is calibrated by the linear  $R_{\rm sub}^{\rm th}$  measurement

The correctness of the exponential extrapolation method is verified within the chuck temperature range  $-60\,^{\circ}\text{C}$  to  $205\,^{\circ}\text{C}$  through a comparison with experimental data, see Fig. 5. The relative error of this method is smaller than a few percent for the whole temperature range of the thermo chuck. This justifies the use of the exponential formula (5) within the range of the thermo chuck.

For temperatures outside the calibration temperature range, the method thus allows for a straightforward calculation of the device temperature. However, this extrapolation relies on the linear temperature dependency of  $R_{\rm sub}^{\rm th}(T_{\rm chuck})$ , which cannot be directly validated above a certain maximum temperature. When extrapolating using (5), it is implicitly assumed due to (2) that the temperature dependency of the thermal resis-

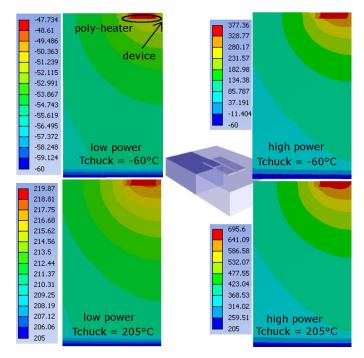

Figure 6. We performed a three-dimensional Ansys® electrothermal simulation of the lateral poly-heater structure. The symmetry of the geometry allowed to simulate only a fourth of the heater structure (see sketch in the middle). Depicted are four temperature distributions in a vertical cut in the center of the half poly-heater. Only the nearby region around the heater wires of the full model is shown, which itself extends far towards the left to account for the large heat distribution in the semiconductor. Different chuck temperatures or heater power supplies cause roughly the same temperature distribution.

tance does not deviate from its linear relationship at temperatures above  $205\,^{\circ}\mathrm{C}$ . This assumption is rather safe considering that the theoretical temperature dependency of the thermal resistance for semiconductors is  $\propto T^{\gamma}$  between  $\approx 100\,\mathrm{K}$  and the melting or sublimation point [22–24]. For example, in silicon  $\gamma=1.324$ , and  $T^{\gamma}$  can be approximated with good accuracy by a linear relationship between  $-60\,^{\circ}\mathrm{C}$  and  $205\,^{\circ}\mathrm{C}$ . With this approximation the relative error is only  $9\,\%$  at  $500\,^{\circ}\mathrm{C}$  (see thick line in Fig. 4). The differential equation (4) which leads to (5) can also be solved for values of  $\gamma\neq 1$  which, however, makes (5) less compact and does not considerably increase the accuracy of the extrapolation.

The validity of our assumption that the thermal resistance of the whole volume underneath the device is due to the temperature of the device  $T_{\text{dev}}$  is not quite obvious. Although the substrate temperature is highly inhomogeneous from top (device) to bottom (chuck), we still observe convincing agreement between the estimated and measured device temperature with  $R^{\text{th}}(T_{\text{dev}})$ . This is because the effective thermal resistance of the substrate is determined by a small increase of the device temperature ( $\approx 10$  °C) with poly-heater power. As confirmed in the next section via numerical simulation, see Fig. 6, this small temperature difference induces approximately the same relative temperature distribution within the stack as a large temperature difference. The temperature is the highest in the region close to the device. Since the thermal resistance rises with increasing temperature a bottleneck forms which mainly impacts the thermal resistance of the substrate. This bottleneck

influences consequently also the rise of the device temperature during poly-heater use. Since we use the same  $R^{\rm th}(T_{\rm dev})$  values in both cases we consistently estimate the device temperature when using the poly-heater.

### IV. FINITE-ELEMENT-METHOD SIMULATION

In order to further verify the extrapolation method (5) we have performed finite element method (FEM) simulations using Ansys<sup>®</sup>. A first approach with a two dimensional (2D) thermal simulation did not lead to satisfactory results. We needed to arbitrarily change the thermal conductivity material data of silicon in order to obtain reasonable qualitative agreement between simulation and measurement [14]. The main shortcoming of the 2D simulation approach was that the polyheater is represented as a quasi-infinitely long device and that the influence of the electrical parameters on the temperature distribution are ignored. This is consistent with literature results [14] and confirms the 3D nature of our problem. We have therefore extended the simulation to a 3D electrothermal simulation, where we obtain a satisfying agreement.

### A. Three dimensional electrothermal simulation

The simulation geometry is sketched in Fig. 6. The numerical simulation calculates the current flow through the heater wires and converts the dissipated electrical power to a corresponding heat. The temperature dependent electrical material data of the polycrystalline silicon have been acquired from polycrystalline test structures on the same wafer. We use Neumann boundary conditions (adiabatic boundary conditions, no heat flow) at all borders of the model except for the bottom surface. There we have introduced a 20 µm thick layer with a temperature independent thermal conductivity of  $0.5\,\mathrm{W}\,\mathrm{m}^{-1}\,\mathrm{K}^{-1}$  to emulate the thermal resistance between the wafer and the chuck. The bottom surface of this layer has Dirichlet boundary conditions and is set to the chuck temperature. The value for the thermal resistance of the wafer to chuck interface is consistent with previous reports [25, 26]. The thermal conductivity of the silicon substrate has been determined in a reference measurement on an unprocessed raw wafer to be significantly lower than standard silicon [22, 23] because of a high doping level [24, 27]. Also for the numerical simulation we have reduced the power law coefficient of the temperature dependency of the thermal resistance of silicon to  $\gamma = 1$  because our experimental data suggests such a dependency on the temperature (c.f. Fig. 4) and a variation of  $\gamma$  between 0.6 and 1.2 in our simulation did not improve the accuracy of the model.

The simulation model includes the exact dimensions of the silicon, the poly silicon and the intermediate oxide layers but misses the surrounding pads and other devices in the vicinity. This is justified because we found the cooling impact of a 20 µm thick metal plate close to the heater to be very small in a cross-check simulation. The area of the substrate material in the simulation had to be increased to 4 mm×4 mm, to cover the large spread of the temperature distribution, visible in a small increase of the temperature at the lateral outside borders of the substrate block. The device temperature was estimated by

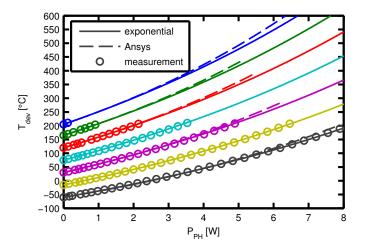

Figure 7. Extrapolation of the device temperature over heater power obtained from a three-dimensional electrothermal Ansys simulation. Also shown is the exponential function (5). Both methods reproduce the measurement data reasonably well and give equivalent extrapolations to the high temperature regime  $> 300\,^{\circ}\text{C}$ .

averaging the few degree Celsius temperature variation along the plane at the  $\mathrm{Si}\text{-}\mathrm{SiO}_2$  interface at the exact position of the device. As depicted in Fig. 7, both the exponential model (5) as well as the 3D electrothermal simulation can reproduce the measurement data very well. The simulation predicts a few percent higher temperature than the measurement data and the exponential extrapolation method. This is presumably a consequence of the neglect of cooling parts, such as the surrounding pads or devices, or the reduction of the substrate area to  $4\,\mathrm{mm}\times4\,\mathrm{mm}$  instead of the whole wafer diameter of 200 mm.

Of particular interest is the extrapolation of the device temperature of both methods to larger powers. There, the two methods follow different assumptions to calculate temperatures beyond  $205\,^{\circ}\text{C}$ . The Ansys® simulation solves the heat equation with position and temperature dependent thermal conductivity values which largely represents the "real" situation. The exponential method (5) reduces the complexity by a 1D approximation and uses mainly the assumption that the change of the thermal resistance with temperature will not loose its linear dependency at temperatures  $> 205\,^{\circ}\text{C}$ . Since both methods give very similar results we conclude that the exponential extrapolation method (5) is a valid reduction of the complexity of the problem and may efficiently be used to extrapolate to high device temperatures.

# V. APPLICATIONS

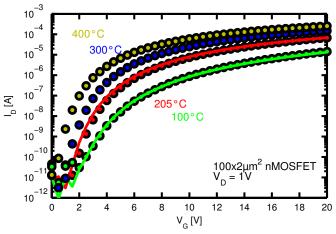

As a particular example, we demonstrate the use of the polyheater to effortlessly test and operate wide band gap devices at high temperatures. In Fig. 8 transfer characteristics of a SiC nMOSFET up to 400 °C are depicted. Measuring at these high temperatures usually involves a significant experimental effort [11]. With the poly-heater, characterization at these high temperatures can be achieved with standard semiconductor parameter analyzers without additional equipment [19]. The maximum achievable device temperature is only given by the

Figure 8. The poly-heater allows for effortless characterization of devices at temperatures beyond conventional chuck systems. To demonstrate this, we recorded the transfer characteristics of a silicon carbide nMOSFET at high temperatures using either the thermo chuck (lines) or the polyheater (symbols). For the poly-heater measurements the wafer was thermally decoupled from the chuck and 4.77 W, 9.67 W, 13.0 W and 15.9 W were applied to the poly-heater to elevate the device temperature to  $100\,^{\circ}\text{C}$ ,  $205\,^{\circ}\text{C}$ ,  $300\,^{\circ}\text{C}$  and  $400\,^{\circ}\text{C}$ , respectively.

power source and the breakdown electric field of the oxide between the polycrystalline silicon wires and the semiconductor. The maximum device temperature can therefore be in principal increased to values much above  $400\,^{\circ}\mathrm{C}$ .

In addition, poly-heaters open a range of new possibilities for device reliability and characterization. For example, it has recently been shown that negative bias temperature stress and recovery can be accelerated at higher temperatures [2]. However, the maximum temperature a fully processed device can sustain in an oven is fairly limited. The poly-heater, in contrast, creates the heat much closer to the dielectric layer and allows therefore to achieve much higher temperatures, which gives two major possibilities. First, as it is known that complete recovery through temperature treatment is possible [28, 29], the poly-heater allows one to recover from previous damage in a minimum amount of time. This idea has already been exploited to increase the lifetime of flash memory cells [30], by heating the word lines of the memory cells. Second [2], by accelerating the degradation with temperature, considerably improved lifetime estimations as well as the determination of the maximum drift of a device are possible.

Finally, because the poly-heater is a rather simple structure having temperature sensors within the semiconductor, it can also be used to determine thermal material data by matching it with a consistent simulation. Even thermal capacitances can be determined when investigating abrupt temperature switches as the ones documented in e.g. [18].

# VI. CONCLUSIONS

We have presented a simple method to extend the temperature range of local poly-heater structures. The method conveniently yields the power supply needed to increase the temperature of the device to a desired target temperature. It is based on an exponential function of the electrical power REFERENCES 7

which is a direct consequence of temperature dependent thermal resistances of the semiconductor materials. We have compared the accuracy of the method within the accessible chuck temperature range with experimental data and FEM simulations. For temperatures higher than the maximum chuck temperature we compared the extrapolation of our model with a 3D electrothermal simulation. All mentioned comparisons show vanishingly small discrepancies, making the poly-heater a powerful tool for research and development as well as for reliability testing. A particular advantage of our method is given by the fact that the calibration procedure of the polyheater has to be performed only once for each technology rather than for every single device under test.

### ACKNOWLEDGMENT

The authors would like to thank Thomas Aichinger, Dethard Peters and Tom Ostermann (all Infineon Technologies AG) for various inspiring discussions and their kind support.

This work was jointly funded by the Austrian Research Promotion Agency (FFG, Project No. 831163) and the Carinthian Economic Promotion Fund (KWF, contract KWF-1521|22741|34186).

### REFERENCES

- [1] D. K. Schroder, "Negative bias temperature instability: What do we understand?", *Microelectronics Reliability*, vol. 47, pp. 841–852, 2007.

- [2] G. Pobegen, T. Aichinger, M. Nelhiebel, and T. Grasser, "Understanding temperature acceleration for NBTI", in *IEEE International Electron Device Meeting*, Dec. 2011, pp. 27.3.1–27.3.4.

- [3] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P.-J. Wagner, F. Schanovsky, J. Franco, M. Toledano Luque, and M. Nelhiebel, "The paradigm shift in understanding the bias temperature instability: From reaction—diffusion to switching oxide traps", *IEEE Transactions on Electron Devices*, vol. 58, no. 11, pp. 3652–3666, Nov. 2011.

- [4] M. Toledano-Luque, B. Kaczer, P. Roussel, M. J. Cho, T. Grasser, and G. Groeseneken, "Temperature dependence of the emission and capture times of SiON individual traps after positive bias temperature stress", *Journal of Vacuum Science and Technology B*, vol. 29, no. 1, 01AA04, Jan. 2011.

- [5] M. J. Kirton and M. J. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise", *Advances in Physics*, vol. 38, no. 4, pp. 367–468, 1989.

- [6] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities", *Microelectronics Reliability*, vol. 52, no. 1, pp. 39–70, 2012.

- [7] C. Guerin, V. Huard, and A. Bravaix, "General framework about defect creation at the Si/SiO2 interface", *Journal of Applied Physics*, vol. 105, no. 11, 114513, p. 114513, 2009.

- [8] S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. Park, H. Enichlmair, M. Karner, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, "Interface traps density-of-states as a vital component for hot-carrier degradation modeling", *Microelectronics Reliability*, no. 50, pp. 1267–1272, 2010.

- [9] E. Wu, J. Sune, W. Lai, E. Nowak, J. McKenna, A. Vayshenker, and D. Harmon, "Interplay of voltage and temperature acceleration of oxide breakdown for ultrathin gate oxides", *Solid-State Electronics*, vol. 46, no. 11, pp. 1787–1798, 2002.

- [10] J. McPherson, "Time dependent dielectric breakdown physics Models revisited", *Microelectronics Reliability*, vol. 52, no. 9-10, pp. 1753–1760, 2012.

- [11] P. Borthen and G. Wachutka, "Testing semiconductor devices at extremely high operating temperatures", *Microelectronics Reliability*, vol. 48, no. 8-9, pp. 1440–1443, 2008.

- [12] C. Messick and T. Turner, "A generic test structure heater design and characterization", in *International Wafer Level Reliability Workshop*, Oct. 1992, pp. 83–87.

- [13] W. Muth, A. Martin, J. von Hagen, D. Smeets, and J. Fazekas, "Polysilicon resistive heated scribe lane test structure for productive wafer level reliability monitoring of NBTI", in *International Conference on Microelectronic Test Structures*, Mar. 2003, pp. 155–160.

- [14] W. Muth and W. Walter, "Bias temperature instability assessment of n- and p-channel MOS transistors using a polysilicon resistive heated scribe lane test structure", *Microelectronics Reliability*, vol. 44, no. 8, pp. 1251–1262, 2004.

- [15] C.-S. Wang, W.-C. Chang, W.-S. Ke, and K.-C. Su, "Ultra-fast negative bias temperature instability monitoring and end-of-life projection", in *IEEE International Integrated Reliability Workshop*, Sep. 2006, pp. 136– 138.

- [16] T.-K. Kang, C.-S. Wang, and K.-C. Su, "Self-heating p-channel metal-oxide-semiconductor field-effect transistors for reliability monitoring of negative-bias temperature instability", *Japanese Journal of Applied Physics*, vol. 46, no. 12, pp. 7639–7642, 2007.

- [17] C. Schluender, R.-P. Vollertsen, W. Gustin, and H. Reisinger, "A reliable and accurate approach to assess NBTI behavior of state-of-the-art pMOSFETs with fast-WLR", in *European Solid State Device Research Conference*, Sep. 2007, pp. 131–134.

- [18] T. Aichinger, M. Nelhiebel, S. Einspieler, and T. Grasser, "In situ polyheater A reliable tool for performing fast and defined temperature switches on chip", IEEE Transactions on Device and Materials Reliability, vol. 10, pp. 3–8, Mar. 2010.

- [19] C. Boianceanu, D. I. Simon, D. Costachescu, and M. Pfost, "Design and operation of an integrated high-temperature measurement structure", *IEEE Transactions on Semiconductor Manufacturing*, vol. 25, no. 4, pp. 542 –548, 2012.

- [20] P. Spirito, G. Breglio, V. d'Alessandro, and N. Rinaldi, "Thermal instabilities in high current power MOS devices: experimental evidence, electro-thermal simulations and analytical modeling", in *International Conference on Microelectronics*, IEEE, vol. 1, 2002, pp. 23–30.

- [21] G. Pobegen and T. Grasser, "On the distribution of NBTI time constants on a long, temperature accelerated time scale", *IEEE Transactions on Electron Devices*, submitted.

- [22] P. Leturcq, J.-M. Dorkel, A. Napieralski, and E. Lachiver, "A new approach to thermal analysis of power devices", *IEEE Transactions on Electron Devices*, vol. 34, no. 5, pp. 1147–1156, May 1987.

- [23] C. J. Glassbrenner and G. A. Slack, "Thermal conductivity of silicon and germanium from 3K to the melting point", *Physical Review*, vol. 134, no. 4A, A1058–A1069, 1964.

- [24] G. A. Slack, "Thermal conductivity of pure and impure silicon, silicon carbide, and diamond", *Journal of Applied Physics*, vol. 35, no. 12, pp. 3460–3466, 1964.

- [25] H. Ibele and K. Reitinger, "Optimum wafer to thermal chuck interface", in *IEEE Semiconductor Wafer Test Workshop*, 2005.

- [26] A. Cardoso and A. K. Srivastava, "Improvements in wafer temperature measurements", *Journal of Vacuum Science and Technology B*, vol. 19, no. 2, pp. 397–402, 2001.

- [27] W. Liu and M. Asheghi, "Thermal conduction in ultrathin pure and doped single-crystal silicon layers at high temperatures", *Journal of Applied Physics*, vol. 98, no. 12, 123523, p. 123523, 2005.

- [28] A. A. Katsetos, "Negative bias temperature instability (NBTI) recovery with bake", *Microelectronics Reliability*, vol. 48, pp. 1655–1659, Oct. 2008.

- [29] C. Benard, J.-L. Ogier, and D. Goguenheim, "Total recovery of defects generated by negative bias temperature instability (NBTI)", in *IEEE International Integrated Reliability Workshop*, 2008, pp. 7–11.

- [30] H.-T. Lue, P.-Y. Du, C.-P. Chen, W.-C. Chen, C.-C. Hsieh, Y.-H. Hsiao, Y.-H. Shih, and C.-Y. Lu, "Radically extending the cycling endurance of flash memory (to greater than 100M cycles) by using built-in thermal annealing to self-heal the stress-induced damage", in *IEEE International Electron Device Meeting*, 2012, pp. 9.1.1 –9.1.4.

Gregor Pobegen was born in Klagenfurt, Austria in 1984. He received the Dipl.-Ing. degree in technical physics from the Graz University of Technology, Graz, Austria, in 2010. He is currently working toward the Ph.D. degree at the Kompetenzzentrum für Automobil- und Industrieelektronik GmbH (KAI), Villach, Austria, and at the Institute for Microelectronics, Vienna University of Technology, Vienna, Austria. His current research interests include the reliability of silicon or silicon carbide based power MOSFETs.

Michael Nelhiebel received his M.Sc. and Ph.D. degrees in physics from Vienna University of Technology and Ecole Centrale Paris, respectively. In 1999 he joined Infineon Technologies Austria. As a principal engineer, he currently focuses on reliability research at the Infineon-held competence center KAI, from MOS interface defects to thermomechanical degradation of power devices.

**Stefano de Filippis** received his Bachelor degree from the faculty of electronic engineering of Università degli Studi di Napoli "Federico II", Naples, Italy, in 2005.

In 2008, he joined the Kompetenzzentrum Automobil- und Industrieelektronik GmbH (KAI), where he worked on the experimental evaluation of the thermal behavior of both discrete power MOSFETs and Smart Power switches for automotive applications. Through 2009 and 2010 he worked on the development of methodologies for infrared

thermographic measurements of power switches. In 2009 he received his Master degree in electronic engineering from Università degli Studi di Napoli "Federico II".

Since 2010, he is working on the development of thermal and electrothermal finite element simulation methods for automotive power switches together with KAI, Infineon Technologies Austria and the department of electronic engineering (Dipartimento di Ingegneria Biomedica, Elettronica e delle Telecomunicazioni) of Università degli Studi di Napoli "Federico II". His current interest focuses on the study of thermally stable versus unstable operating conditions and on the assessment of their impact on device robustness and reliability characteristics. His main research activities include electro-thermal modeling of power MOSFETs, their experimental characterization and the development of suitable simulation algorithms. In April 2013, he obtained the Ph.D. degree in electronic engineering from Università degli Studi di Napoli "Federico II".

**Tibor Grasser** received his Ph.D. degree in technical sciences from the Vienna University of Technology where he is currently employed as an Associate Professor. In 2003 he was appointed director of the Christian Doppler Laboratory for TCAD in Microelectronics. Dr. Grasser is the co-author or author of more than 400 scientific articles, editor of a book on advanced device simulation, a distinguished lecturer of the IEEE Electron Devices Society, a senior member of IEEE, has been involved in various functions of outstanding conferences such as IEDM,

IRPS, SISPAD, IWCE, ESSDERC, IIRW, and ISDRS, is a recipient of the Best Paper Awards at IRPS (2008, 2010, and 2012), ESREF (2008) and the IEEE EDS Paul Rappaport Award (2011). He was also a chairman of SISPAD 2007 and is currently TPC chair of IIRW 2013.