# Impact of hot carrier degradation and positive bias temperature stress on lateral 4H-SiC nMOSFETs

Gregor Pobegen<sup>1,a</sup>, Thomas Aichinger<sup>2,b</sup>, Alberto Salinaro<sup>3,c</sup>, and Tibor Grasser<sup>4,d</sup>

<sup>1</sup>KAI GmbH, Europastraße 8, 9500 Villach, Austria

<sup>2</sup>Infineon Technologies Austria AG, Siemensstraße 2, 9500 Villach, Austria

<sup>3</sup>Infineon Technologies AG, Schottkystraße 10, 91058 Erlangen, Germany

<sup>4</sup>Institute for Microelectronics, TU Vienna, Gusshausstraße 27-29, 1040 Vienna, Austria

<sup>a</sup>gregor.pobegen@k-ai.at, <sup>b</sup>thomas.aichinger@infineon.com, <sup>c</sup>alberto.salinaro@infineon.com, <sup>d</sup>grasser@iue.tuwien.ac.at

**Keywords:** 4H-SiC, SiC-MOSFET, reliability, defects, traps, capture/emission time constants, bias temperature stress, hot carrier degradation

**Abstract.** We study the impact of positive bias temperature stress (PBTS) and hot carrier stress (HCS) on lateral 4H-SiC nMOSFETs. These degradation mechanisms are prominent in silicon (Si) based devices where both create oxide (OT) as well as interface traps (IT) [1, 2]. For SiC MOSFETs only limited information regarding these mechanisms is available [3–5]. We transfer the charge pumping (CP) technique, known from Si MOSFETs, reliably to SiC MOSFETs to learn about the nature of the stress induced defects.

## **Details of the experiment:**

The measurements were performed on dedicated lateral nMOSFET test structures on 4H-SiC with an 80nm thick NO-annealed deposited oxide with  $100\mu m$  channel width and  $2\mu m$  length. We analyze interface traps with CP [6] because this technique allows to resolve very low trap densities compared to capacitance or conductance methods (in Si down to  $\approx 10^9 cm^{-2} eV^{-1}$ ). We do not observe a geometric component which recently questioned the applicability of CP for SiC MOSFETs [7]. Further, CP can be applied to SiC MOSFETs directly, alleviating the problem of having to draw conclusions from capacitance-voltage measurements obtained on large area MOS capacitors.

CP is performed by repeatedly switching ( $f=100 {\rm kHz}$ ) the gate voltage between full inversion ( $V_{\rm G}=25 {\rm V}$ ) and full accumulation ( $V_{\rm G}=-25 {\rm V}$ ). The rising and falling slopes are  $13.33 {\rm V}/\mu {\rm s}$ . The resulting CP current ( $I_{\rm CP}$ ) between the source/drain and the bulk is proportional to the mean density of interface traps ( $D_{\rm IT}$ ) in an energy range ( $2.9\pm0.1$ )eV symmetrically around mid-gap (at room temperature). This energy range is calculated [6] by

$$\Delta E_{\rm CP} = 2k_{\rm B}T \ln \left( \frac{\Delta V_{\rm G}}{v_{\rm th}\sigma n_{\rm i}(V_{\rm TH} - V_{\rm FB})\sqrt{t_{\rm r}t_{\rm f}}} \right),\tag{1}$$

where  $k_{\rm B}T$  is the Boltzmann constant times the temperature and  $\Delta V_G/(V_{\rm TH}-V_{\rm FB})=50{\rm V}/6.5{\rm V}$  is the ratio between the pulse amplitude and the difference between the threshold and the flat-band voltage. The remaining parameters depend on the type of semiconductor and are not unambiguously determined for 4H-SiC. However, we defined a range of possible values and calculated the propagating maximum error for the CP energy range and the  $D_{\rm IT}$ . The used values are  $v_{\rm th}=(0.75\dots2)\times10^7{\rm cm/s}$  for the thermal drift velocity [8],  $\sigma=\sqrt{\sigma_n\sigma_p}=(10^{-18}\dots10^{-16}){\rm cm}^2$  for the geometric mean of the electron and hole capture cross-section of the interface traps, respectively [9] and  $n_{\rm i}=(0.5\dots1)\times10^{-8}{\rm cm}^{-3}$  for the intrinsic carrier density [10].

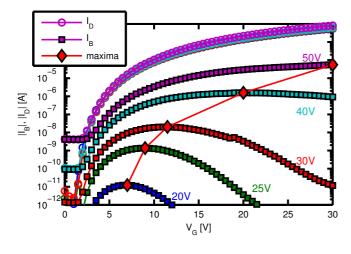

Fig. 1: Bulk  $I_{\rm B}$  and drain  $I_{\rm D}$  current as a function of gate voltage  $V_{\rm G}$  for several high drain voltages  $V_{\rm D}$ . The substrate current peak increases and shifts towards larger  $V_{\rm G}$  values with increasing  $V_{\rm D}$ . We observed a destructive breakdown for  $V_{\rm D}=60{\rm V}$ .

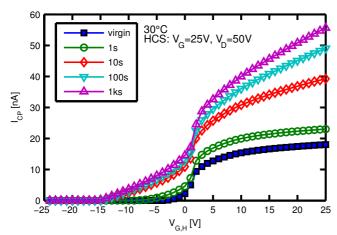

Fig. 2: Constant base level CP measurement before and after HCS. A large increase in the number of interface traps is observed.

### **Hot carrier degradation:**

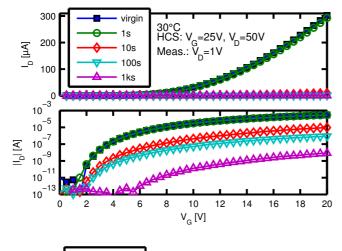

To test whether hot carriers can be created in the channel of the device under test, we measure the bulk current as a function of the  $V_{\rm G}$  for high drain bias, as depicted in Fig. 1. We indeed observe a bulk current because the electrons accelerated from the source gain sufficient kinetic energy such that they cause impact ionization at the interface region near the drain junction [2]. This impact ionization creates electron-hole pairs which are separated by the space charge region of the reverse biased drain-bulk pn-junction and may cause interface degradation. The mechanism is most efficient (peak in  $I_{\rm B}$ ) for large drain bias and  $V_{\rm G}\approx 1/\alpha\times V_{\rm D}$  with  $\alpha=2$ –3, as expected for long channel devices of Si technology [2]. As depicted in Fig. 2, the CP current increases considerably due to HCS. In terms of  $D_{\rm IT}$ : from  $(1.9\pm0.1)\times10^{11}{\rm cm}^{-2}{\rm eV}^{-1}$  to  $(6.0\pm0.4)\times10^{11}{\rm cm}^{-2}{\rm eV}^{-1}$  after 1ks stress. These newly created IT decrease the drain current of the device as visible in the transfer characteristic, see Fig. 3. The induced threshold voltage shift depends strongly on the readout bias.

# Positive bias temperature stress:

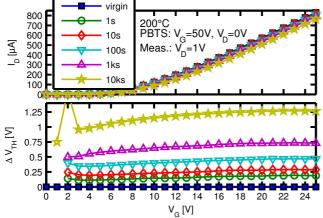

To study the impact of BTS on 4H-SiC nMOSFETs, we subjected a device to  $V_{\rm G}=50{\rm V}~(\approx 6{\rm MV/cm})$ ,  $V_{\rm D}=0{\rm V}$  at 200°C chuck temperature to accelerate the degradation. The transfer characteristic of the device is shifted parallel along the voltage axis towards larger  $V_{\rm G}$  values as depicted in Fig. 4. This indicates the creation of  $1.9\times10^{11}{\rm cm}^{-2}$  OT after 1ks stress when assuming the charges at the SiC-SiO<sub>2</sub> interface. The readout bias independence indicates that the defects created through PBTS are located within the SiO<sub>2</sub> and cannot exchange charge with the carriers in the channel during the transfer characteristic measurement. I.e. charge exchange with these defects occurs only on larger timescales.

Fig. 3: Transfer characteristics after HCS in linear and logarithmic scale. The stress decreases the drain current of the device largely.

Fig. 4: Change of the transfer characteristic (upper plot) with increasing PBTS time. The  $V_{\rm TH}$  shift occurs parallel along the voltage axis, as also visible when plotting the horizontal difference between the characteristics (lower plot).

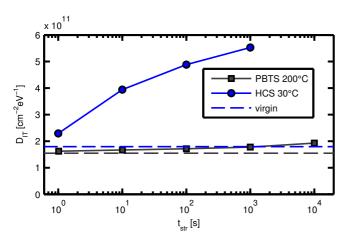

In accordance, the CP current stays almost constant with increasing stress time [5] if compared to HCS (c.f. Fig. 5).

#### **Discussion:**

In the degradation after HCS and PBTS we distinguish between OT and IT by analyzing the transfer characteristics and the CP current of dedicated test structures. We find that only the high energetic carriers during HCS can cause interface degradation measurable with CP. PBTS causes the creation of gate bias independent negative oxide charges consistent with results for negative BTS [5]. We explain our results by assuming that IT at the SiC-SiO<sub>2</sub> interface are passivated by nitrogen atoms [11] which are strongly bonded to the interfacial Si or C atoms [12] and are therefore only dissociated by the high

Fig. 5: Change of the density of interface traps measured with CP over stress time for HCS and PBTS. The smaller CP energy range at 200°C for PBTS compared to 30°C [6] for HCS was considered by calculating the energy range with (1). The remaining difference in the virgin  $I_{\rm CP}$  is due to device-to-device variations.

energetic carriers existent during HCS. In contrast, PBTS causes a degradation because of field and temperature dependent bond dissociation [1, 13] of precursor defects within the SiO<sub>2</sub> layer.

# Acknowledgment

This work was jointly funded by the Austrian Research Promotion Agency (FFG, Project No. 831163) and the Carinthian Economic Promotion Fund (KWF, contract KWF-1521|22741|34186). The authors would like to thank Dethard Peters (Infineon Technologies AG) and Gernot Gruber (KAI GmbH) for their kind guidance and support.

### References

- [1] T. Grasser, B. Kaczer, W. Goes, H. Reisinger, T. Aichinger, P. Hehenberger, P.-J. Wagner, F. Schanovsky, J. Franco, M. Toledano Luque, and M. Nelhiebel, "The paradigm shift in understanding the bias temperature instability: From reaction--diffusion to switching oxide traps," *IEEE Transactions on Electron Devices*, vol. 58, no. 11, pp. 3652–3666, Nov. 2011.

- [2] A. Bravaix and V. Huard, "Hot-carrier degradation issues in CMOS nodes," in *European Symposium on Reliability of Electron Devices, Failure Physics and Analysis*, Oct. 2010, tutorial.

- [3] E. Bano, C. Banc, T. Ouisse, and S. Scharnholz, "Hot carrier-induced photon emission in 6H and 4H-SiC MOSFETs," *Solid-State Electronics*, vol. 44, no. 1, pp. 63–69, 2000.

- [4] A. Lelis, D. Habersat, R. Green, A. Ogunniyi, M. Gurfinkel, J. Suehle, and N. Goldsman, ``Time dependence of bias-stress-induced SiC MOSFET threshold-voltage instability measurements," *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 1835–1840, Aug. 2008.

- [5] T. Aichinger, P. M. Lenahan, and D. Peters, "Interface defects and negative bias temperature instabilities in 4H-SiC pMOSFETs -- a combined DCIV/SDR study," *Materials Science Forum*, vol. 740-742, pp. 526–532, 2013.

- [6] G. Groeseneken, H. Maes, N. Beltran, and R. De Keersmaecker, "A reliable approach to charge-pumping measurements in MOS transistors," *IEEE Transactions on Electron Devices*, vol. 31, no. 1, pp. 42–53, 1984.

- [7] D. Okamoto, H. Yano, T. Hatayama, Y. Uraoka, and T. Fuyuki, ``Analysis of anomalous charge-pumping characteristics on 4H-SiC MOSFETs," *IEEE Transactions on Electron Devices*, vol. 55, no. 8, pp. 2013–2020, Aug. 2008.

- [8] K. Vassilevski, K. Zekentes, A. Zorenko, and L. Romanov, "Experimental determination of electron drift velocity in 4H-SiC p+/n/n+ avalanche diodes," *IEEE Electron Device Letters*, vol. 21, no. 10, pp. 485–487, 2000.

- [9] T. Rudenko, I. Osiyuk, I. Tyagulski, H. Ólafsson, and E. Sveinbjörnsson, ``Interface trap properties of thermally oxidized n-type 4H-SiC and 6H-SiC," *Solid-State Electronics*, vol. 49, no. 4, pp. 545–553, 2005.

- [10] P. Friedrichs, E. P. Burte, and R. Schörner, "Interface properties of metal-oxide-semiconductor structures on n-type 6H and 4H-SiC," *Journal of Applied Physics*, vol. 79, no. 10, pp. 7814–7819, 1996.

- [11] K. McDonald, R. Weller, S. Pantelides, L. Feldman, G. Chung, C. C Tin, and J. Williams, "Characterization and modeling of the nitrogen passivation of interface traps in SiO2/4H-SiC," *Journal of Applied Physics*, vol. 93, no. 5, pp. 2719–2722, 2003.

- [12] C. Naulin, M. Costes, Z. Moudden, N. Ghanem, and G. Dorthe, `The dissociation energy of the SiN radical determined from a crossed molecular beam study of the Si+N2O->SiN+NO reaction," *Chemical Physics Letters*, vol. 202, no. 5, pp. 452–458, 1993.

- [13] V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling," *Microelectronics Reliability*, vol. 46, no. 1, pp. 1–23, 2006.