# **Characterization and Modeling of Reliability Issues in Nanoscale Devices**

G. Rzepa\*, W. Goes\*, B. Kaczer<sup>†</sup>, and T. Grasser\*

\*Institute for Microelectronics, TU Wien, Vienna, Austria

<sup>†</sup>imec, Leuven, Belgium

Abstract—Detailed investigations of charge trapping mechanisms have revealed a very specific picture of defects in the oxide of MOSFETs. Important features of these defects, such as the existence of metastable states, were indicated by time-dependent defect spectroscopy. These insights, together with the theoretical foundation provided by the non-radiative multi-phonon (NMP) theory, led to the development of the four-state NMP model. This model describes charging processes of oxide defects microscopically, and it is able to unify reliability phenomena such as bias temperature instability, random telegraph noise and stressinduced leakage currents. Furthermore, it correctly describes the continuous degradation measured on large-area devices and the discrete trapping events observed on nanoscale devices, using the same parameters. We finally also demonstrate how this comprehensive validity can be exploited to efficiently extract the physical model parameters in order to simulate the variability and reliability of nanoscale devices.

# Introduction

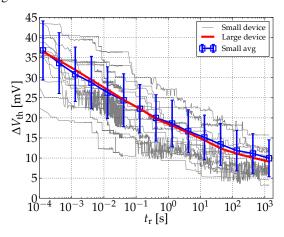

Charge trapping events in nanoscale devices can be identified and quantified based on the height of the step they cause in the threshold voltage. By applying time-dependent defect spectroscopy (TDDS) [1], the time constants of defects corresponding to these steps can be extracted. Based on nonradiative multiphonon (NMP) theory [2, 3], the four-state NMP model has been developed which can explain these biasand temperature dependent time constants for various stress conditions. In accordance with measurements, this model also explains the wide distribution of time constants [4, 5] and the link between random telegraph noise (RTN) [6-10] and bias temperature instabilities (BTI) [11–18]. As a wide distribution of time constants implies a pronounced variability of nanoscale devices, a lot of defects have to be characterized with TDDS in order to obtain the distribution of the defect parameters. However, as TDDS measurements are very time consuming it is difficult to obtain these distribution this way [19]. In order to obtain these technology dependent defect parameters efficiently, the distributions can be extracted from large-area devices (or many nanoscale devices in parallel). This approach is based on the assumption that the distributions of defects properties are the same for nanoscale and large-area devices of the same technology (see Fig. 1).

# MICROSCOPIC OXIDE DEFECTS

Important details about the nature of oxide defects can be obtained by measuring and analyzing the discrete steps of the threshold voltage during the recovery of previously stressed nanoscale devices [13, 20–22]. The TDDS uses a "spectral map" where these steps enter according to their step height and emission time. This is done for many subsequent stress and recovery cycles on the same device which give rise to clusters of similar step height and emission times in the spectral map.

Fig. 1: The recovery of the threshold voltage of previously stressed nanoscale devices (grey) shows discrete steps which correspond to single charge trapping events. The average of these recovery traces (blue) was reduced by 30% to obtain perfect agreement with the recovery data measured on a large-area device of the same technology (red).

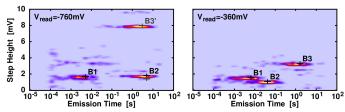

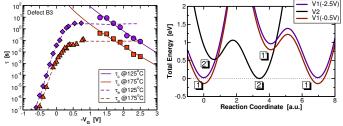

As the step height of a defect is mainly determined by its position along the channel, these clusters can be assigned to particular defects, and thereby reveal the statistics of their annealing process. By evaluating these clusters for varying stress times, the statistics of defect activation can be obtained as well. Doing so for various stress voltages, the effective capture  $(\tau_c)$  and emission time constants  $(\tau_e)$  of single defects as a function of the gate voltage and the temperature are accessible. Such TDDS studies have revealed defects with a distinct sensitivity to the readout voltage as shown in Fig. 2. Furthermore, the measured capture and emission time constants were found to be only weakly correlated, which implies metastable states in addition to the two stable charge states. Based on these considerations the microscopic fourstate NMP model has been developed where the charge state transitions are modeled according to the NMP theory and the others follow simple transition state theory. This model approximates the energy potential surface along the transition path between the states by quantum harmonic oscillators. The system energy can be plotted in configuration coordinate (CC) diagrams which determine the transition dynamics of the defect. Therein, the voltage dependence enters via the position and bias dependent electrostatic potential. The parameters which define the CC diagrams, and thereby the transitions dynamics, can be obtained from density functional theory calculations on suitable defect structures [23]. Such studies on likely defect candidates have provided reference values of these parameters. Based on this data, the four-state NMP model can explain all phenomena observed in TDDS measurements. Fig. 3 shows TDDS data and the corresponding simulation results for an exemplary defect.

Fig. 2: Typical spectral maps obtained by the TDDS at two different readout (recovery) voltages. Three defects are clearly visible. Defect B1, is a fixed charge trap with an emission time independent of the readout voltage. Defects B2 and B3, however, are switching oxide traps with a bias-dependent emission time, with B2 being much more sensitive than B3. Also, for these defects, the step-heights are very sensitive to the readout voltage [24].

Fig. 3: The capture and emission times of switching trap B3 at two temperatures (symbols: data, lines: four-state NMP model). Excellent agreement is obtained over 8 orders of magnitude.

# DISTRIBUTION OF DEFECTS

With its physical model parameters, the four-state NMP model can explain various aspects of charge trapping related reliability issues. The wide distributions of the parameters can be efficiently extracted by applying information obtained on the single defect level to large-area devices.

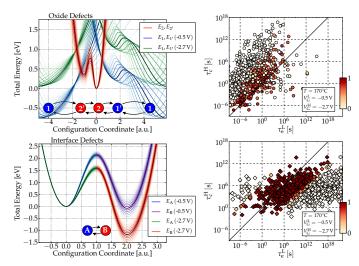

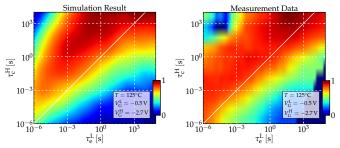

In order to cover the whole degradation picture as measured on large-area devices, the four-state NMP model, accounting for oxide defects, has to be complemented by a model which describes the creation of interface states [25]. We model the creation and annealing of these interface states using a simple phenomenological double well model and evaluate their charge with an amphoteric SRH model. The transitions of the double well model can be depicted in a CC diagram as well and we assume all parameters which define the CC diagrams of both, the four-state NMP and the double well model, to be independent and normally distributed, while the spatial distribution of all defects and precursors is assumed to be uniform. In Fig. 4 the distribution of CC diagrams is shown for both defects types, together with the resulting distributions of the emission time constant during low gate voltage  $\left( au_{\mathrm{e}}^{\mathrm{L}} = au_{\mathrm{e}} \left( V_{\mathrm{G}}^{\mathrm{L}} \right) \right)$  and capture time constants during high gate voltage  $\left( au_{\mathrm{c}}^{\mathrm{H}} = au_{\mathrm{c}} \left( V_{\mathrm{G}}^{\mathrm{H}} \right) \right)$ .

An exemplary parameter extraction has been demonstrated recently for a 2.2 nm SiON pMOSFET technology using different stress voltages ( $-V_{\rm G}=1.2,1.7,2.2,2.7,3.2\,{\rm V}$ ), temperatures (T=125 and  $170^{\circ}{\rm C}$ ), and stress and recovery times in the range  $1\,\mu{\rm s}{-}100\,{\rm ks}$  [26]. The threshold voltage shift during recovery was measured using the stress-measure-stress technique, where repetitive stress-recovery cycles were performed on the same device with stress times increasing for each subsequent cycle. With this technique the threshold voltage is not measured during stress. Therefore, this information has to be obtained indirectly by making the measurement delay  $t_{\rm D}$  between switching to recovery voltage

Fig. 4: **Top left**: Exemplary distribution of the CC diagrams which describe four-state NMP defects. The opaque lines represent the mean values and the fade-out illustrates up to one  $\sigma$  of the distributions. For simplicity this CC diagram only illustrates the situation for carrier exchange with the valence band of the substrate. An increase of the gate voltage shifts the energies according to the difference of the electrostatic potential at the defect site compared to the surface potential. **Top right**: The defects corresponding to the distributed CC diagrams plotted according to their time constants  $\tau_{\rm c}^{\rm H}$  and  $\tau_{\rm e}^{\rm L}$ . Their color indicates their contribution to the threshold voltage shift. **Bottom**: Same as in the upper row but for the double well model.

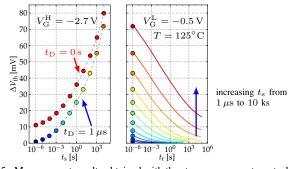

Fig. 5: Measurement results obtained with the stress-measure-stress technique. Repeated stress-recovery cycles are performed in order to indirectly measure degradation during stress. It is important to keep the delay after switching to recovery and performing the first measurement small, as even for a very short measurement delay with  $t_{\rm D}$  of  $1\,\mu{\rm s}$  some defects are already discharged and this information about degradation is lost.

and measuring the threshold voltage as short as possible. Still, it is important to note that some defects will already be discharged even for the shortest possible measurement delays (see Fig. 5). In order to obtain comparable data for various combinations of stress voltages and temperatures, the measured device should behave the same for each measurement, but the typically observed "permanent" threshold voltage shift of previously stressed devices requires to measure each combination of stress voltage and temperature on another "fresh" device. Therefore, device to device variability has to be taken into account. For the applied large-area pMOSFETs with an gate area of 1  $\mu m^2$  this variability was found to be in the range of  $\pm 15\%$ , apparently mainly due to the permanent component. Given the correct distribution of the physical defect parameters and large enough devices, the simulations results for all possible BTI stress conditions have to be in agreement with the corresponding measurements. Fig. 6 shows the comparison of measured and simulated degradation, based

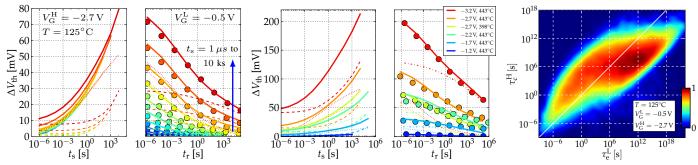

Fig. 6: Left: Comparison of simulated threshold voltage shifts (solid lines) to the experimental data (dots) during stress  $(t_s)$  and recovery  $(t_r)$ . The contribution of the four-state NMP defects (dotted lines) and of the defects described by the double-well model (dashed lines) are also shown separately. The stress-recovery measurements and simulations were performed on the same device subsequently with increasing stress durations. However, for the sake of convenience they are plotted on top of each other in the stress and recovery part of the figure. Middle: Same as left for various stress voltages and temperatures, but only the last stress-recovery cycle is shown. Right: The CET map computed from the simulated oxide and interface defects.

Fig. 7: Comparison of the simulated (**left**) and measured (**right**) CET maps within the measurement window. The important characteristics are reproduced: the center of the distribution is above the  $\tau_{\rm c}^{\rm L}=\tau_{\rm e}^{\rm L}$  axis for short emission times and starts to cross the axis towards larger emission times.

on the distribution of defect parameters for this technology, together with the capture/emission time (CET) map [27–29] which was computed from the simulated microscopic defects. The density plotted in CET maps represents the contribution to the threshold voltage shift depending on the capture and emission time constants. It is important to recall that the emission time constant is given for low gate voltage while the capture time is given for high gate voltage. This implies that CET maps represent certain stress scenarios also including the temperature. The contribution of a particular defect to this density at  $\left(\tau_{\rm c}\left(V_{\rm G}^{\rm H}\right),\,\tau_{\rm e}\left(V_{\rm G}^{\rm L}\right)\right)$  is given by its step height times the probability that the defect changes its charge state for the given stress setup. Using the equilibrium occupancy  $f\left(V_{\rm G}\right)$ , the later can be described by its equilibrium occupancy difference which evaluates to [30]

$$a = f(V_{\mathrm{G}}^{\mathrm{H}}) - f(V_{\mathrm{G}}^{\mathrm{L}}) = \frac{\tau_{\mathrm{e}}^{\mathrm{H}}}{\tau_{\mathrm{e}}^{\mathrm{H}} + \tau_{\mathrm{c}}^{\mathrm{H}}} - \frac{\tau_{\mathrm{e}}^{\mathrm{L}}}{\tau_{\mathrm{e}}^{\mathrm{L}} + \tau_{\mathrm{c}}^{\mathrm{L}}}.$$

In contrast to this computation from *simulation results* of single defects, CET maps can also be calculated directly from *measurement data*. As the integral of CET maps gives the threshold voltage shift, this can be done by taking the mixed partial derivative of the measured recovery traces [27, 30]. This allows for a comparison of measurement data and simulation results within the measurement window (see Fig. 7).

# IMPLICATIONS OF OXIDE DEFECTS

When the defect parameter distribution is applied to obtain the microscopic defects of nanoscale devices, various reliability aspects become apparent. First, nanoscale devices with typical defect densities possess only a few tens of defects in typical TDDS measurement windows, and as their number

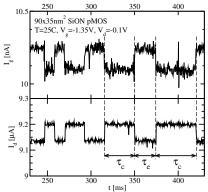

Fig. 8: A hole capture event in the oxide reduces the drain current  $I_{\rm d}$  while a subsequent emission of the hole restores the original electrostatics and, thereby,  $I_{\rm d}$ . On nanoscale devices these events are visible as discrete steps in the drain current (lower panel). At the same time discrete steps of the gate current  $I_{\rm g}$  can be observed (upper panel) which indicates the opening and closing of a tunneling path that correlates with the capture and emission events [31].

is subject to random fluctuations, significant variability is inherent. More importantly, the parameters of the defects are drawn from broad distributions which explains the large variability observed on nanoscale devices. Another important insight which is perfectly described by the four-state NMP model is that RTN and BTI are just different realizations of the same mechanism: BTI is related to charging of defects in the oxide, but for certain stress conditions the capture and emission time constants can be roughly equal, leading to a stochastically repeating charging and discharging as it is usually observed in RTN measurements. The metasable states of the model can also explain the more involved anomalous RTN. Reliability issues related to trap assisted tunneling through gate oxides come naturally with microscopic defects. For example, the effect of stress induced leakage current (SILC) is inherent to the four-state NMP model and can be explained by the CC diagram where for certain stress voltages capture processes take place via the channel while emission processes are governed by gate interaction. The correlation between tunneling through the gate oxide and BTI has been verified experimentally (see Fig. 8).

#### CONCLUSIONS

The four-state NMP model can successfully describe various charge trapping related reliability issues which can be observed on nanoscale up to large-area devices. For the understanding of these defects it is important to know the *distributions* of the physical model parameters. We have demonstrated

how large-area devices can be employed to efficiently extract these widely distributed parameters. Simulations based on these parameter distribution show good agreement for various stress conditions on large-area devices and they allow for a detailed insight into the relation of large and small devices with respect to reliability issues. Finally, the extracted distribution of defect parameters enables accurate simulation and investigation of charge trapping processes in nanoscale devices.

# **ACKNOWLEDGEMENTS**

This work has received funding from the European Community's FP7 Project n°619234 (MoRV) and the Intel Sponsored Research Project n°2013111914.

# REFERENCES

- [1] T. Grasser, H. Reisinger, P.-J. Wagner, W. Goes, F. Schanovsky, and B. Kaczer, "The Time Dependent Defect Spectroscopy (TDDS) for the Characterization of the Bias Temperature Instability," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 16–25, May 2010.

- [2] K. Huang and A. Rhys, "Theory of Light Absorption and Non-Radiative Transitions in F-Centres," *Proc.R.Soc.A*, vol. 204, pp. 406–423, 1950.

- [3] D. Lang and C. Henry, "Nonradiative Recombination at Deep Levels in GaAs and GaP by Lattice-Relaxation Multiphonon Emission," *Physical Review Letters*, vol. 35, no. 22, pp. 1525–1528, 1975.

- [4] B. Kaczer, T. Grasser, J. Martin-Martinez, E. Simoen, M. Aoulaiche, P. Roussel, and G. Groeseneken, "NBTI from the Perspective of Defect States with Widely Distributed Time Scales," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 55–60, 2009.

- [5] M. Toledano-Luque, B. Kaczer, J. Franco, P. Roussel, T. Grasser, T. Hoffmann, and G. Groeseneken, "From Mean Values to Distributions of BTI Lifetime of Deeply Scaled FETs Through Atomistic Understanding of the Degradation," in *IEEE Symposium on VLSI Technology Digest* of Technical Papers, 2011.

- [6] K. Ralls, W. Skocpol, L. Jackel, R. Howard, L. Fetter, R. Epworth, and D. Tennant, "Discrete Resistance Switching in Submicrometer Silicon Inversion Layers: Individual Interface Traps and Low-Frequency (1/f?) Noise," *Physical Review Letters*, vol. 52, no. 3, pp. 228–231, 1984.

- [7] M. Kirton and M. Uren, "Noise in Solid-State Microstructures: A New Perspective on Individual Defects, Interface States and Low-Frequency (1/f) Noise," Adv. Phys., vol. 38, no. 4, pp. 367–486, 1989.

- [8] A. Palma, A. Godoy, J. A. Jimenez-Tejada, J. E. Carceller, and J. A. Lopez-Villanueva, "Quantum Two-Dimensional Calculation of Time Constants of Random Telegraph Signals in Metal-Oxide-Semiconductor Structures," *Physical Review B*, vol. 56, no. 15, pp. 9565–9574, 1997.

- [9] D. Fleetwood, H. Xiong, Z.-Y. Lu, C. Nicklaw, J. Felix, R. Schrimpf, and S. Pantelides, "Unified Model of Hole Trapping, 1/f Noise, and Thermally Stimulated Current in MOS Devices," *IEEE Trans.Electron Devices*, vol. 49, no. 6, pp. 2674–2683, 2002.

- [10] T. Nagumo, K. Takeuchi, T. Hase, and Y. Hayashi, "Statistical Characterization of Trap Position, Energy, Amplitude and Time Constants by RTN Measurement of Multiple Individual Traps," in *Proc. Intl. Electron Devices Meeting (IEDM)*, pp. 628–631, 2010.

- [11] C. Zhao, J. Zhang, G. Groeseneken, and R. Degraeve, "Hole-Traps in Silicon Dioxides - Part II: Generation Mechanism," *IEEE Trans. Electron Devices*, vol. 51, no. 8, pp. 1274–1280, 2004.

- [12] V. Huard, C. Parthasarathy, and M. Denais, "Single-Hole Detrapping Events in pMOSFETs NBTI Degradation," in *Proc. Intl.Integrated Reliability Workshop*, pp. 5–9, 2005.

- [13] T. Wang, C.-T. Chan, C.-J. Tang, C.-W. Tsai, H. Wang, M.-H. Chi, and D. Tang, "A Novel Transient Characterization Technique to Investigate Trap Properties in HfSiON Gate Dielectric MOSFETs-From Single Electron Emission to PBTI Recovery Transient," *IEEE Trans. Electron Devices*, vol. 53, no. 5, pp. 1073–1079, 2006.

- [14] D. Ang, S. Wang, G. Du, and Y. Hu, "A Consistent Deep-Level Hole Trapping Model for Negative Bias Temperature Instability," *IEEE Trans. Dev. Mat. Rel.*, vol. 8, no. 1, pp. 22–34, 2008.

- [15] T. Grasser, B. Kaczer, W. Goes, T. Aichinger, P. Hehenberger, and M. Nelhiebel, "Understanding Negative Bias Temperature Instability in the Context of Hole Trapping," *Microelectronic Engineering*, vol. 86, no. 7-9, pp. 1876–1882, 2009.

- [16] H. Reisinger, T. Grasser, and C. Schlünder, "A Study of NBTI by the Statistical Analysis of the Properties of Individual Defects in pMOSFETs," in *Proc. Intl.Integrated Reliability Workshop*, pp. 30–35, 2009.

- [17] T. Grasser, ed., Bias Temperature Instability for Devices and Circuits. Springer, New York, 2014.

- [18] T. Grasser, K. Rott, H. Reisinger, M. Waltl, J. Franco, and B. Kaczer, "A Unified Perspective of RTN and BTI," in *Proc. Intl.Rel.Phys.Symp.* (IRPS), pp. 4A.5.1–4A.5.7, June 2014.

- [19] T. Grasser, K. Rott, H. Reisinger, M. Waltl, P. Wagner, F. Schanovsky, W. Goes, G. Pobegen, and B. Kaczer, "Hydrogen-Related Volatile Defects as the Possible Cause for the Recoverable Component of NBTI," in *Proc. Intl.Electron Devices Meeting (IEDM)*, Dec. 2013.

- [20] M. Toledano-Luque, B. Kaczer, P. Roussel, T. Grasser, G. Wirth, J. Franco, C. Vrancken, N. Horiguchi, and G. Groeseneken, "Response of a Single Trap to AC Negative Bias Temperature Stress," in *Proc. Intl. Rel. Phys. Symp.* (IRPS), pp. 364–371, 2011.

- [21] J. Zou, R. Wang, N. Gong, R. Huang, X. Xu, J. Ou, C. Liu, J. Wang, J. Liu, J. Wu, S. Yu, P. Ren, H. Wu, S. Lee, and Y. Wang, "New Insights into AC RTN in Scaled High-κ/Metal-gate MOSFETs under Digital Circuit Operations," in *IEEE Symposium on VLSI Technology Digest of Technical Papers*, pp. 139–140, 2012.

- [22] T. Grasser, K. Rott, H. Reisinger, P.-J. Wagner, W. Goes, F. Schanovsky, M. Waltl, M. Toledano-Luque, and B. Kaczer, "Advanced Characterization of Oxide Traps: The Dynamic Time-Dependent Defect Spectroscopy," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 2D.2.1–2D.2.7, Apr. 2013.

- [23] T. Grasser, W. Goes, Y. Wimmer, F. Schanovsky, G. Rzepa, M. Waltl, K. Rott, H. Reisinger, V. Afanasev, A. Stesmans, A.-M. El-Sayed, and A. Shluger, "On the Microscopic Structure of Hole Traps in pMOSFETs," in *Proc. Intl. Electron Devices Meeting (IEDM)*, Dec. 2014.

- [24] J. Franco, B. Kaczer, M. Toledano-Luque, P. Roussel, J. Mitard, L. Ragnarsson, L. Witters, T. Chiarella, M. Togo, N. Horiguchi, G. Groeseneken, M. Bukhori, T. Grasser, and A. Asenov, "Impact of Single Charged Gate Oxide Defects on the Performance and Scaling of Nanoscaled FETs," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, p. 5A.4.1, 2012.

- [25] T. Aichinger, M. Nelhiebel, and T. Grasser, "Unambiguous Identification of the NBTI Recovery Mechanism using Ultra-Fast Temperature Changes," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 2–7, 2009.

- [26] G. Rzepa, W. Goes, G. Rott, K. Rott, M. Karner, C. Kernstock, B. Kaczer, H. Reisinger, and T. Grasser, "Physical Modeling of NBTI: From Individual Defects to Devices," in *Proc. Simulation of Semiconductor Processes and Devices*, pp. 81–84, 2014.

- [27] H. Reisinger, T. Grasser, W. Gustin, and C. Schlünder, "The Statistical Analysis of Individual Defects Constituting NBTI and its Implications for Modeling DC- and AC-Stress," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 7–15, May 2010.

- [28] H. Reisinger, T. Grasser, K. Ermisch, H. Nielen, W. Gustin, and C. Schlünder, "Understanding and Modeling AC BTI," in *Proc. Intl. Rel. Phys. Symp.* (IRPS), pp. 597–604, Apr. 2011.

- [29] T. Grasser, P.-J. Wagner, H. Reisinger, T. Aichinger, G. Pobegen, M. Nelhiebel, and B. Kaczer, "Analytic Modeling of the Bias Temperature Instability Using Capture/Emission Time Maps," in *Proc. Intl. Electron Devices Meeting (IEDM)*, pp. 27.4.1–27.4.4, Dec. 2011.

- [30] T. Grasser, "Stochastic Charge Trapping in Oxides: From Random Telegraph Noise to Bias Temperature Instabilities," *Microelectronics Reliability*, vol. 52, pp. 39–70, 2012.

- [31] M. Toledano-Luque, B. Kaczer, E. Simoen, R. Degraeve, J. Franco, P. Roussel, T. Grasser, and G. Groeseneken, "Correlation of Single Trapping and Detrapping Effects in Drain and Gate Currents of Nanoscaled nFETs and pFETs," pp. XT.5.1–XT.5.6, 2012.