## CHARACTERIZATION OF THE PERMANENT COMPONENT OF

## **MOSFET DEGRADATION MECHANISMS**

## Bianka Ullmann, Michael Waltl, and Tibor Grasser Institute for Microelectronics

In modern electronic devices millions of metal-oxide-semiconductor field-effect transistors (MOSFETs) are used. The lifetimes of such nano-scale MOSFETs are limited due to an unwanted change of the device characteristics during operation. This detrimental device behaviour is caused by material defects, defined by deviations within the short-range order of the amorphous gate oxide of the MOSFET and are simply called traps. These traps can capture or emit charge carriers from the silicon substrate and from the gate oxide, described by non-radiative multiphonon transitions [1–3]. Quite remarkably, in nano-scale MOSFETs the charge exchange events cause discrete steps of several pA up to  $\mu$ A in the drain source current  $I_{\rm d}$ . The larger ones allow us to characterize the bias and temperature dependent charge capture and emission times. Thus more detailed insight into the nature of single defects is possible, which contributes to a deeper understanding of degradation mechanisms like bias temperature instability (BTI) [4] and hot carrier degradation (HCD) [5].

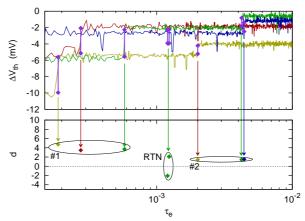

To determine the nature of traps responsible for BTI and HCD, we compare simulations of physical processes computed by the device simulator MINIMOS-NT [6] with our collected experimental data. On the experimental side the time dependent defect spectroscopy (TDDS) has been proposed [7–9]. In detail, we analyze threshold voltage shifts  $\Delta V_{\rm th}$  in the sub-mV range caused by charge capture and emission events during sequences of stress (typically  $V_{\rm g} > V_{\rm th}$ , where  $V_{\rm g}$  is the gate voltage) and recovery ( $V_{\rm g} \approx V_{\rm th}$ ) cycles at different temperatures. We make use of the facts that nano-scale MOSFETs contain just a handful of traps and that the smaller the MOSFET is, the larger the observed step heights of  $\Delta V_{\rm th}$  get. Therefore, we can focus on particular defects. Fig. 1 shows the discrete steps of the recorded  $\Delta V_{\rm th}$  of a 500 nm  $\times$  120 nm SiON nMOS. This electrical response of the traps allows to gain insight into their physical properties and thus provides information about the deterministic distribution of capture and emission times which are compared to non-radiative multiphonon (NMP) simulations.

The typical capture and emission times of traps vary by many orders of magnitude, from  $\mu$ s to weeks. For degradation processes of MOSFETs, traps with emission times lying outside the experimental window (typically up to 10 ks), also called permanent traps, are of special interest for us. They are expected to dominate the lifetime distri-

Fig. 1. The discrete steps of the recorded  $\Delta V_{\rm th}$  during recovery bias conditions (top) are mapped to the spectral map (bottom), where each defect appears as a cluster characterized by its step height d in mV and its emission time  $\tau_{\rm e}$  in s (reprinted from [11]). In case of random telegraph noise (RTN), the cluster is symmetrically arranged around the abscissae

bution. It has to be noted that the capture and emission process is strongly temperature dependent. A part of our current research focuses on the idea of shifting large capture and emission times into experimentally feasible time slots (measurement time below 1 ks) by applying controlled temperature pulses during device recovery. Due to the temperature dependence of the capture and emission events, the puls-like elevation of the temperature during recovery stimulates the charge emission. The challenge of the required immediate temperature ramp has been overcome by using MOSFETs with integrated poly-silicon wires, also called polyheaters [10]. We have developed a hardware and software application for temperature control of the polyheaters within the TDDS framework. By shifting large emission times into the experimental window, we are able to analyse defects, which seem to be otherwise permanent. From future measurements we expect a significant contribution to the understanding of the permanent degradation, especially on the HCD.

We will give a brief overview on the state of the art of measurements of MOSFETs with integrated polyheaters and the expected impact of the experimental data on the understanding of the permanent component of degradation mechanisms.

## REFERENCES

- [1] M. Kirton et al., Adv. Phys. 38, 367 (1989).

- [2] K. Huang et al., Proceedings of the Royal Society of London. Series A 204, 406 (1950).

- [3] C. Henry et al., Phys.Rev.B 15, 989 (1977).

- [4] Bias Temperature Instability for Devices and Circuits, edited by T. Grasser (Springer-Verlag, 2013).

- [5] Hot Carrier Degradation in Semiconductor Devices, edited by T. Grasser (Springer-Verlag, 2014).

- [6] Minimos-NT User Manual Release 2014.03.

- [7] T. Grasser et al., Proc.IRPS (2010), pp. 16 25.

- [8] T. Grasser et al., Phys.Rev.B 82, 245318 (2010).

- [9] T. Grasser, Microelectronics Reliability 52, 39 (2012).

- [10] G. Pobegen et al., Proc.IEDM (2011), pp. 27 31.

- $[11] \ \ M. \ Waltl \ \textit{et al.}, \ \textit{Proc.IRPS} \ (2014), \ pp. \ XT.18.1 XT.18.5.$