# Hot-Carrier Degradation and Bias-Temperature Instability in Single-Layer Graphene Field-Effect Transistors: Similarities and Differences

Yury Illarionov, *Graduate Student Member, IEEE*, Anderson Smith, *Graduate Student Member, IEEE*, Sam Vaziri, *Graduate Student Member, IEEE*, Mikael Ostling, *Fellow, IEEE*, Thomas Mueller, Max Lemme, *Senior Member, IEEE*, and Tibor Grasser, *Senior Member, IEEE*

Abstract—We present a detailed analysis of hot-carrier degradation (HCD) in graphene field-effect transistors (GFETs) and compare those findings with the bias-temperature instability (BTI). Our results show that the HCD in GFETs is recoverable, similar to its BTI counterpart. Moreover, both the degradation mechanisms strongly interact. Particular attention is paid to the dynamics of HCD recovery, which can be well fitted with the capture/emission time (CET) map model and the universal relaxation function for some stress conditions, quite similar to the BTI in both GFETs and Si technologies. The main result of this paper is an extension of our systematic method for benchmarking new graphene technologies for the case of HCD.

Index Terms—Bias-temperature instability (BTI), graphene FETs (GFETs), hot-carrier degradation (HCD), reliability.

## I. INTRODUCTION

RAPHENE is a next-generation material for an application in modern microelectronic and nanoelectronic devices. That is due to its outstanding physical and electrical properties, such as a high saturation velocity [1] and an extremely high room-temperature carrier mobility [2], [3], and good compatibility with the standard complimentary metaloxide-semiconductor (CMOS) technology. During the last decade, several research groups have succeeded in fabricating graphene-based FETs (GFETs) [4]–[9] and related electronic

Manuscript received July 3, 2015; revised September 12, 2015; accepted September 17, 2015. Date of current version October 20, 2015. This work was supported in part by the European Commission through STREP Projects MoRV under Grant 619234 and GRADE under Grant 317839, in part by the German Research Foundation under Grant 2440/1-1 and Grant 2440/2-1, and in part by the European Research Council Starting Grant under Grant 307311. The review of this paper was arranged by Editor G. L. Snider.

Y. Illarionov and T. Grasser are with the Institute for Microelectronics, Technische Universität Wien, Vienna 1040, Austria, and also with the Ioffe Physical-Technical Institute, Saint Petersburg 194021, Russia (e-mail: illarionov@iue.tuwien.ac.at; grasser@iue.tuwien.ac.at).

A. Smith, S. Vaziri, and M. Ostling are with the School of Information and Communication Technology, KTH Royal Institute of Technology, Kista 16440, Sweden (e-mail: andsmi@kth.se; vaziri@kth.se; ostling@kth.se).

T. Mueller is with the Institute for Photonics, Technische Universität Wien, Vienna 1040, Austria (e-mail: thomas.mueller@tuwien.ac.at).

M. Lemme is with the University of Siegen, Siegen 57076, Germany (e-mail: max.lemme@uni-siegen.de).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2015.2480704

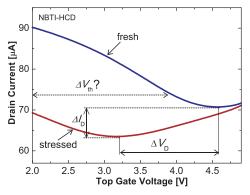

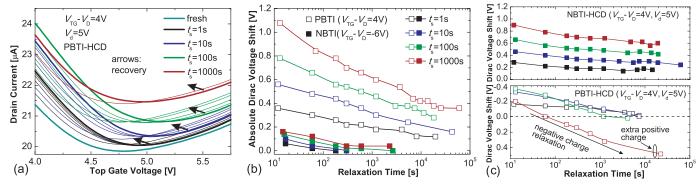

Fig. 1. Bias and HC stresses result in a shift of the voltage  $(\Delta V_D)$  and the current  $(\Delta I_D)$  at the Dirac point. For a strong HC stress,  $\Delta I_D$  can be significant. Therefore, the previously used definition of GFET threshold voltage  $V_{\rm th}$  as the gate bias at which  $I_d = (I_{\rm dmax} - I_{\rm dmin})/2$  [13], [15], [17] is unsuitable. For a correct estimate of the trapped charge density, we suggest to use  $\Delta V_D$ .

devices [10], [11]. Therefore, the investigation of their dielectric reliability is required. Although a few attempts to study the bias-temperature instabilities (BTIs) in GFETs have been undertaken [12]–[15], no analysis has been attempted with respect to hot-carrier degradation (HCD), which is another key reliability issue in the conventional Si metal–oxide–semiconductor field-effect transistors (MOSFETs) [16].

In this paper, we perform a detailed study of HCD in the high-k top gate of double-gated GFETs and compare the dynamics of this phenomenon with the BTIs in both GFETs and Si technologies. We demonstrate that, similar to the BTI in GFETs, the degradation dynamics of HCD should be expressed in terms of a voltage shift at the Dirac point. For some stress conditions, this allows the benchmarking of HCD in GFETs using the methods developed for a BTI analysis in Si technologies.

### II. DEVICES

We perform our studies on double-gated GFETs fabricated using a standard lithography process [10]. In these devices, 25-nm-thick Al<sub>2</sub>O<sub>3</sub> is used as a top-gate insulator, and 1800-nm-thick SiO<sub>2</sub> is employed as a back-gate insulator; the channel lengths and widths are 1–4 and 20–80  $\mu$ m, respectively. Initially, the devices have been baked at T=300 °C

in a  $H_2$ /He mixture, which allowed us to reach a significant decrease in variability [18]. As shown in [18] and [19], it has also been verified that our GFETs show all typical properties known from literature reports [12].

## III. EXPERIMENT

Our studies are based on the analysis of the top-gate transfer characteristics of GFETs, which can be sensitive to the detrimental impact of the environment [15]. For this reason, the measurements were performed in vacuum ( $10^{-5}$  torr). The impact of HC and bias stresses on the device performance was examined as follows. After measuring the reference transfer characteristic, a stress with a constant  $V_{TG}$  and a drain voltage  $V_d$  was applied for a certain time. Then, the recovery of the stressed device was monitored for several hours/days. For a more detailed analysis of the degradation/recovery dynamics, on each device, the measurements have been repeated for increasing stress times ( $t_s = 1$ , 10, 100, and 1000 s) with readjusted  $V_{TG} - V_D(t_s) \approx$  const. The latter was necessary to approximately maintain a constant oxide field during all stress rounds [18].

# IV. RESULTS AND DISCUSSION

Fig. 1 shows the typical impact of HC and bias stresses with negative  $V_{TG} - V_D$  (i.e., NBTI-HCD) on the top-gate transfer characteristics, which results in both vertical  $(\Delta I_D)$ and horizontal  $(\Delta V_D)$  shifts of the Dirac point. Furthermore, the shape of the transfer characteristics is modified, an effect that becomes more pronounced after a stronger HCD stress. The origin of this behavior is a change in the concentration of charged border traps, which may have a significant impact on both electrostatics and mobility. In [18] and [19], we demonstrated for BTI that the presence of a vertical drift  $\Delta I_D$ makes the previously used definition of the GFET threshold voltage  $V_{\text{th}}$  at which  $I_d = (I_{d\text{max}} - I_{d\text{min}})/2$  [13], [15], [17] questionable. Thus, it was suggested to use  $\Delta V_D$  versus the relaxation time  $t_r$  traces to capture the essence of the recovery dynamics. In the case of HCD, this is also extremely important, because the typically observed magnitudes of the vertical drift

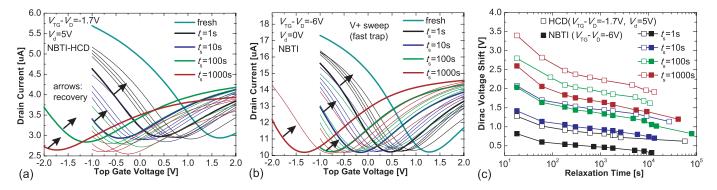

Fig. 3. (a) Time evolution of the top-gate transfer characteristics after pure HCD stress ( $V_{\rm TG}-V_D=0$ ). The Dirac point is shifted toward left, which indicates that positively charged defects are created, similar to pure NBTI stress. (b) Contrary to Si technologies, significant recovery takes place, demonstrating the similarity of NBTI and HCD in GFETs.

are even stronger than those of BTI. However, it is worth to remark that our manual measurements introduce a time delay of  $\sim$ 10–15 s between the end of the stress and the first  $t_r$  point. Based on our previous simulation results for GFETs [18] and an experience obtained on Si technologies [20], we assume that a significant recovery takes place during this time. Therefore, for both BTI and HCD, we are mostly dealing with long-term  $\Delta V_D(t_r)$  recovery traces. This is still enough for a proper comparison of the two phenomena.

In [18], we illustrated that the measured transfer characteristics depend on the sweep direction. When coming from a negative bias stress and sweeping toward positive  $V_{TG}$  ( $V^+$  mode),

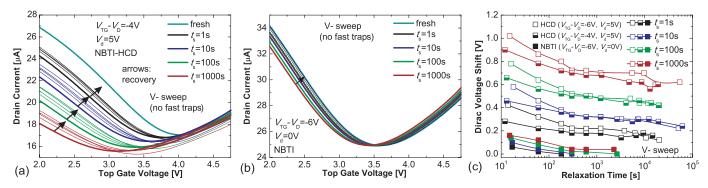

Fig. 4. Time evolution of the top-gate transfer characteristics after (a) NBTI-HCD and (b) pure NBTI stresses ( $t_s = 1$ , 10, 100, and 1000 s) with approximately constant  $V_{TG} - V_D$ . In both the cases, the measurements have been done in  $V^-$  mode, in order to reduce the impact of the fast trap component. Both  $\Delta V_D$  and  $\Delta I_D$  caused by the NBTI-HCD stress are significantly larger than those caused by the NBTI stress, despite the smaller  $V_{TG} - V_D$  in the former case. (c) Recovery traces corresponding to pure NBTI and NBTI-HCD stresses (no fast trap component). Degradation caused by pure NBTI stress is the weakest and recovers completely while the HCD component significantly accelarates NBTI. HCD stress with  $V_{TG} - V_D = -6$  V initially leads to a stronger degradation than with  $V_{TG} - V_D = -4$  V, mainly due to a stronger NBTI component. However, the long-time tails are similar, indicating that the weakly recoverable HC components are nearly the same.

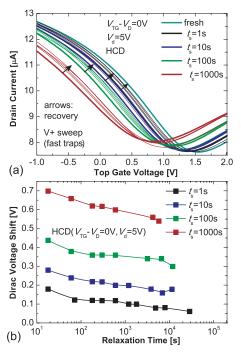

Fig. 5. (a) Time evolution of the top-gate transfer characteristics after HCD stress ( $t_s = 1, 10, 100$ , and 1000 s) with approximately constant positive  $V_{TG} - V_D(t_s)$  (i.e., positive bias-temperature instability (PBTI)–HCD). The Dirac point shift is significantly smaller than that in the case of NBTI–HCD with similar stress conditions (Fig. 4). (b) Recovery traces corresponding to pure NBTI and pure PBTI stresses. The latter is significantly stronger, despite the smaller  $V_{TG} - V_D$ . (c) Similarly for NBTI–HCD and PBTI–HCD with the same absolute  $V_{TG} - V_D$ . In this case, NBTI–HCD is significantly stronger than PBTI. The origin of this behavior is the HC component, which introduces positively charged defects, similar to NBTI and contrary to PBTI. Interestingly, at larger  $t_s$ , PBTI–HCD stress may lead to a shift of the Dirac point in the opposite direction during recovery. This is associated with extra positively charged defects, which are introduced by the HC component.

$\Delta V_D$  contains some fast trap contribution, which also impacts the recovery traces for NBTI-like degradation following HC stress. This fast trap contribution is effectively suppressed by sweeping toward negative  $V_{TG}$  ( $V^-$  mode). Initially, we performed the measurements in  $V^+$  sweep mode. Fig. 2 shows the time evolution of the transfer characteristics corresponding to NBTI-HCD and pure NBTI stresses. Even though a much higher  $V_{TG} - V_D$  was used for pure NBTI, the degradation caused by NBTI-HCD stress is significantly stronger. This means that the HC component introduces positively charged defects, which substantially accelerate NBTI degradation and also have a stronger impact on mobility. Contrary to previous reports [17], our results are well reproducible [18], as baking of the devices at T = 300 °C in a H<sub>2</sub>/He mixture restores the original transfer characteristic and also results in the same degradation behavior upon restress. Fig. 3 illustrates that pure HCD stress also shifts the Dirac point in an NBTI-like manner, which confirms that positively charged defects are created. However, contrary to Si technologies, considerable recovery is observed, likely due to the absence of dangling bonds, which are otherwise typically associated with HCD [22].

In order to solidify the results, we performed similar measurements on devices with more positive values of  $V_D$ . In addition, the impact of the fast trap component has been reduced using the  $V^-$  sweep mode. The results given in Fig. 4(a) and (b) illustrate that the overall level of NBTI-like degradation in these devices is significantly lower, which is not only due to the absence of the fast trap contribution but also because of more positive initial values of  $V_D$ . However, the presence of the HC component during stress still severely accelerates the impact of NBTI. Despite the smaller  $V_{TG} - V_D$ , degradation for NBTI-HCD is significantly stronger than that for pure NBTI. The corresponding recovery traces are plotted in Fig. 4(c), where an additional data set for NBTI-HCD with  $V_{TG} - V_D = -6$  V is added. Clearly, the pure NBTI stress leading to the weakest degradation is completely recoverable. At the same time, the degradation caused by NBTI-HCD stress with larger  $V_{TG} - V_D$  is stronger. In Fig. 5, we provide similar results for HCD stress with positive  $V_{TG} - V_D$  (i.e., PBTI-HCD) and compare them with NBTI-HCD data. Although pure PBTI is much stronger than pure NBTI [Fig. 5(b)], the presence of the HCD component

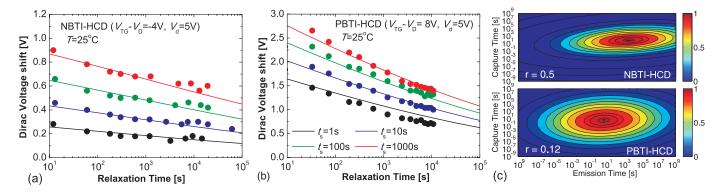

Fig. 6. Similar to the case of pure BTI [18], [19], recovery traces measured after both (a) NBTI-HCD and (b) PBTI-HCD stresses can be fitted with the CET map model [21] using a single bivariate Gaussian distribution. This, however, only works if the degradation is mainly contributed by the defects of one sign, which is the case for either NBTI-HCD or PBTI-HCD with large  $V_{TG} - V_D$ . Under these conditions, the dynamics of HCD are similar to BTI, possibly because the absence of dangling bonds in GFETs makes the defects responsible for BTI and HCD similar. (c) Underlying CET distributions obtained using the optimized CET map model are similar to those obtained for BTI in GFETs [18].

makes NBTI–HCD stronger than PBTI–HCD [Fig. 5(c)]. This means that HCD not only accelerates NBTI degradation by introducing additional positive charge but also suppresses PBTI, which creates negatively charged defects. In particular, Fig. 5(c) illustrates that the impact of the HCD component having an NBTI-like nature increases versus  $t_s$ , which may lead to a shift of the Dirac point in the opposite direction during recovery (e.g., after  $t_s = 1000$ -s stress). This suggests that there is an interaction between the defects introduced by the HC and bias components of the PBTI–HCD stress. While the PBTI-like recovery is associated with a relaxation of negatively charged defects introduced by the bias component, an extra positive charge created by the HC component makes the original  $V_D$  more negative.

As shown in [18], the suppression of the fast trap component by using the  $V^-$  sweep mode and the decrease in the device-to-device variability allowed us to fit the experimental  $\Delta V_D$  recovery for pure BTI with the capture/emission time (CET) map model [21] and the universal relaxation function [23], [24]. Considering the similarities between BTI and HCD described above, we, here, made an attempt at applying these models to fit the HCD dynamics in GFETs. The CET map model [21] assumes that BTI is the collective response of independent defects that exchange charges with the channel. Charge exchange is thermally activated, and the correlated activation energies can be described using the bivariate Gaussian distributions. The main parameters of the model are the mean values ( $\mu_c$  and  $\mu_e$ ) and the standard deviations ( $\sigma_c$  and  $\sigma_e$ ) of the capture and emission energies  $E_c$  and  $E_e$ , respectively. In addition, an uncorrelated part of the emission energy  $\Delta E_e$  and the corresponding  $\mu_{\Delta e}$  and  $\sigma_{\Delta e}$  are considered. However, it was found that the use of the original model [21] does not always produce reasonable results, possibly because the  $V_D$  shifts in GFETs are significantly larger than threshold voltage shifts in Si technologies. Therefore, we suggest to modify the model [21] by changing the implicit correlation between the standard deviations  $\sigma_e^2 = r\sigma_c^2 + \sigma_{\Delta e}^2$  with r being a new model parameter, which can be varied between 0 and 1, while in [21],

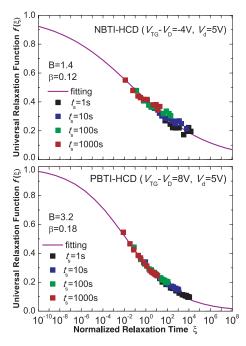

Fig. 7. HCD in GFETs can be fitted using the universal relaxation relation [23], [24]  $f(\xi) = 1/(1 + B\xi^{\beta})$ , while the parameters B and  $\beta$  remain similar to their counterparts for the BTI in both GFETs and Si technologies [18], [19]. However, the limitations are the same as in the case of the CET map model.

r was equivalent to 1. Thus, the distribution is given by

$$g(E_c, E_e) = \frac{1}{2r\pi\sigma_c\sigma_{\Delta e}} \exp \times \left( -\frac{(rE_c - \mu_c)^2}{2r^2\sigma_c^2} - \frac{(E_e - (rE_c + \mu_{\Delta e}))^2}{2\sigma_{\Delta e}^2} \right).$$

(1)

The results of both NBTI-HCD and PBTI-HCD obtained with a single Gaussian distribution corresponding to a more recoverable component are provided in Fig. 6. One can see that the fits [Fig. 6(a) and (b)] are rather reasonable that

underlines the similarity between the HCD and BTI dynamics in GFETs. The underlying CET map distributions [Fig. 6(c)] are also similar to those published previously for the BTI in GFETs [18]. Moreover, the dynamics of HCD in GFETs can also be described by the universal relaxation relation [23], [24],  $f(\xi) = 1/(1 + B\xi^{\beta})$ , where  $\xi = t_r/t_s$  is the normalized relaxation time, and B and  $\beta$  are the empirical fitting parameters (Fig. 7). Remarkably, the parameters B and  $\beta$  given in Fig. 7 are similar to their counterparts obtained from BTI data for both GFETs and Si technologies [18], [19], which further confirms the similarity in the physical mechanisms underlying degradation/recovery dynamics.

However, the described analysis is typically only possible if both the HC and bias contributions introduce the defects of the same sign (e.g., NBTI–HCD). Otherwise, if the two contributions have opposite signs (e.g., PBTI–HCD), fitting is only possible for stress conditions, under which the bias component dominates. At the same time, the dynamics of PBTI–HCD with comparable HC and bias components [Fig. 5(c)] is more complicated, and, therefore, cannot be described using such simple models [21], [23], [24].

Finally, as a remark, we should state that there was no clear channel width impact neither on HCD nor on BTI recovery within our experiments.

## V. CONCLUSION

In summary, we have performed a detailed analysis of HCD dynamics in GFETs and compared those findings with the BTIs in both GFETs and Si technologies. It has been demonstrated that the presence of the HC component severely accelerates the impact of NBTI and suppresses PBTI. If the impact of the fast trap component on the measurement results is suppressed, for some stress conditions, the long-term HCD data can be well fitted with the CET map model and also with the universal relaxation relation. This is similar to the case of BTI in both GFETs and Si technologies. As such, a systematic method for benchmarking new graphene technologies proposed in [18] has been extended to the case of HCD.

## ACKNOWLEDGMENT

The authors would like to thank D. Polyushkin, A. Pospischil, M. Furchi, S. Wagesreither, and A. Lugstein for the technical assistance and useful discussions.

#### REFERENCES

- [1] V. E. Dorgan, M.-H. Bae, and E. Pop, "Mobility and saturation velocity in graphene on SiO<sub>2</sub>," *Appl. Phys. Lett.*, vol. 97, no. 8, p. 082112, 2010.

- [2] A. K. Geim and K. S. Novoselov, "The rise of graphene," *Nature Mater.*, vol. 6, no. 3, pp. 183–191, 2007.

- [3] K. S. Novoselov et al., "Electric field effect in atomically thin carbon films," Science, vol. 306, no. 5696, pp. 666–669, 2004.

- [4] M. C. Lemme, T. J. Echtermeyer, M. Baus, and H. Kurz, "A graphene field-effect device," *IEEE Electron Device Lett.*, vol. 28, no. 4, pp. 282–284, Apr. 2007.

- [5] Y.-M. Lin, K. A. Jenkins, A. Valdes-Garcia, J. P. Small, D. B. Farmer, and P. Avouris, "Operation of graphene transistors at gigahertz frequencies," *Nano Lett.*, vol. 9, no. 1, pp. 422–426, 2009.

- [6] J. S. Moon et al., "Epitaxial-graphene RF field-effect transistors on Si-face 6H-SiC substrates," *IEEE Electron Device Lett.*, vol. 30, no. 6, pp. 650–652, Jun. 2009.

- [7] I. Meric, C. Dean, A. Young, J. Hone, P. Kim, and K. L. Shepard, "Graphene field-effect transistors based on boron nitride gate dielectrics," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2010, pp. 23.2.1–23.2.4.

- [8] S.-J. Han, Z. Chen, A. A. Bol, and Y. Sun, "Channel-length-dependent transport behaviors of graphene field-effect transistors," *IEEE Electron Device Lett.*, vol. 32, no. 6, pp. 812–814, Jun. 2011.

- [9] M. Engel et al., "Light–matter interaction in a microcavity-controlled graphene transistor," Nature Commun., vol. 3, Jun. 2012, Art. ID 906.

- [10] M. C. Lemme, L.-J. Li, T. Palacios, and F. Schwierz, "Two-dimensional materials for electronic applications," *MRS Bull.*, vol. 39, no. 8, pp. 711–718, 2014.

- [11] H. Yang et al., "Graphene barristor, a triode device with a gate-controlled Schottky barrier," Science, vol. 336, no. 6085, pp. 1140–1143, 2012.

- [12] S. A. Imam, S. Sabri, and T. Szkopek, "Low-frequency noise and hysteresis in graphene field-effect transistors on oxide," *IET Micro Nano Lett.*, vol. 5, no. 1, pp. 37–41, 2010.

- [13] B. Liu, M. Yang, C. Zhan, Y. Yang, and Y.-C. Yeo, "Bias temperature instability (BTI) characteristics of graphene field-effect transistors," in *Proc. Int. Symp. VLSI Technol.*, Syst. Appl., 2011, pp. 1–2.

- [14] W. J. Liu et al., "Vth shift in single-layer graphene field-effect transistors and its correlation with Raman inspection," *IEEE Trans. Device Mater.* Rel., vol. 12, no. 2, pp. 478–481, Jun. 2012.

- [15] W. J. Liu et al., "Observation of the ambient effect in BTI characteristics of back-gated single layer graphene field effect transistors," *IEEE Trans. Electron Devices*, vol. 60, no. 8, pp. 2682–2686, Aug. 2013.

- [16] S. E. Tyaginov, I. Starkov, H. Enichlmair, J. M. Park, C. Jungemann, and T. Grasser, "Physics-based hot-carrier degradation modeling," *ECS Trans.*, vol. 35, no. 4, pp. 321–352, 2011.

- [17] W. J. Liu et al., "Positive bias-induced V<sub>th</sub> instability in graphene field effect transistors," *IEEE Electron Device Lett.*, vol. 33, no. 3, pp. 339–341, Mar. 2012.

- [18] Y. Y. Illarionov et al., "Bias-temperature instability in single-layer graphene field-effect transistors," Appl. Phys. Lett., vol. 105, no. 14, p. 143507, 2014.

- [19] Y. Y. Illarionov et al., "Bias-temperature instability in single-layer graphene field-effect transistors: A reliability challenge," in Proc. IEEE Silicon Nanoelectron. Workshop (SNW), Jun. 2014, pp. 29–30.

- [20] D. K. Schroder, "Negative bias temperature instability: What do we understand?" *Microelectron. Rel.*, vol. 47, no. 6, pp. 841–852, 2007.

- [21] T. Grasser *et al.*, "Analytic modeling of the bias temperature instability using capture/emission time maps," in *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2011, pp. 27.4.1–27.4.4.

- [22] G. Pobegen, S. Tyaginov, M. Nelhiebel, and T. Grasser, "Observation of normally distributed energies for interface trap recovery after hot-carrier degradation," *IEEE Electron Device Lett.*, vol. 34, no. 8, pp. 939–941, Aug. 2013.

- [23] T. Grasser, W. Gös, V. Sverdlov, and B. Kaczer, "The universality of NBTI relaxation and its implications for modeling and characterization," in *Proc. 45th Annu. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2007, pp. 268–280.

- [24] T. Grasser et al., "Simultaneous extraction of recoverable and permanent components contributing to bias-temperature instability," in Proc. IEEE Int. Electron Devices Meeting (IEDM), Dec. 2007, pp. 801–804.

Yury Illarionov was born in Saint Petersburg, Russia, in 1988. He received the M.Sc. degree from Saint Petersburg State Polytechnic University, Saint Petersburg, in 2011, and the FAME Erasmus Mundus Program in 2012, and the Ph.D. degree from the Ioffe Physical-Technical Institute, Saint Petersburg, in 2015.

He joined the Institute for Microelectronics, Technische Universität Wien, Vienna, Austria, in 2013.

Anderson David Smith received the bachelor's and master's degrees in mechanical engineering from the Georgia Institute of Technology, and a second master's degree in nanotechnology from the KTH Royal Institute of Technology, Stockholm, Sweden, where he is currently pursuing the Ph.D. degree with the School of Information and Communication Technology.

His current research interests include graphene sensors and transistors for more and Moore applications.

**Thomas Mueller** received the M.Sc. and Ph.D. degrees in electrical engineering from Technische Universität Wien, Vienna, Austria, in 2001 and 2004, respectively.

He joined the IBM Research Center, Yorktown Heights, NY, USA, in 2007. He returned to Technische Universität Wien, in 2009, where he is currently an Assistant Professor. His current research interests include (opto)electronic using 2-D materials.

Sam Vaziri received the B.Sc. degree in solid-state physics from Shahid Beheshti University, Tehran, Iran, the M.Sc. degree in solid-state physics from the K. N. Toosi University of Technology, Tehran, and the M.Sc. degree in nanotechnology from the KTH Royal Institute of Technology, Stockholm, Sweden, in 2011, where he is currently pursuing the Ph.D. degree.

His current research interests include investigating graphene electronic and optoelectronic devices.

Max C. Lemme (M'00–SM'06) received the Dipl.Ing. and Dr.Ing. degrees in electrical engineering from RWTH Aachen University, Aachen, Germany.

He was a Research Fellow with Harvard University, Cambridge, MA, USA, from 2008 to 2010. He is currently a Heisenberg Professor of Graphene-Based Nanotechnology with the University of Siegen, Siegen, Germany, and an Associate Professor with the KTH Royal Institute of Technology, Stockholm, Sweden.

Mikael Östling has been a Visiting Professor with Stanford University, Stanford, CA, USA, and the University of Florida, Gainesville, FL, USA. He was the Dean of the School of Information and Communication Technology with the KTH Royal Institute of Technology, Stockholm, Sweden, where he is currently a Professor of Solid-State Electronics and the Department Head.

Mr. Östling is the Vice President of the IEEE Electron Device Society.

**Tibor Grasser** is currently an Associate Professor with Technische Universität Wien, Vienna, Austria. He has co-authored or authored over 500 scientific articles and edited books on *Advanced Device Simulation*, *Bias-Temperature Instability* (Springer).

Prof. Grasser has received a number of prestigious Best Paper Awards, including the 2011 IEEE EDS Paul Rappaport Award.