## A Systematic Study of Charge Trapping in Single-Layer Double-Gated GFETs

Yu. Yu. Illarionov<sup>1,2</sup>, G. Rzepa<sup>1</sup>, M. Waltl<sup>1</sup>, H. Pandey<sup>3</sup>, S. Kataria<sup>3</sup>, V. Passi<sup>3</sup>, M.C. Lemme<sup>3</sup>, and T. Grasser<sup>1</sup>

<sup>1</sup>Institute for Microelectronics (TU Wien), Gusshausstrasse 27–29, 1040 Vienna, Austria <sup>2</sup> Ioffe Physical-Technical Institute, Polytechnicheskaya 26, 194021 St-Petersburg, Russia <sup>3</sup>University of Siegen, Holderlinstrasse 3, 57076 Siegen, Germany Email: illarionov@iue.tuwien.ac.at/Phone: +4315880136035

ing/discharging of oxide traps.

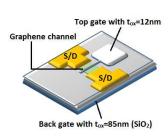

**Devices:** In our single-layer double-gated GFETs (L = $3-6 \mu m$ ) the CVD graphene channel [10] is sandwiched between thermally oxidized SiO<sub>2</sub> as a back gate oxide  $(t_{ox} = 85 \text{ nm})$  and e-beam evaporated SiO<sub>2</sub> as a top gate oxide ( $t_{ox} = 12 \text{ nm}$ ), see Fig. 1. The source/drain pads are made of a thermally evaporated Cr(20nm)/Au(80nm) stack and the top gate contact is 120nm thick Al.

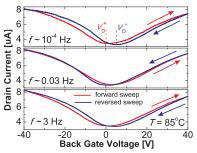

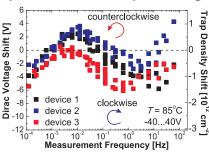

**Experiment:** In the spirit of [5], our measurements were performed in a vacuum ( $\sim 5 \times 10^{-6}$  torr). The hysteresis was investigated by measuring the back gate transfer  $(I_{\rm d}$ - $V_{\rm bg})$  characteristics at  $V_{\rm d}$  = 0.1 V. By using different step voltages  $V_{\text{step}}$  and sampling times  $t_{\text{step}}$ , we have varied the measurement frequency  $f=1/(N \cdot t_{\text{step}})$  with  $N=2((V_{\text{bgmax}} - t_{\text{bgmax}}))$  $V_{\text{bgmin}}$ )/ $V_{\text{step}}$ +1) between 10<sup>-4</sup> and 10<sup>2</sup> Hz. This allowed us to demonstrate that the dependence of the Dirac point voltage shift  $\Delta V_D = V_D^+ - V_D^-$  versus f presents a unique fingerprint of the hysteresis dynamics. For a reliable determination of the hysteresis origin, we have measured the  $\Delta V_{\rm D}(f)$ at  $T = 85^{\circ}$ C and  $T = 165^{\circ}$ C.

Fig. 4 we show that the  $I_d$ - $V_{bg}$  characteristics exhibit a ther evidences the contribution of top gate defects. clockwise hysteresis for low and high f, while a counterfor different devices. Namely,  $\Delta N_{\rm T}$  becomes positive and is dominated by thermally activated oxide traps.

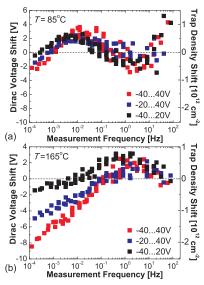

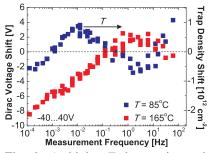

**Introduction:** Graphene is a honeycomb carbon mareaches a maximum at  $f \sim 10^{-3}$ – $10^{-2}$  Hz. In Fig. 6 we terial which is now successfully applied as a channel in demonstrate that at higher T the  $\Delta N_{\rm T}(f)$  dependence is graphene FETs (GFETs) [1–5]. However, stability of shifted towards higher f, which is consistent with thermodern GFETs is limited by a considerable hysteresis on mally activated charging/discharging processes. Namely, the gate transfer characteristics [3]. Although several stud- at low f discharging of back gate oxide defects is domiies on this issue have been reported [3,6–9], different phys-nant, leading to a negative  $\Delta N_T$ , an effect which becomes ical explanations have been put forward. Here we intro- larger at higher T and decreases for higher f. Although duce an experimental technique allowing for a systematic for very fast sweeps  $\Delta N_T$  should simply reach zero, we study of the hysteresis in GFETs and show that in our de- observe a change of the  $\Delta N_T$  sign while passing through a vices this issue is dominated by thermally activated charg-maximum. This is likely due to thermally activated charging of the defects situated in the top gate oxide, which introduces additional positive charges. Interestingly, in some cases at  $T = 85^{\circ}$ C there is a second reversal of the trend of the hysteresis at very high f, which suggests a charging of the top gate defects with smaller time constants.

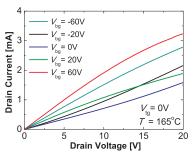

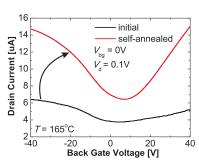

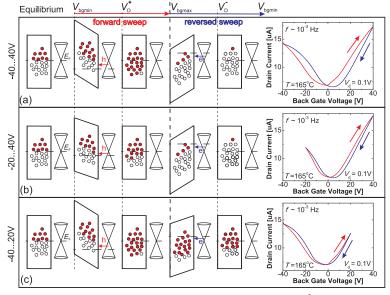

In Fig. 7 we show that the  $\Delta V_D(f)$  dependences are affected by the sweep range in their low f branch, especially at T = 165°C. This behaviour can be understood based on Fig. 8. At  $V_{\text{bgmin}} = -40 \text{ V}$  the Fermi level  $E_{\text{F}}$  is close to the back gate oxide valence band. Hence, for low f most of the defects are charged before  $V_{\text{bg}} = V_{\text{D}}^{+}$  is reached. Then, a significant fraction of them is either discharged when  $V_{\text{bgmax}} = 40 \,\text{V}$  is reached or continue to discharge during the reversed sweep. As a result, the amount of charged traps at  $V_{\text{bg}} = V_{\text{D}}^{-}$  is much smaller than it was at  $V_{\text{bg}} = V_{\text{D}}^{+}$ (Fig. 8a), leading to a large clockwise hysteresis. However, if  $V_{\text{bgmin}} = -20 \,\text{V}$ , the initial  $E_{\text{F}}$  lies higher and the time spent in the hole conduction region is smaller. Hence, the concentration of charged defects at  $V_{\text{bg}} = V_{\text{D}}^{+}$  is reduced (Fig. 8b). Thus, although sweeping till  $V_{bgmax} = 40 \,\mathrm{V}$  and dependences using different sweep ranges  $V_{\text{bgmin}} \dots V_{\text{bgmax}}$  back to  $V_{\text{bg}} = V_{\text{D}}^-$  discharges most of them, the observed hysteresis is smaller. Finally, for  $V_{\text{bg}} = -40...20 \text{ V}$  (Fig. 8c) **Results and Discussions:** The output  $(I_d-V_d)$  charact the amount of charged defects at  $V_{bg} = V_D^+$  is only insignifteristics of our GFETs (Fig. 2) show some signs of saticantly larger than at  $V_{\text{bg}} = V_{\text{D}}^{-}$ , since a low  $V_{\text{bgmax}}$  does not uration for larger  $V_d$  and  $V_{bg}$ . At the same time, the  $I_d$ - allow for efficient discharging. Hence, only a very small  $V_{\rm bg}$  characteristics (Fig. 3) exhibit an improvement after hysteresis is visible. Obviously, at lower T both charging the  $I_{\rm d}$ - $V_{\rm d}$  sweeps. The latter is attributed to self-annealing and discharging are less efficient, making the difference of graphene at high  $I_d$  [11], which allowed us to achieve smaller (Fig. 7a). At the same time, a weak impact of the a better reproducibility of all further measurements. In  $V_{\rm bg}$  sweep range on  $\Delta V_{\rm D}(f)$  right from the maximum fur-

**Conclusions:** We have suggested an experimental clockwise hysteresis is observed for moderate f (cf. [6,7]), technique allowing for a simple and systematic bench-As shown in Fig. 5, the resulting charged trap density marking of the hysteresis in GFETs. Using this technique shift  $\Delta N_{\rm T} = C_{\rm bg} \Delta V_{\rm D}/q$  versus f is qualitatively similar allowed us to demonstrate that in our GFETs the hysteresis

[1] M. Lemme et al., EDL 28, 282 (2007). [2] J. Moon et al., T-ED 30, 650 (2009). [3] S. Imam et al., Micro & Nano Lett. 5, 37 (2010). [4] M. Engel et al., Nat. Commun. 3, 906 (2012). [5] W. Liu et al., T-ED 60, 2682 (2013). [6] H. Wang et al., ACS Nano 4, 7221 (2010). [7] Z.-M. Liao et al., JCP 133, 044703 (2010). [8] Y. Lee et al., APL 98, 183508 (2011). [9] M. Winters et al., JAP 117, 074501 (2015). [10] S. Kataria et al., Phys.SS(RRL) 211, 2439 (2014). [11] J. Moser et al., APL 91, 163513 (2007).

Fig. 1: Schematic layout of our single-layer double gated GFETs. S/D pads are made of Au/Cr and the top gate contact of Al.

Fig. 4: The  $I_{\rm d}$ - $V_{\rm bg}$  characteristics exhibit a hysteresis which reverses at moderate measurement frequency f. We express the hysteresis width as a Dirac voltage shift  $\Delta V_{\rm D} = V_{\rm D}^+ - V_{\rm D}^- = q \Delta N_{\rm T}/C_{\rm bg}$ .

Fig. 7: The  $\Delta V_{\rm D}(f)$  dependences measured at  $T=85^{\circ}{\rm C}$  (a) and  $165^{\circ}{\rm C}$  (b) using different sweep ranges. At higher T the low f part is more sensitive to the sweep range, since charging/discharging of the back gate oxide traps is more efficient.

Fig. 2: Output  $(I_d-V_d)$  characteristics measured at different back gate voltages exhibit a linear region and some signs of saturation for large  $V_d$  and  $V_{bg}$ .

Fig. 5: The hysteresis width versus the measurement frequency  $f = 1/(N \cdot t_{\text{step}})$  obtained for different devices exhibits a maximum, around which the hysteresis changes sign. This is likely due to charging of top gate defects.

Fig. 3: The back gate transfer ( $I_{\rm d}$ - $V_{\rm bg}$ ) characteristics dramatically improve after  $I_{\rm d}$ - $V_{\rm d}$  sweeps. This is due to self-annealing of graphene at high  $I_{\rm d}$ .

Fig. 6: At higher T the maximum is shifted towards higher f, i.e. the time constants of both charging/discharging of traps in the back gate oxide and charging of their counterparts in the top gate oxide become smaller.

Fig. 8: The hysteresis dynamics at  $T = 165^{\circ}\text{C}$  and  $f = 10^{-3}\,\text{Hz}$ . (a) For  $V_{\text{bg}} = -40...40\,\text{V}$  the time constants of most defects are small compared to the total sweep time. Hence, they can be charged/discharged and the hysteresis is large. (b) For  $V_{\text{bg}} = -20...40\,\text{V}$  only a limited number of traps will be charged in the hole conduction region. Hence, their discharging will lead to a smaller hysteresis. (c) Finally, for  $V_{\text{bg}} = -40...20\,\text{V}$  the amount of charged traps is large, but most of them will not discharge, leading to the smallest hysteresis.