# Nanoscale Evidence for the Superior Reliability of SiGe High-k pMOSFETs

M. Waltl\*, A. Grill\*,<sup>⋄</sup>, G. Rzepa\*, W. Goes\*, J. Franco<sup>†</sup>, B. Kaczer<sup>†</sup>, J. Mitard<sup>†</sup>, and T. Grasser\*

\* Institute for Microelectronics, TU Wien, Vienna, Austria Phone: +43-1-58801/36050, Fax: +43-1-58801/36099, Email: {waltl|grasser}@iue.tuwien.ac.at

Christian Doppler Laboratory at the Institute for Microelectronics, TU Wien, Vienna, Austria

† imec, Leuven, Belgium

Abstract—It is commonly accepted that the susceptibility of conventional Si channel pMOSFETs to the negative bias temperature instability (NBTI) is a serious threat to further scaling. One possible solution of this problem is the use of SiGe quantum-well devices, which not only offer high mobilities but also superior NBTI reliability compared to conventional silicon transistors. It has been speculated that the latter is due to the energetically higher valence band edge of the SiGe channel with respect to Si, which increases the energetic separation between the defect bands in the high-k gate stack and the channel. We investigate this claim by comparing the behavior of single-defects in nanoscale devices to the averaged behavior of the large number of defects visible in large-area devices. Using detailed TCAD simulations together with the four-state non-radiative multiphonon model we determine the energetic and spatial locations of the traps in the gate stack and confirm that the previously developed picture correctly explains the significant reliability benefits of SiGe channel devices.

### I. INTRODUCTION

The lifetime of nanoscale transistors is seriously affected by bias temperature instabilities (BTI). Single defects located inside the gate dielectrics can capture/emit electrons or holes and as a consequence modulate the surface potential within the conducting channel. The resulting reduction in the drain-source current is harmful to the operation of CMOS circuits. In order to compare charge trapping for different technologies, the impact of charge capture/emission on the drain-source current is commonly converted into an equivalent threshold voltage shift.

The aggressive scaling towards smaller devices has led to metal-oxide-semiconductor transistors (MOSFETs) with geometrical dimensions of several tens of nanometers. In general, the thinner the gate insulator becomes, the larger the gate leakage currents will be. To obtain physical thin gate oxides and at the same time avoid high leakage currents, high-k gate stacks have been introduced [1–4]. In modern devices the gate dielectric often consists of an HfO<sub>2</sub>/SiO<sub>2</sub> (HK/IL) stack which is contacted with a metal gate (MG).

Nonetheless, in high-k MOSFETs BTI still remains a severe reliability issue. Recent investigations have shown that the detrimental impact of NBTI on device performance of high-k pMOSFETs can be significantly reduced using SiGe channels [5–8]. The SiGe channel devices have been initially introduced to exploit the higher mobility of the SiGe channel compared to conventional Si channel devices. At the same time, a

significantly improved reliability with respect to NBTI has been observed. Apparently counter-intuitively, it was found that devices with a very thin Si cap layer on top of the SiGe channel resulted in the best reliability performance, suggesting that the crucial role of the Si cap is not to act as a tunneling barrier for channel holes, but instead to enable the fabrication of a high-quality SiO<sub>2</sub> interfacial layer [9]. It has been previously speculated that this reliability boost is a result of the favorable energetic alignment of the SiGe channel with respect to the defect band in the high-k gate stack. Compared to Si devices, the valence band in the SiGe channel is energetically higher, resulting in a smaller overlap with the defect states and thus reduced charge trapping.

In nanoscale transistors just a handful of defects are present. Thus the contribution of a single-trap to the threshold voltage shift can be studied individually. For that the time-dependent defect spectroscopy (TDDS) has been recently proposed [10–12]. Although the TDDS has been used to study single defects in SiON MOSFETs [10–13], less focus has been put on HK devices [14–16]. In contrast to nanoscale transistors, in large area devices the average contribution of a large number of defects to the threshold voltage shift can be studied.

To understand and model the observed recovery of pMOS-FETs subjected to NBTI stress, the non-radiative multiphonon (NMP) model is often used [17, 18]. So far, the NMP model has been successfully used to explain the complex bias dependence of the capture/emission times of single-traps together with their temperature dependence in SiON MOSFETs [10, 13, 19, 20].

First we use nanoscale SiGe pMOSFETs and extract 19 single-traps by applying the TDDS to devices with two different Si cap layer thicknesses and reference Si transistors. From the recovery traces we calculate the cumulative complementary distribution function (CCDF) of step heights and show that unimodal and bimodal CCDFs are obtained for our SiGe quantum-well transistors, depending on the Si cap thickness. In addition to that we record recovery traces from large area devices using an extended measure-stressmeasure (eMSM) scheme [21]. Afterwards we use the NMP model to reproduce the bias and temperature dependent capture/emission time characteristics of our single-traps and the recovery data recorded on the large area devices. All detailed TCAD simulations are performed with our device simulator

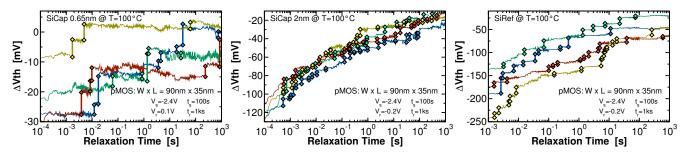

Fig. 1: The emission events of individual defects are clearly visible in the recovery traces of our nanoscale transistors. As can be seen in the recovery traces the number of traps accessible, i.e. the trap density, increases with larger SiCap layer thickness (left:  $d_{\rm SiCap} = 0.65 \, \rm nm$  and middle:  $d_{\rm SiCap} = 2 \, \rm nm$ ). The largest threshold voltage shift, however, is observed from the reference device (right). First we investigate the devices with the thin Si cap layer where a particularily high stress bias of  $V_{\rm G}^{\rm s} = -2.4 \, \rm V$  has to be used to observe a measureable degradation (left). To achieve comparable results the recovery traces of the two other device variants are recorded after the transistors have been subjected to the same NBTI stress.

MINIMOSNT [22]. Both our experimental data as well as our theoretical analysis clearly demonstrate for the first time that the *energetical favorable alignment of the defect band to the SiGe layer caused by the Si cap layer* is indeed responsible for the superior reliability of SiGe devices.

# II. EXPERIMENTAL DETAILS

To study the impact of NBTI on SiGe p-channel transistors we focus on structures with two different Si cap thicknesses of  $d_{\rm SiCap} = 0.65\,{\rm nm}$  and  $d_{\rm SiCap} = 2\,{\rm nm}$  between the HfO<sub>2</sub>/SiO<sub>2</sub> gate stack and the SiGe layer [9]. First we investigate nanoscale pMOSFETs with a gate width of  $W=90\,\mathrm{nm}$ and a gate length of  $L=35\,\mathrm{nm}$ . We note that all three device technologies have different threshold voltages. The reference Si devices have the most negative threshold voltage  $V_{\rm th} = -217\,{\rm mV}$  and the devices with the thin Si Cap the most positive  $V_{\rm th} = 245\,\mathrm{mV}$  (the devices with the thick Si cap layer have  $V_{\rm th} = 24\,{\rm mV}$ ). To ensure comparable oxide fields during recovery, the recovery gate bias is determined individually for each device in such a way that all devices see the same overdrive voltage during recovery. This is achieved by setting the recovery bias to the gate voltage which causes a drainsource current of  $I_{\rm DS}=-1\,\mu{\rm A}$  at  $V_{\rm DS}=-100\,{\rm mV}$ . Typical recovery traces of all three technologies recorded after NBTI stress with  $V_{\rm G}^{\rm s} = -2.4\,{\rm V}$  are shown in Figure 1. As can be seen, for nanoscale devices the emission events in the recovery traces are visible as discrete steps, i.e. the recovery proceeds in discrete emission events. Each particular step corresponds to a charge exchange with either the substrate or the MG. For each technology an average contribution of a single trap to the total threshold voltage shift  $\eta$  can be extracted. The analysis of the recovery traces reveals that with increasing Si cap layer thickness the number of active traps increases, as can be seen when the recovery traces for the device with the thin Si cap layer shown in Figure 1 (left) and the traces from the device with the thick Si cap layer Figure 1 (middle) are compared. The number of defects present for a certain technology is given by the number of traps  $N_{\rm T}$ . Among the studied device variants the reference devices without a SiGe channel show the largest number of active traps visible, see Figure 1 (right). From this

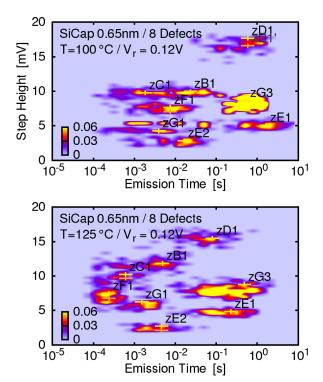

Fig. 2: Employing SiGe pMOSFETs with the thinnest SiCap layer we identified 8 defects at  $T=100^\circ$  (top) and  $T=125^\circ$  (bottom). The step heights of the defects are found widely distributed from  $\Delta V_{\rm th}\approx 3\,{\rm mV}$  up to  $\Delta V_{\rm th}\approx 17\,{\rm mV}$ . In order to keep the experimental effort for the TDDS within reasonable limits, only fast traps with  $\tau_{\rm e}<1\,{\rm s}$  are studied here. In line with previous single-trap studies of BTI in SiON [10,11,13] and high-k devices [16] the defects move towards lower emission times at higher temperatures due to the thermally activated nature of charge trapping.

observation it follows that even with a thick Si cap layer the use of a SiGe channel results in a considerable reliability boost with respect to NBTI. A particularly interesting observation is that although the largest overdrive voltage during stress was applied to the devices with the thinnest Si cap layer (because they have the smallest  $V_{\rm th}$ ), their absolute  $\Delta V_{\rm th}$  is still the smallest compared to the other pMOSFETs. Furthermore, a considerable stress bias has to be used to achieve a measurable degradation of the SiGe pMOSFETs.

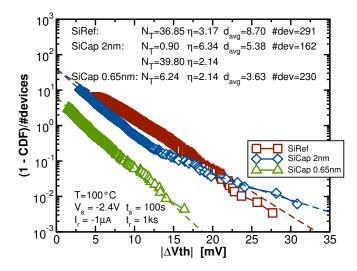

Fig. 3: The recovery traces of more than 600 devices have been analyzed to determine the complementary CDF. A unimodal CCDF is obtained for the devices with the thinnest Si cap layer and for the reference devices. In contrast, the devices with the thick Si cap layer show bimodally distributed step heights. Quite remarkably, the CCDFs obtained from the SiGe pMOSFETs have similar values for the average contribution of a single trap  $\eta$  for step heights smaller than approximately 12~mV. It has to be noted that when the CCDF is normalized to the number of devices the number of traps per single device is directly visible at the ordinate at  $|\Delta V_{\text{th}}| = 0~\text{V}$ . As can be seen, the devices with the thin Si cap layer have the smallest  $N_{\text{T}}$  compared to the other two technologis.

Using the TDDS we identified 19 single defects among all our DUTs. To study a certain trap, 100 recovery traces are recorded at the same stress/recovery times and biases and at the same device temperature. Afterwards, the traces are thoroughly analyzed [10, 12, 18, 20] and the discrete steps and emission times are collected in the emission time vs. step height plane  $(\tau_e, d)$ , called spectral map. Withing a spectral map the single-traps form clusters, which are the fingerprints of each individual defect. The eight traps we analyzed in detail from the devices with the thin Si cap layer show step heights from  $d \approx 3 \, \text{mV}$  up to  $d \approx 17 \, \text{mV}$ , see Figure 2. As can be seen from the spectral maps, the single-traps move towards lower emission times with increasing device temperature, an observation which is in agreement with single-trap studies on SiON and high-k MOSFETs [10, 13, 16, 20].

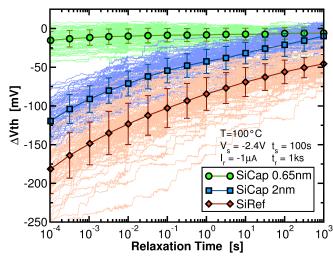

Contrary to their nanoscale counterparts, the large area pMOSFETs ( $W=L=1\,\mu\mathrm{m}$ ) show a continuous recovery behavior. The average recovery is a result of the contribution of a large number of defects to the net device degradation. Using an eMSM scheme, the impact of different stress times and stress biases has been studied. It has to be noted that for an increasing device area  $A=W\times L$  a smaller average contribution of a single charge  $\eta_{\mathrm{um}}=\eta_{\mathrm{nm}}/A$  is obtained. In contrast, the trap density increases together with increasing device area  $N_{\mathrm{T,um}}=A\times N_{\mathrm{T,nm}}$ .

Fig. 4: The average threshold voltage shift  $\Delta V_{\rm th}$  of the traces used to calculate the CCDF from Figure 3. The largest  $\Delta V_{\rm th}$  shift is observed for the reference Si transistor. A smaller sensitivity with respect to NBTI stress is found for the devices with  $d_{\rm SiCap}=2\,{\rm nm}$ . The transistors with  $d_{\rm SiCap}=0.65\,{\rm nm}$  show the smallest  $\Delta V_{\rm th}$  shift when subjected to NBTI stress.

## III. SINGLE DEFECTS

The CCDFs in Figure 3 shows unimodally distributed step heights for the reference Si device and the devices with  $d_{\rm SiCap} = 0.65 \, \rm nm$ . Quite remarkably, a significant smaller value for the average contribution of a single trap  $\eta$  is observed for devices with the thin Si cap layer compared to the reference pMOSFETs, with  $\eta_{0.65\mathrm{nm}} = 2.14 < \eta_{\mathrm{ref}} = 3.14$ . On average, the smaller the observed step height, the farther away the trap is located from the channel. In the case of the SiGe pMOSFETs it has to be considered that the conducting channel is located in the SiGe layer which is farther away from the IL due to the additional cap layer with thickness  $d_{\rm SiCap} = 0.65\,{\rm nm}.$  We thus conclude that the small value for  $\eta_{0.65\mathrm{nm}}$  is a consequence of charge trapping between the gate stack and the conducting channel which is dominantly located inside the SiGe layer. This claim is confirmed by our quantum-mechanical simulations. In contrast to the previously mentioned CCDFs, the step heights of the devices with a Si cap of  $d_{SiCap} = 2 \,\mathrm{nm}$  appear bimodally distributed. This suggests the presence of two conducting channels with the first one located at the SiO<sub>2</sub>/SiCap interface and the second one in the SiGe layer. This assumption is supported by the observation that the first part of the bimodal CCDF shows the same value for the average contribution of a single trap  $\eta$  as obtained for the unimodal CCDF for the devices with the thin Si cap layer. Therefore, we link the low  $\eta$  bulk of the bimodal CCDF to traps interacting with the channel in the SiGe. The high  $\eta$  tail of the CCDF is a superposition of step heights from traps interacting with the channel at the SiO<sub>2</sub>/SiCap interface and with the channel in the SiGe. When thinning the SiCap layer, the current flow is more dominantly located in the SiGe and thus the bimodal CCDF turns into a unimodal one. The

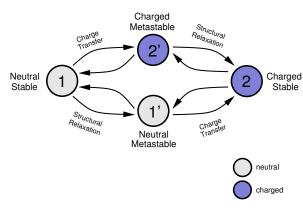

Fig. 5: The four-state NMP model is used to describe the response of the capture and emission times of single defects to varying biases and temperatures. In general, the model considers two stable states 1 (neutral) and 2 (charged) and two meta-stable states 1' and 2'. These states are required for an accurate description of the bias-dependent and bias-independent capture and emission times as well as other features [10]

extracted number of traps per device  $N_{\rm T}$  is in agreement with the recovery traces shown in Figure 1. As can be seen, the devices with the thin Si cap layer have a smaller number of active traps  $N_{\rm T,0.65nm}=6.24$ . Significantly more pronounced charge trapping is obtained for the two other technologies, resulting in a larger number of traps per device.

The average recovery traces from Figure 4 are calculated from the traces recorded to create the CCDF. As can be seen, the reference devices show the largest threshold voltage shift whereas the devices with the thin Si cap layer have the smallest response to NBTI stress. It has to be noted that the threshold voltage shift remaining at the end of the recovery traces ( $t_{\rm r}=1\,{\rm ks}$ ) strongly depends on the device technology and thus on  $N_{\rm T}$ . The larger  $N_{\rm T}$ , the larger the remaining threshold voltage shift. A negligible  $\Delta V_{\rm th}$  remains at the end of the traces for the thin Si cap device a noticeable value for  $\Delta V_{\rm th}$  is found for the reference devices after  $t_{\rm r}=1\,{\rm ks}$ .

# IV. MODELING AND SIMULATION

To properly capture the device electrostatics and the carrier concentrations inside the SiGe channel, we calibrate our Schrödinger Poisson solver VSP [23] to experimental C(V) characteristics of all three different device structures [24]. With the geometrical dimensions and dopings obtained from the quantum-mechanical simulations, our device simulator MINIMOSNT [22] is used to reproduce the corresponding  $I_{\rm D}(V_{\rm G})$  characteristics. Then the hole capture and emission transition rates are calculated using our four-state NMP model (NMP) [18].

Initially, the NMP model was developed around the oxygen vacancy which is the most prominent defect in silica. Recently, considerably better agreement between DFT and experiment was obtained for the hydroxyl E' center, a variant of this defect [19]. The model uses metastable states to cover the *switching traps* with bias-dependent emission times (via state 1') and the *fixed traps* bias-independent emission times (via state 2'), see

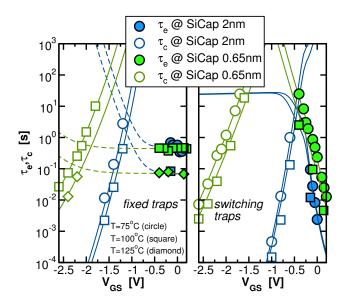

**Fig. 6:** The capture and emission times of single-traps characterized from our SiGe pMOSFETs plotted versus the stress/recovery biases at different device temperatures. As can be seen, *fixed hole traps* (**left**) with bias independent emission times and *switching traps* (**right**) with their typical bias dependent emission time behavior are found in all device variants. All the observed capture and emission time characteristics and their temperature dependence are well reproduced by our simulations using the four-state NMP model (lines).

Figure 5. To properly reproduce the trapping behavior of our SiGe pMOSFETs, charging and discharging interactions with the channel at the  $SiO_2/SiCap$  interface and with the SiGe channel have to be considered.

Among our 19 studied single-traps we found fixed oxide traps and switching oxide traps, both shown in Figure 6. As can be seen, the fixed and switching trap capture/emission time characteristics and their temperature dependence is well explained by our four-state NMP model.

# V. RESULTS AND DISCUSSION

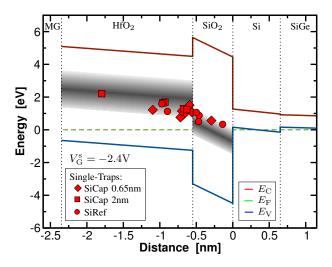

In addition to nanoscale SiGe pMOSFETs we also characterized the recovery of large area DUTs with W = L = $1 \, \mu \text{m}$ . The continuous recovery of these devices reflect the average contribution of a large number of traps with widely distributed capture/emission times and different step heights. Based on the NMP model parameters from the presented single trap investigations, an NMP trap distribution is calculated and utilized to reproduce the recovery. Consistently with our single-trap investigations, the recovery behavior of our large area devices of all three different technologies recorded after NBTI stress with different stress times and stress voltages can be reproduced using the four-state NMP model. Quite remarkably, this was achieved with the same set of trap parameters for the recoverable component. As a consequence we interpret the difference in the trapping kinetics and the number of electrically active traps as a consequence of the different energetic alignment of the gate stack with the active channel. The band-diagram from Figure 7 depicted for stress

**Fig. 7:** The band-diagram under stress bias conditions shows the traps identified in the nanoscale devices marked with symbols. The trap bands in the HK and the IL show the energetical distribution of the traps used to to explain the recovery of *all the large-area* devices. Furthermore, this has been achived with just one paramterset.

bias conditions shows the trap energy band used to explain the recovery of the large area transistors together with the trap depth and energetic position of the 19 identified individual traps. Performing detailed TCAD simulations we have observed that for large-area devices the recovery behavior is not very sensitive to the energetical position of the trap band in the HK. So the recoverable component is primilary dominated by traps present in the IL. Nonetheless, the mean value of the trap energy band for the HK and the IL used in our simulations are fully consistent with investigations of other groups [25].

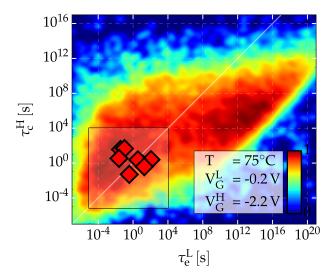

As stated above, the recovery of the large area devices can be reproduced for all three different technologies by using the same set of NMP model parameters. From this parameter set we have calculated the capture emission time (CET) map for the devices with the thin Si cap layer, see Figure 8. In addition, the capture and emission times obtained from the eight single traps are also marked in the CET map. As can be seen, the single traps observed have capture/emission times lying well inside the simulated CET distribution.

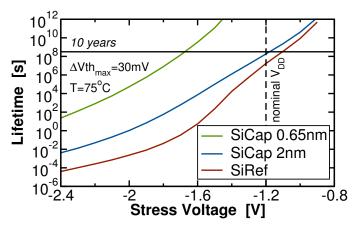

Finally, the device lifetimes of the SiGe and reference Si devices are extrapolated. Using our calibrated model the dependence of the device lifetimes on the stress voltage is calculated, see Figure 9. As expected, the SiGe devices with the thinnest Si cap provide a superior lifetime, easily outperforming the Si reference device.

# VI. CONCLUSIONS

In a detailed study we have compared NBTI in nanoscale and large-area SiGe pMOS transistors. We have characterized 19 single defects and found the trap levels and positions to be independent of the device structure. This implies that the gate stacks are similar in all technologies and that the reliability

Fig. 8: The CET map is obtained from our simulations and shows the capture/emission time distribution from the defect ensemble from Figure 7 used to reproduce the recovery behavior of the large area devices with the thin Si cap layer. For the capture times the values are calculated at gate stress bias  $V_{\rm G}^{\rm H}$  (denoted with superscript 'H') and the emissions times are extracted at recovery gate bias  $V_{\rm G}^{\rm L}$  (denoted with superscript 'L'). The datapoints are extracted from our single-trap investigation lie well inside the distribution. Also visible is the measurement window with  $\tau_{\rm e}, \tau_{\rm c} \in [10~\mu{\rm s}, 10~{\rm ks}]$  which marks the area of capture/emission times which can be accessed by eMSM measurements.

**Fig. 9:** Based on the unified model the lifetime of all three technologies can be estimated and is shown against the applied gate bias. At the nominal operating voltage of  $V_{\rm DD}=-1.2\,\rm V$  a lifetime of more than 10 years is easily achieved for the SiGe devices.

benefits must be primarily a result of the combination of channel material and gate stack. By comparing the single-defect data with the average response of a large ensemble of defects, both experimentally as well as in TCAD simulations we could therefore demonstrate that the superior lifetime of SiGe devices with a thin Si cap layer is indeed due to the favorable energetic alignment of the defect band in the oxide with the channel.

#### VII. ACKNOWLEDGEMENT

The research leading to these results has received funding from the Austrian Science Fund (FWF) project n°26382-N30, the European Community's FP7 project n°619234 (MoRV), as well as the Intel Sponsored Research Project n°2013111914. Furthermore, this work has been performed in part in the frame of the imec Core Partner program on Ge-based devices.

### REFERENCES

- G.D. Wilk, R.M. Wallace, and J.M. Anthony, "High-K Gate Dielectrics: Current Status and Materials Properties Considerations," *J. Appl. Phys.*, vol. 89, jan 2001.

- [2] J. Robertson, "High Dielectric Constant Oxides," Eur. Phys. J. Appl. Phys., vol. 28, pp. 265–291, 12 2004.

- [3] H.L. Byoung, K. Laegu, Q. Wen-Jie, N. Renee, J. Yongjoo, O. Katsunori, and J.C. Lee, "Ultrathin Hafnium Oxide with Low Leakage and Excellent Reliability for Alternative Gate Dielectric Application," in *Proc. Intl. Electron Devices Meeting (IEDM)*, Dec 1999, pp. 133–136.

- [4] E.P. Gusev, D.A. Buchanan, E. Cartier, A. Kumar, D. DiMaria, S. Guha, A. Callegari, S. Zafar, P.C. Jamison, D.A. Neumayer, M. Copel, M.A. Gribelyuk, H. Okorn-Schmidt, C. D'Emic, P. Kozlowski, K. Chan, N. Bojarczuk, L.-A. RagnarssonAND P. Ronsheim, K. Rim, R.J Fleming, A. Mocuta, and A. Ajmera, "Ultrathin High-K Gate Stacks for Advanced CMOS Devices," in *Proc. Intl. Electron Devices Meeting (IEDM)*, Dec 2001, pp. 20.1.1–20.1.4.

- [5] S. Deora, A. Paul, R. Bijesh, J. Huang, G. Klimeck, G. Bersuker, P.D. Krisch, and R. Jammy, "Intrinsic Reliability Improvement in Biaxially Strained SiGe p-MOSFETs," *IEEE Electron Device Lett.*, vol. 32, no. 3, pp. 255–257, March 2011.

- [6] S. Krishnan, U. Kwon, N. Moumen, M.W. Stoker, E.C.T. Harley, S. Bedell, D. Nair, B. Greene, W. Henson, M. Chowdhury, D.P. Prakash, E. Wu, D. Ioannou, E. Cartier, M.-H. Na, S. Inumiya, K. McStay, L. Edge, R. Iijima, J. Cai, M. Frank, M. Hargrove, D. Guo, A. Kerber, H. Jagannathan, T. Ando, J. Shepard, S. Siddiqui, M. Dai, H. Bu, J. Schaeffer, D. Jaeger, K. Barla, T. Wallner, S. Uchimura, Y. Lee, G. Karve, S. Zafar, D. Schepis, Y. Wang, R. Donaton, S. Saroop, P. Montanini, Y. Liang, J. Stathis, R. Carter, R. Pal, V. Paruchuri, H. Yamasaki, J.-H. Lee, M. Ostermayr, J.-P. Han, Y. Hu, M. Gribelyuk, D.-G. Park, X. Chen, S. Samavedam, S. Narasimha, P. Agnello, M. Khare, R. Divakaruni, V. Narayanan, and M. Chudzik, "A manufacturable dual channel (Si and SiGe) high-k metal gate CMOS technology with multiple oxides for high performance and low power applications," in *Proc. Intl. Electron Devices Meeting (IEDM)*, Dec 2011, pp. 28.1.1–28.1.4.

- [7] P. Srinivasan, J. Fronheiser, K. Akarvardar, A. Kerber, L.F. Edge, R.G. Southwick, E. Cartier, and H. Kothari, "SiGe composition and thickness effects on NBTI in replacement metal gate high-k technologies," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, June 2014, pp. 6A.3.1–6A.3.6.

- [8] J. Franco, B. Kaczer, P.J. Roussel, J. Mitard, C. Moonju, L. Witters, T. Grasser, and G. Groeseneken, "SiGe Channel Technology: Superior Reliability Toward Ultrathin EOT Devices – Part I: NBTI," *IEEE Trans. Electron Devices*, vol. 60, no. 1, pp. 396–404, Jan. 2013.

- [9] J. Franco, B. Kaczer, M. Toledano-Luque, P.J. Roussel, T. Kauerauf, J. Mitard, L. Witters, T. Grasser, and G. Groeseneken, "SiGe Channel Technology: Superior Reliability Toward Ultra-Thin EOT Devices Part II: Time-Dependent Variability in Nanoscaled Devices and Other Reliability Issues," *IEEE Trans.Electron Devices*, vol. 60, no. 1, pp. 405–412, Jan. 2013.

- [10] T. Grasser, H. Reisinger, P.-J. Wagner, F. Schanovsky, W. Goes, and B. Kaczer, "The Time Dependent Defect Spectroscopy (TDDS) for the Characterization of the Bias Temperature Instability," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, May 2010, pp. 16–25.

- [11] T. Grasser, H. Reisinger, P.-J. Wagner, and B. Kaczer, "The Time Dependent Defect Spectroscopy for the Characterization of Border Traps in Metal-Oxide-Semiconductor Transistors," *Physical Review B*, vol. 82, no. 24, pp. 245318, 2010.

- [12] H. Reisinger, T. Grasser, and C. Schlünder, "A Study of NBTI by the Statistical Analysis of the Properties of Individual Defects in pMOSFETs," in *Proc. Intl.Integrated Reliability Workshop*, 2009, pp. 30–35.

- [13] M. Waltl, W. Goes, K. Rott, H. Reisinger, and T. Grasser, "A Single-Trap Study of PBTI in SiON nMOS Transistors: Similarities and Differences to the NBTI/pMOS Case," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, 2014, pp. XT18.1–XT18.5.

- [14] T. Wang, C.-T. Chan, C.-J. Tang, C.-W. Tsai, H. Wang, M.-H. Chi, and D. Tang, "A Novel Transient Characterization Technique to Investigate Trap Properties in HfSiON Gate Dielectric MOSFETs-From Single Electron Emission to PBTI Recovery Transient," *IEEE Trans.Electron Devices*, vol. 53, no. 5, pp. 1073–1079, 2006.

- [15] J. Zou, R. Wang, N. Gong, R. Huang, X. Xu, J. Ou, C. Liu, J. Wang, J. Liu, J. Wu, S. Yu, P. Ren, H. Wu, S. Lee, and Y. Wang, "New Insights into AC RTN in Scaled High-κ/Metal-gate MOSFETs under Digital Circuit Operations," in *IEEE Symposium on VLSI Technology Digest of Technical Papers*, 2012, pp. 139–140.

- [16] M. Toledano-Luque, B. Kaczer, E. Simoen, Ph.J. Roussel, A. Veloso, T. Grasser, and G. Groeseneken, "Temperature and Voltage Dependences of the Capture and Emission Times of Individual Traps in High-k Dielectrics," *Microelectronic Engineering*, vol. 88, no. 7, pp. 1243– 1246. July 2011.

- [17] T. Grasser, K. Rott, H. Reisinger, M. Waltl, F. Schanovsky, and B. Kaczer, "NBTI in Nanoscale MOSFETs – The Ultimate Modeling Benchmark," *IEEE Trans. Electron Devices*, vol. 61, no. 11, pp. 3586–3593, Nov. 2014.

- [18] T. Grasser, K. Rott, H. Reisinger, P.-J. Wagner, W. Goes, F. Schanovsky, M. Waltl, M. Toledano-Luque, and B., "Advanced Characterization of Oxide Traps: The Dynamic Time–Dependent Defect Spectroscopy," in Proc. Intl. Rel. Phys. Symp. (IRPS), 2013, pp. 2D.2.1–2D.2.7.

- [19] T. Grasser, W. Goes, Y. Wimmer, F. Schanovsky, G. Rzepa, M. Waltl, K. Rott, H. Reisinger, V.V. Afanas'ev, A. Stesmans, A.-M. El-Sayed, and A.L. Shluger, "On the Microscopic Structure of Hole Traps in pMOSFETs," in *Proc. Intl.Electron Devices Meeting (IEDM)*, 2014.

- [20] M. Waltl, P.-J. Wagner, H. Reisinger, K. Rott, and T. Grasser, "Advanced Data Analysis Algorithms for the Time–Dependent Defect Spectroscopy of NBTI," in *Proc. Intl.Integrated Reliability Workshop*, Oct. 2012, pp. 74–79

- [21] B. Kaczer, T. Grasser, Ph.J. Roussel, J. Martin-Martinez, R. O'Connor, B.J. O'Sullivan, and G. Groeseneken, "Ubiquitous Relaxation in BTI Stressing – New Evaluation and Insights," in *Proc. Intl.Rel.Phys.Symp.* (IRPS), 2008, pp. 20–27.

- [22] Minimos-NT User Manual Release 2014.03, Global TCAD Solutions.

- [23] O. Baumgartner, Z. Stanojevic, K. Schnass, M. Karner, and H. Kosina, "VSP–A Quantum-Electronic Simulation Framework," *J. Comp. El.*, 2013.

- [24] P. Hehenberger, W. Goes, O. Baumgartner, J. Franco, B. Kaczer, and T. Grasser, "Quantum–Mechanical Modeling of NBTI in High-k SiGe MOSFETs," in *Proc. Simulation of Semiconductor Processes and Devices*, 2012, pp. 11–14.

- [25] L. Vandelli, L. Larcher, D. Veksler, A. Padovani, G. Bersuker, and K. Matthews, "A Charge-Trapping Model for the Fast Component of Positive Bias Temperature Instability (PBTI) in High-κ Gate-Stacks," *IEEE Trans.Electron Devices*, vol. 61, no. 7, pp. 2287–2293, July 2014.