Contents lists available at ScienceDirect

## Solid-State Electronics

journal homepage: www.elsevier.com/locate/sse

# The defect-centric perspective of device and circuit reliability—From gate oxide defects to circuits

B. Kaczer <sup>a,\*</sup>, J. Franco <sup>a</sup>, P. Weckx <sup>a,1</sup>, Ph.J. Roussel <sup>a</sup>, M. Simicic <sup>a,1</sup>, V. Putcha <sup>a,1</sup>, E. Bury <sup>a,1</sup>, M. Cho <sup>a</sup>, R. Degraeve <sup>a</sup>, D. Linten <sup>a</sup>, G. Groeseneken <sup>a,1</sup>, P. Debacker <sup>a</sup>, B. Parvais <sup>a</sup>, P. Raghavan <sup>a</sup>, F. Catthoor <sup>a,1</sup>, G. Rzepa <sup>b</sup>, M. Waltl <sup>b</sup>, W. Goes <sup>b</sup>, T. Grasser <sup>b</sup>

#### ARTICLE INFO

Article history:

Available online 20 July 2016

The review of this paper was arranged by Jurriaan Schmitz

Keywords: Variability Reliability Defects RTN BTI HCI

#### ABSTRACT

As-fabricated (time-zero) variability and mean device aging are nowadays routinely considered in circuit simulations and design. Time-dependent variability (reliability-related variability) is an emerging concern that needs to be considered in circuit design as well. This phenomenon in deeply scaled devices can be best understood within the so-called defect-centric picture in terms of an ensemble of individual defects. The properties of gate oxide defects are discussed. It is further shown how in particular the electrical properties can be used to construct time-dependent variability distributions and can be propagated up to transistor-level circuits.

© 2016 Elsevier Ltd. All rights reserved.

#### 1. Introduction

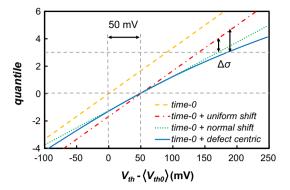

Circuit simulations

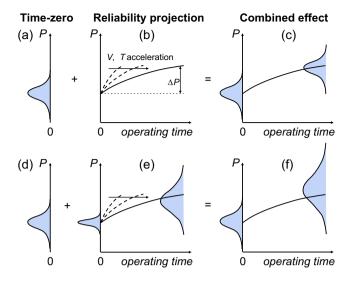

Variability of as-fabricated (i.e., time-zero) parameters of modern VLSI devices has been considered in circuit design tools for some time (Fig. 1a). With the exception of Time-Dependent Dielectric Breakdown (TDDB) [1,2], circuit lifetime estimation due to Field-Effect Transistor (FET) gate-oxide degradation (aging) mechanisms is presently based on projecting only the *mean* parameters shifts (Fig. 1b) [3]. The combination of both hitherto orthogonal efforts used in determining circuit operating margins is illustrated in Fig. 1c.

It has long been accepted that in mechanisms associated with FET gate current, such as Stress-Induced Leakage Current (SILC) and TDDB, only a handful of defects will cause significant current increases and can bridge the gate oxide, presently  $\sim 1$  nm thick. Similarly, as lateral dimensions of VLSI devices are reduced toward the 10 nm range, just a few stochastically-behaving defects present in the FET gate oxide will have a sizable impact on the *drive* current as well. These phenomena result in additional, *time-dependent*

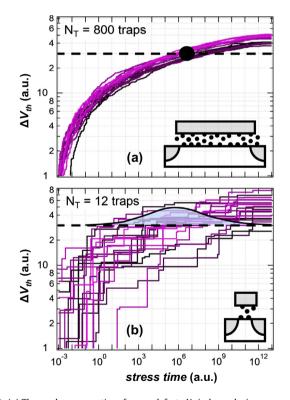

variability in deeply-scaled devices, and their manifestation in the form of Random Telegraph Noise (RTN) has been extensively studied by many groups [4–13]. Here we build upon those observations and show how the same, physics-based considerations give rise to a new, *statistical* perception of other gate-oxide degradation mechanisms, such as Bias Temperature Instability (BTI) and Hot Carrier Injection (HCI) [14–16]. This paradigm shift is illustrated in Fig. 2.

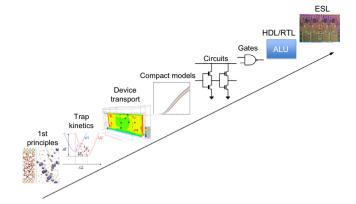

Since only a handful of defects (cf.  $N_T$  = 12 in Fig. 2b) will be responsible for the time-dependent effects in each deeply-scaled device, we maintain that understanding of degradation mechanisms at the level of individual defects is essential for simulations of time-dependent variability in circuits. This notion is indeed the basis of the so-called *defect-centric* picture and is hierarchically illustrated in Fig. 3. After defining basic variability terms, we review the properties of individual defects and show how to propagate these properties to higher hierarchical levels. We formalize the statistical description of time-dependent distributions (Fig. 1e) into simple equations and point out the parallels with time-zero variability. To estimate the full device and circuit parameter distributions at the end of useful lifetime, time-zero and time-dependent statistics have to be combined, as illustrated

a imec, Kapeldreef 75, B-3001 Leuven, Belgium

<sup>&</sup>lt;sup>b</sup> TUWien, Gusshausstrasse 27-29, A-1040 Vienna, Austria

<sup>\*</sup> Corresponding author.

E-mail address: ben.kaczer@imec.be (B. Kaczer).

<sup>&</sup>lt;sup>1</sup> Also at KU Leuven, ESAT Department, Leuven, Belgium.

**Fig. 1.** A schematic representation of time-zero and time-dependent effects considered in circuit design. (a-c) Presently, time-zero variability of a device parameter P is considered together with the projection of the mean parameter shift  $\Delta P$  (obtained by reliability engineers through bias and temperature accelerated tests) during aging. (d-f) Time-dependent variability is also considered, in contrast to (a-c).

**Fig. 2.** (a) The random properties of many defects  $N_T$  in large devices average out, resulting in a well-defined lifetime while (b) the stochastic nature of a handful of defects in deeply-scaled devices becomes apparent, resulting in large variation in the lifetime. This also illustrates the paradigm shift in projecting reliability in deeply scaled devices (Fig. 1b and e) [17].

in Fig. 1d-f. Finally, we discuss how the combined variability can be propagated to and simulated at the circuit level.

## 2. Device variability

We refer to as-fabricated, time-independent, or static, device-todevice variability, as time-zero variability. Time-dependent, or

**Fig. 3.** Hierarchical levels of the defect-centric picture: Understanding of defect properties at the atomic level [18] can be propagated up to circuit design.

dynamic, variability then refers to all variability due time-dependent effects. In this work, this is limited to effects due to defects (traps) present in FET gate dielectrics. The main emphasis of this Section is developing the time-dependent variability within the defect-centric picture. This is done Section 2.2. Subsections thereof then discuss the properties of individual traps (Section 2.2.1), both temporal and electric, the statistics of multiple traps (Section 2.2.2), and the experimental methods to characterize time-dependent variability (Section 2.2.3). The complete distribution (Section 2.3) is constructed from time-dependent variability and time-zero variability, discussed next.

#### 2.1. Time-zero variability

As-fabricated, i.e., time-zero variability, both systematic (process-induced) and random, is a well-known phenomenon in deeply-scaled VLSI technologies [19,20]. For example, the time-zero threshold voltages  $V_{th0}$  are assumed to be normally-distributed with mean  $\langle V_{th0} \rangle$  and variance  $\sigma_{Vth0}^{-2}$  [21]. Disregarding edge effects, the random component of  $\sigma_{Vth0}^{-2}$  scales as

$$\sigma_{Vth0}^2 \cong \frac{A_{Vth}^2}{A_C} \tag{1}$$

where  $A_{Vth}$  is a scaling factor and  $A_G$  the total channel area [22,23]. It should be noted that some variation-inducing effects, such as Line-Edge Roughness, will result in a departure from this ideal scaling rule in deeply scaled devices [24].

A large number of nominally identical devices need to be typically measured to establish  $A_{Vth}$ , while organization of devices into matched pairs or local arrays is used to separate the systematic and the random components [25].

#### 2.2. Time-dependent variability

Similarly to time-zero variability, time-dependent variability also has random and systematic components [25–28]. Because of the limited number of gate-oxide defects  $N_T$  present in modern deeply downscaled FETs (e.g.,  $N_T$  = 10 with defect density  $10^{12}$  cm<sup>-2</sup> and  $A_G$  =  $W \times L$  =  $100 \times 10$  nm<sup>2</sup>), other degradation mechanisms, such as RTN/BTI and HCI will be distributed as well [14,16,29]. Based on this simple fact we claim that the time-dependent variability in deeply scaled devices can be best understood in terms of an ensemble of individual defects and their time, voltage, and temperature dependent properties. This is indeed the underlying foundation of the defect-centric approach. To develop this approach further, we now discuss some of the relevant properties of individual defects.

#### 2.2.1. Properties of individual defects

The properties of each gate oxide defect (trap) are formed by the spatial location of the defect in the FET gate insulating layer, as well as the immediate configuration of atoms around it [18]. Because of the amorphous nature of the presently-used gate dielectrics, each defect will have substantially different structural properties, such as the ground level and the relaxation energy [30–32].

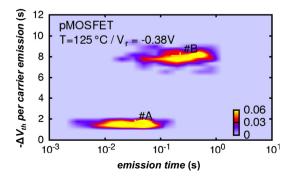

All these properties will then project into two main classes of parameters usable at higher abstraction levels, namely (a) the defect time constants (temporal) and (b) the defect impact on the FET parameters (electrical). An illustration of a distribution of these properties for two distinct defects in a deeply-scaled device is given in Fig. 4.

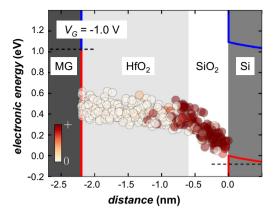

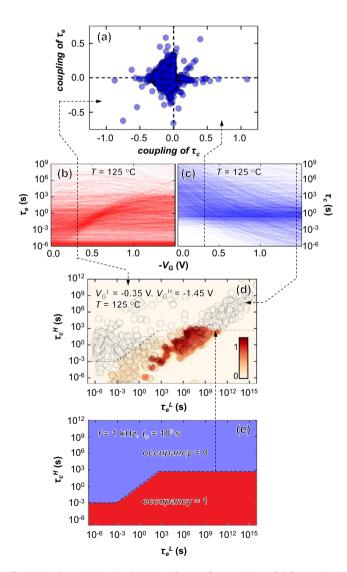

2.2.1.1. Temporal defect properties. The defect time constants  $\tau_c$  and  $au_e$  are the mean times for the gate defect to capture and emit a carrier. In addition, each capture and emission event will be stochastic and exponentially distributed around the respective mean value (cf. spread in individual emission times in Fig. 4). The values of  $\tau_c$  and  $\tau_e$  vary drastically from defect to defect, from at least tens of ns to years, based on the abovementioned defect structural and spatial (depth and lateral) properties, bias and temperature. Distributions of  $\tau_c$  and  $\tau_e$  can be inferred from a simulation of the FET device (Fig. 5) assuming distributions of the structural and spatial properties of the defects within the Non-radiative Multi-Phonon (NMP) theory [9,35]. The extracted distributions of  $\tau_c$  and  $\tau_e$  at varying gate voltages (for a given temperature, Fig. 6b and c) then allow to conveniently describe both RTN at any given fixed bias (Fig. 6a) [10] and BTI (stress and relaxation) at arbitrary biases. If the gate bias varies between two levels, e.g. 0 and the circuit supply voltage  $V_{DD}$ , as is the case in digital circuits, the  $\tau_c^H$  at high bias (stress) and  $\tau_e^L$  at low bias (relaxation) form the so-called Capture/ Emission Times (CET) map (Fig. 6d) [37].

Encoding the BTI degradation in the form of a CET map allows to conveniently project the degradation of any device. The trap occupancy map (Fig. 6e) can be calculated in the same space for an arbitrary digital workload applied to the gate of the device. Analytic solutions exist for constant and periodic signals [40,41]. An algorithm has therefore been developed to partition an arbitrary workload signal into a sequence of constant and periodic phases [41], facilitating the occupancy calculation. The trap occupancy map is then convoluted with the CET map (Fig. 6d), yielding the occupied number of traps in the particular device [39,40].

The concept of time constants characterizing individual traps can be easily extended to defect generation, e.g. by assuming additional time to convert a precursor site into a trap [42].

**Fig. 4.** An example of Time-Dependent Defect Spectroscopy (TDDS) spectrum of two traps (#A and #B) in a deeply-scaled pMOSFET device. The distribution of emission times and impacts on the FinFET  $V_{th}$  is apparent. The TDDS technique was developed specifically within the defect-centric approach [33,34].

**Fig. 5.** A simulation of pFET device with a high-k/metal gate stack assuming a defect band. Large-area device is simulated to obtain average behavior. Capture and emission to/from both the substrate and the gate are considered [35,36].

**Fig. 6.** Based on  $\tau_c(V_G)$  and  $\tau_e(V_G)$  dependences of a population of defects at given temperature T (b, c), both an RTN behavior (e.g., distributions of coupling factors kT/q  $\beta$ ln  $\tau/\partial V_G)$  [10] (a) and BTI response in the form of a CET map (d) can be computed [37,38]. A trap occupancy map (e.g., for periodic AC signal) [39] (e) can be calculated for any digital workload in the same coordinates. Superimposing it over the CET map determines degradation of the device for that particular workload.

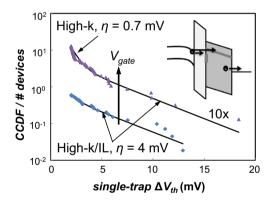

2.2.1.2. Electrical defect properties. In general, a defect can impact one or multiple FET properties. It can, e.g., act as a "stepping stone" between the FET body and the gate and thus contribute to gate leakage [44–46], or it can influence the channel current when charged [47]. Again, the impact will be distributed. E.g., the impact of charged defects on the drain current, for the sake of convenience converted into the threshold voltage shift  $\Delta V_{th}$ , is approximately exponentially distributed (Fig. 7).

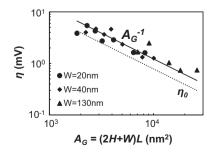

The expectation value of this distribution,  $\eta$ , represents the *mean* impact of a single trap and is the crucial parameter in the defect-centric model. To the first order (cf. considerations around Eq. (1) and e.g. [48]), it scales as

$$\eta = \frac{B_{\eta}}{A_{G}},\tag{2}$$

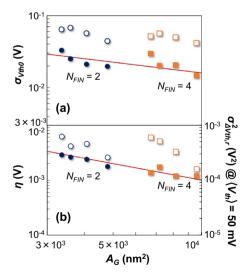

where  $B_{\eta}$  is a scaling factor increasing with increasing gate oxide thickness and increasing channel doping  $N_A$  and  $A_G$  is the area of the device channel [49,50]. Other sources of variability randomizing the channel potential, such as fixed oxide charges and interface defects [51], are expected to take the place of  $N_A$  in low-doped channel devices (e.g., FinFETs). The dependence of  $A_G$  in FinFET devices is confirmed in Fig. 8 [52].

In Fig. 8, the value of  $\eta$  for p-channel devices (hole trapping) is approximately double the value of  $\eta_0 = q/C_o$ , the shift expected for a charge sheet at the Si/dielectric interface [48,52]. We have observed that in gate stacks on high-mobility substrates currently being considered for upcoming technology nodes, the ratio  $\eta/\eta_0$  can both decrease, in case of p-channel SiGe FETs [53], and

**Fig. 7.** Exponential distributions of  $V_{th}$  shifts  $\Delta V_{th}$  due to single trapping events, collected from "step heights" in TDDS measurements on multiple nFET devices. The bimodal distribution corresponds to trapping in high-k and at IL/high-k interface [43] (inset; the infrequently-observed electron de-trapping also illustrated). At lower  $V_G$ , trapping at the IL/high-k interface is dominant.

**Fig. 8.** The mean impact per trap  $\eta$  as  $A_G^{-1}$  in pFinFETs (high-k/MG,  $t_{inv} \approx 1.7$  nm) with varying fin width W and gate length L (fin height  $H_{fin}$  is fixed). Each point is extracted from a monomodal TDDS distribution (cf. Fig. 7). The value of  $\eta$  is  $\sim 2 \times$  higher than the expected  $\Delta V_{th}$  for a single charge from a charge sheet approximation  $\eta_0 = q/C_{ox}$  [52].

increase, in case of n-channel InGaAs [54]. We explained the decrease by trapping deeper in the SiGe-channel gate oxide [53,55]. The increase in the III–V devices we ascribed to more percolative channel conduction induced by still excessive interface and channel defectivity, potentially combined with larger channel carrier centroid displacement from the interface, induced by quantum effects in the low density-of-states semiconductor [54].

In nanolaminate high-k dielectrics used in modern FET devices, each trap "layer" will contribute with its own  $\eta$  value and the resulting distribution will be bi- or multimodal (cf. Fig. 7) [43,56–58].

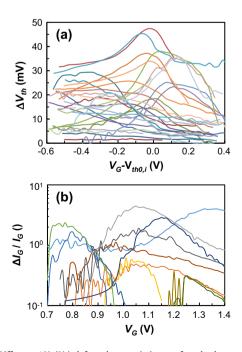

The impact of a charged defect is obviously not limited to  $V_G = -V_{th}$ , and can vary with gate and drain biases (cf.  $\tau_c$  and  $\tau_e$  temporal dependences in Fig. 6). The  $V_G$  dependence is illustrated in Fig. 9 for both the impact on drain [52] and gate currents [35,36,46].

#### 2.2.2. Multiple defects: Defect-centric statistics

Identical stress of a population of deeply scaled devices will result in a *distribution* of FET parameter shifts, as illustrated in Fig. 10 (cf. Fig. 2b). Note that in a population of  $\sim$ 400 devices, the  $\Delta V_{th}$  of some devices after identical BTI stress is negligible, while other devices shift by  $\sim$ 100 mV(!). This contrasts with the large-area devices of the past, in which identical stress resulted in identical degradation (cf. Fig. 2a). Understanding of BTI and HCI distributions in deeply-scaled devices therefore requires the new, defect-centric approach. The information presented so far in the previous sub-section is sufficient to achieve this goal.

As the individual gate oxide defects charge during operation, corresponding to RTN/BTI and/or HCI degradation, they will concurrently modify the channel current [59]. To describe their combined impact on  $V_{th}$  in a population of FETs, we simply assume that the number of charged defects varies from device to device following Poisson statistics with the mean number of defects per device  $N_T$ . When combined with the  $\Delta V_{th}$  exponential distribution of each contributing charged defect (cf. Section 2.2.1.2), it can be

**Fig. 9.** (a) Different  $\Delta V_{th}(V_G)$  defect characteristics are found when measuring 30 different (but nominally identical) pFETs before and after the capture of a single hole [52]. (b) Different  $\Delta I_G(V_G)$  characteristics are found when measuring several (but nominally identical) nFETs before and after the activation of a single defect [46].

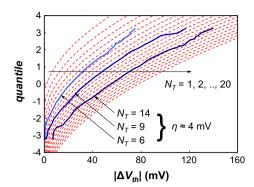

**Fig. 10.** Total  $\Delta V_{th}$  distribution (Eq. (3)) for the average number of defects  $N_T$  from 1 to 20 (thin lines) rescaled to fit experimental distributions from Fig. 10 of Ref. [60], with the corresponding values of  $N_T$  and  $\eta$  readily extracted.

shown that the resulting statistics will have a cumulative distribution given by [14,15,61]

$$H_{\eta,N_T}(\Delta V_{th}) = \sum_{n=0}^{\infty} \frac{e^{-N}N^n}{n!} \left[ 1 - \frac{n}{n!} \Gamma\left(n, \frac{\Delta V_{th}}{\eta}\right) \right]. \tag{3}$$

Note that the above *defect-centric*  $\Delta V_{th}$  distribution is controlled by only two parameters,  $\eta$  (cf. Eq. (2)), and  $N_T$ , where the latter is simply linked to the defect density  $N_{ot}$  as  $N_T = N_{ot} A_{G}$ . As is apparent from Fig. 10, Eq. (3) excellently describes the measured distributions.

Having an analytical description of the  $\Delta V_{th}$  distribution has several advantages. It allows to (i) make projections to high percentiles without the need to measure or simulated billions of devices, and (ii) provide a crucial link between the first two statistical moments of the  $\Delta V_{th}$  distribution [14,15,61]

$$\sigma_{\Delta V_{th}}^2(t) = 2\eta \langle \Delta V_{th}(t) \rangle. \tag{4}$$

$\langle \Delta V_{th}(t) \rangle$  is the mean shift of the population, linked with the two parameters of Eq. (3) as  $\langle \Delta V_{th}(t) \rangle = \eta \ N_T(t)$ .  $\langle \Delta V_{th}(t) \rangle$  is projected to operating conditions using established acceleration techniques. Eq. (3) also allows to extract  $\eta$  directly from measured  $\Delta V_{th}$  distributions (typically at accelerated conditions), without having to analyze the statistics of individual steps, as will be discussed in the next section.

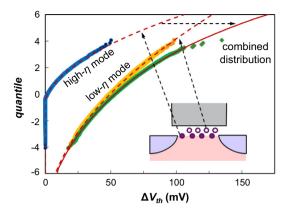

In devices with high-k dielectrics, trapping in multiple layers will be combined, resulting in a bi- or multi-modal distribution [57,58]. The high-percentile tail may be controlled by the defects low in density, but with high  $\eta$  value (i.e., closer to the substrate), as illustrated in Fig. 11 [16]. The analytical description of the multi-modal defect-centric distribution has been also derived, allowing to correctly project the high-percentile tails [58].

The correct knowledge of  $B_{\eta}$  (Eq. (2)), combined with the projection of the expected degradation mean  $\langle \Delta V_{th}(t) \rangle$ , discussed in Section 2.2.1.1, then allows to make an educated prediction of degradation distribution in the entire device population of the VLSI application [16]. In the following we therefore understand the characterization of time-dependent variability to be equivalent to extracting  $B_{\eta}$  (i.e.,  $\eta$  vs.  $A_G$ ) for a given technology, analogously to extracting  $A_{vth}$  (Eq. (1)) for time-zero variability.

## 2.2.3. Characterization of time-dependent variability

The parameter  $\eta$  can be extracted from RTN or TDDS (Fig. 4) amplitudes of individual defects or from a  $\Delta V_{th}$  distribution (Fig. 10), where multiple, Poisson-distributed number of defects contribute simultaneously. While actively-stimulating individual traps using TDDS is considerably more powerful than mere passive RTN measurements, we note that the analysis of individual defect

**Fig. 11.** Illustration of bimodal  $\Delta V_{th}$  defect-centric distribution (cf. the bimodal distribution for *individual* defects, Fig. 7) [16]. Symbols: Monte Carlo, lines: analytic fit [16,58]. The high- $\sigma$  tail of the full distribution is controlled by defects at the substrate (high  $\eta$ ; inset: solid symbols).

steps is generally a highly elaborate process, involving step detection in time traces with experimental noise, complex "bookkeeping" to avoid double-counting of defects resulting in "stuffing" of amplitude distributions, and the uncertainty in fitting the distribution tail [28]. On the other hand, extraction of  $B_{\eta}$  from the defect-centric  $\Delta V_{th}$  distribution using Eqs. (2) and (4) appears to be more pragmatic and more suitable for industrial and production environments.

Obviously, obtaining both time-zero and time-dependent variability distributions requires measurements on a sufficiently large number of devices. If these devices are distributed over a larger area, process-induced variations (e.g. across the wafer) will increase the observed variability. In order to extract the random variability component only, the additional process-induced variability can be corrected for by either using the so-called matched pairs or local arrays of a large number of closely-packed devices.

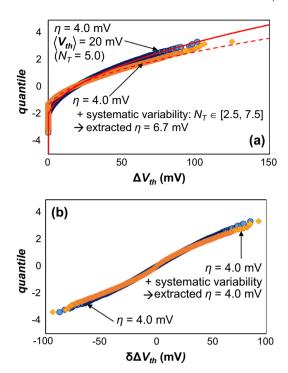

2.2.3.1. Matched pairs. Analogously to time-zero analysis [22], standard matched FET pairs (MPs), widely available in most test-chip layouts, can be used for the same task of extracting random time-dependent variability [27,28,62]. Resolution of  $\eta$  down to  $\sim$ 0.1 mV range can be achieved [28]. We define

$$\delta \Delta V_{th} = \Delta V_{th,L} - \Delta V_{th,R} \tag{5}$$

as the difference between the  $V_{th}$  shift of the left ("L") and the right ("R") devices of the MP. We now introduce additional systematic (process-induced) variability, represented by varying the originally constant mean number of defects per device  $N_T$  [28]. This conceptually mimics across-wafer variations in gate oxide defect density of traps due process variations, such as plasma-induced damage, or larger degradation in devices with locally thinner oxide. We see that the single-device defect-centric distribution is substantially dilated (Fig. 12a). A naive extraction of random variability from this distribution, represented by  $\eta$ , then leads to incorrect conclusions. (Such an error is analogous to obtaining  $\sigma_{Vth0,r}$  from single-device timezero  $V_{th0}$  distributions.) When systematic variability in MPs is simulated by using the randomized, but identical  $N_T$  for both "L" and "R" devices of each pair, the MP  $\delta\Delta V_{th}$  distribution in Fig. 12b is not significantly changed. The *intrinsic*, i.e. random variance ( $\sim \eta$ , Eq. (4)) can be readily extracted from the difference distribution  $\delta \Delta V_{th}$ obtained on MPs (Fig. 12b).

Fig. 13 illustrates the methodology applied to real silicon devices. It is apparent that for both n and pFinFET devices tested, the time-zero variances extracted from single devices (Fig. 13a and b, open symbols) are affected by systematic variability and

**Fig. 12.** Probit plots of Monte Carlo simulation of defect-centric distributions in (a) single devices and (b) matched pairs. *Additional systematic variability*, generated by distributing the defect density  $N_{\rm T}$ , in single devices (a) is *fully compensated and the original*  $\eta$  *is restored* (b). Blue circles and orange diamonds: distributions *without* and *with* systematic variability included [28]. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

**Fig. 13.** The random components of both (a) time-zero and (b) time-dependent variabilities, extracted using matched pairs (solid symbols), follow area scaling (Eqs. (1) and (2), respectively, lines) in contrast to single nFinFET devices (open symbols), which are affected by systematic variability. Eq. (4) is used for the right-hand axis [28].

thus overestimate the random component extracted from MPs (solid symbols), which follow correct  $A_G$  scaling (line, Eq. (1)) [22,23,25]. Similarly for time-dependent variability,  $\eta$  obtained on nFinFETs (Fig. 13c) by naive extraction from single devices does not scale correctly with  $A_G$ . Thus extracted  $\eta$  overestimates the true value, as illustrated already in Fig. 12. However, when the MP methodology is used, the resulting  $\eta$ 's scale excellently with device area and the parameter  $B_\eta$  (Eq. (2)) can be readily extracted.

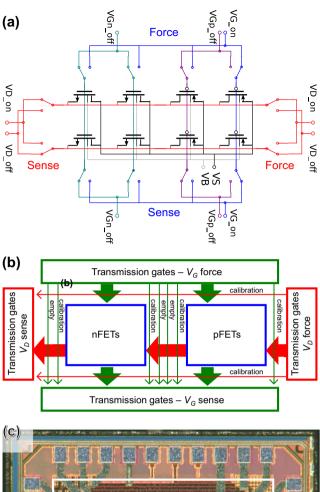

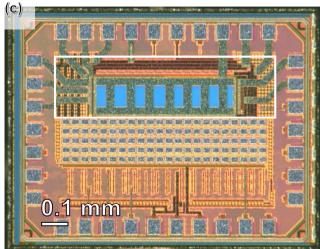

Fig. 14. (a) Reduced schematic of the array including both nFETs and pFETs, double transmission gates (shown as switches), Kelvin sensing for the drain and gate terminals, the body and the source connections. (b) Placing plan of the array. To reduce unwanted RTN signals and enable higher than nominal voltages on the test FETs, the switches are designed with sufficiently large IO devices. Two shift registers are used to address the transmission gates with level shifters, with the added capability to measure multiple test FETs in parallel. Calibration and open lines are included to characterize the leakage from the periphery, the parasitic resistances and as a sanity check for the programming of the chip during measurements. (c) Microphotograph of the chip with the array containing 54,432 devices is delineated (top). Similar area is occupied by a few tens of individually-accessible FETs (center). A pipelined array for parallelizing MSM sequences in hardware by up to 5× contains several hundred devices (bottom; discussed in [67,68]).

2.2.3.2. Local arrays. One of the first applications of closely-packed identical capacitors to separate across-wafer and random variabilities in TDDB measurements was proposed by Roussel et al. [26]. Kerber et al. have used simple, periphery-less  $8 \times 8$  local FET arrays

**Fig. 15.**  $\Delta V_{th}$  distributions obtained on pFETs with 6 different areas in the array in Fig. 14 [24]. Opposite shifts are observed originating from RTN [33]. Symbols: measurements, curves: Monte Carlo (MC) fits of defect-centric distributions (Eq. (3)), including the RTN tails.

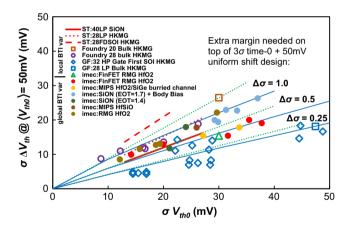

**Fig. 16.** pFET time-dependent variability (at 50 mV mean degradation) plotted against time-zero variability for various techologies. Results from the discussed array are designated "Foundry: 28 bulk HKMG". The isolines indicate the added margin  $(\Delta\sigma)$  on top of the standard  $3\sigma$  margin for CMOS logic that the design needs to handle (i.e.,  $3\sigma + \Delta\sigma$ ) when factoring in time-zero variability + 50 mV mean BTI shift, using either a Normal approximation (dashed) or full defect-centric distribution (solid), cf. Fig. 17 [66].

to extract both time-zero and time-dependent variability and to separate across-wafer and random components [25]. Substantially larger arrays, allowing to map further into the tails of variability distributions, already require sophisticated control periphery [63,64]. Learning and results obtained with arrays with  $\sim\!10^4$  devices are demonstrated here [24,58,65,66].

The array, illustrated in Fig. 14, includes 54,432 individual test FETs [24,65]. Different transistor geometries are used, each of which contains  $108 \times 42 = 4536$  single test FETs. All the test n and pFET devices share the source and body terminals, the gates are shared among the test FETs in rows, while the drains are shared in columns (Fig. 14a). The placement plan of the array is depicted

**Fig. 17.** Three possible ways of adding time-dependent variability to the time-zero distribution (dashed yellow): (i) a simple shift of  $\langle \Delta V_{th}(t) \rangle$  in all devices (dot-dashed red), (ii) a Normal (Gaussian, dotted green), and (iii) the defect-centric statistics (Eq. (3), solid blue). The discrepancies between the defect-centric distribution and the approximations are evident at higher quantiles. Considering time-zero variability +50 mV mean BTI shift, using either a Normal BTI approximation or defect-centric BTI can be expressed as additional margin ( $\Delta\sigma$ ) needed on top of a  $3\sigma$  margin in the conventional, time-zero-only design [61,66]. (For interpretation of the references to color in this figure legend, the reader is referred to the web version of this article.)

in Fig. 14b. The drawn area of the design is 0.18 mm<sup>2</sup> (Fig. 14c, highlighted in red<sup>2</sup>).

The array allows the standard characterization of time-zero variability, i.e., the extraction of  $\sigma_{Vth^2}$  for varying device gate areas  $A_G$ , and hence  $A_{Vth}$  (Eq. (1)). A Measure-Stress-Measure (MSM) sequence on each FET then allows to determine  $\Delta V_{th}$  for each device. Typical  $\Delta V_{th}$  distributions are shown in Fig. 15. The distributions have the distinct defect-centric shape (Fig. 10), allowing the extraction of  $\eta$ , and the time-dependent variability (Eq. (4)) for different device areas [24,65]. Opposite shifts are also observed, originating from RTN in the devices [58].

Both the time-zero and the time-dependent intrinsic variances are therefore obtained using the same array, allowing to characterize and benchmark the underlying technology. The variances are shown in Fig. 16, designated as "Foundry: 28 bulk HKMG" (6 open purple circles). Note that the variances per technology typically scale with device area, as per Eqs. (1), (2) and (4) [61,62]. Fig. 16 further illustrates the relatively wide spread in the  $\sigma_{Vth0}$ - $\sigma_{AVth}$  relationship [51], with values of  $\sigma_{AVth}$  at  $\langle \Delta V_{th} \rangle$  = 50 mV (a typical CMOS logic degradation criterion) almost reaching their  $\sigma_{Vth0}$  counterparts for some technologies. This confirms the significance of considering the time-dependent variability—the main thesis of this paper.

## 2.3. Total variability

The combined knowledge of time-zero and time-dependent variability for a given technology is expressed through the tuple  $(\sigma_{Vtho}; \sigma_{AVth} @ \text{given } \langle \Delta V_{th} \rangle)$ , as in Fig. 16, or more generally through area-independent  $(A_{Vth}; B_{\eta})$ , cf. Eqs. (1) and (2). This combined information enables projections of the total distribution of a FET parameter after operation at nominal operating conditions, allowing the circuit designer a rigorously-derived control of the design margins.

As illustrated in Fig. 1f, the *total* distribution is simply a convolution of time-zero and time-dependent distributions [61,66,69,70]. Fig. 17 illustrates this convolution for 3 different cases: (i) no time-dependent variability (uniform shift, corresponds to Fig. 1c), (ii) Normally-distributed time-dependent variability [71], and (iii) Eq. (3) (defect centric). Note that the Normal

$<sup>^{\,2}\,</sup>$  For interpretation of color in Fig. 14, the reader is referred to the web version of this article.

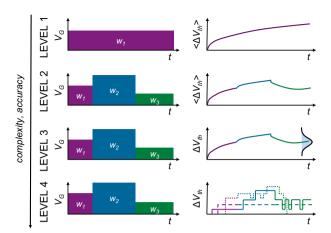

**Fig. 18.** Complexity/accuracy levels of incorporating device aging (specifically here, the threshold voltage shift) in circuit simulations. The full workload on each device can be *approximated* by a series of phases  $w_i$  with duration t, voltage V, duty factor DF, frequency f, and temperature T. (In reality the number of workload phases is typically very large.)

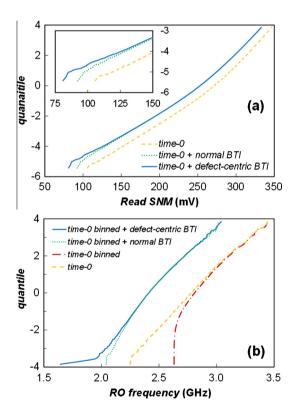

**Fig. 19.** (a) Probit plot of the Read Signal Noise Margin (RSNM) of 28 nm technology SRAM cell for an average 50 mV NBTI shift. Inset magnifies the discrepancy at higher quantiles. (b) Impact of binning at time-zero on a population of ring oscillators. The yield cut-off criterion of  $mean-1\sigma$  of the ring oscillator frequency is used. The loss of the effect of binning due to time-dependent variability at low percentiles, as well as the choice of the time-dependent distribution (normal or defect-centric) are apparent [81].

approximation is not entirely physical, as it is bound to cross the time-zero distribution (at low percentiles). On the other hand, the defect-centric model (Eq. (3)) predicts larger  $V_{th}$  shifts at high percentiles, again emphasizing the need to factor in time-dependent variability (cf. the definition of  $\Delta \sigma$  in Fig. 17 and the isolines in Fig. 16).

We also note that in some cases, a correlation between timezero and time-dependent variability may exist. This is because

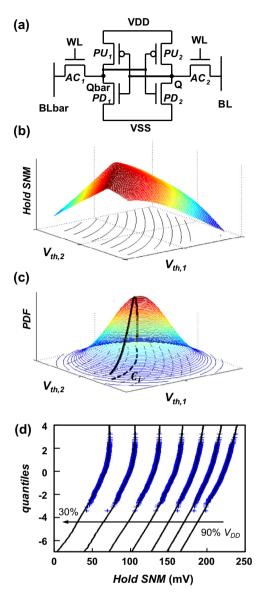

**Fig. 20.** (a) A schematic of a 6T-SRAM cell. (b) Any given circuit figure of merit, e.g., SRAM Hold SNM, is pre-characterized as a function of the 6 FET  $V_{th}$  values (dependence on  $V_{th,1}$  and  $V_{th,2}$  shown). (c) Projected total distributions after degradation (as discussed in Section 2.3.) of the 6 FET  $V_{th}$ 's is evaluated along the constant SNM isoline. (d) SNM distribution at decreasing supply voltage  $V_{DD}$ . Lines: the non-MC numerical propagation technique can predict the tails of the distribution up to  $-7\sigma$ . Symbols: MC simulation added for comparison shows excellent agreement with the non-MC method [83].

devices with higher  $V_{th}$  may degrade less at fixed gate bias as both the oxide field and self-heating effects driving the degradation will be lower [72]. Such correlations need to be factored into the convolution.

### 3. Application to circuits

The conventional reliability margins in modern technologies generally decrease due to the higher electric fields, while simultaneously, voltage-overdriving techniques are employed by designers to maximize performance [43]. Consequently, more elaborate reliability projection methods are needed to guarantee product reliability. The methods are based on the realization that (i) in real circuits, the devices seldom see constant stress at the supply voltage throughout their entire operating lifetime, as has been

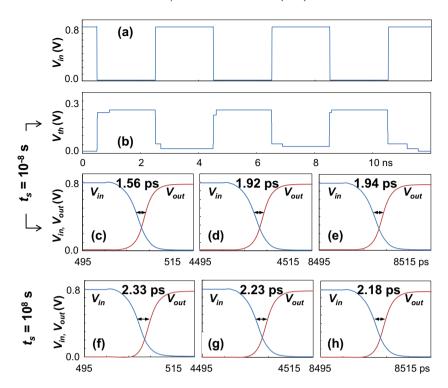

**Fig. 21.** Inverter degradation simulation transient snapshots. (a) Three periods of a f = 250 MHz input signal of the studied inverter. (b) Corresponding time-dependent pFET threshold voltage  $V_{th}$  after  $10^{-8}$  s illustrates the modulation of  $V_{th}$  by defects. (Note that due to short channel effects,  $V_{th}$  is also modulated by  $V_D$ , i.e., the output signal of the inverter.)  $V_{th}$  after  $10^8$  s is further degraded due to the capture of charge in large- $\tau_c$  defects. Switching delay of the studied inverter during the three periods (c-e) after  $10^{-8}$  s and (f-h)  $10^8$  s [4].

assumed in the past conservative technology reliability qualification, (ii) the failure criterion for each device will be different, depending on its function in the circuit, and (iii) the time-dependent variability needs to be considered in deeply-scaled technologies, as argued hitherto. All of these notions require technology- and reliability-aware simulation and design.

For the purposes of this paper, the different levels of implementation of device aging in circuit simulations are defined in Fig. 18. Level 1 corresponds to predicting the device degradation by assuming the device operates at a fixed "effective" workload throughout its entire lifetime in the circuit. Level 2, an improvement over Level 1, acknowledges that devices can be exposed to a sequence of different workloads throughout their operation, including e.g. short bursts of data activity (at ns – ms time scales) to "turbo", "sleep", and "off" modes (ms – day time scales) [73]. Implementations of Level 2 range from the so-called reaction-diffusion model [74] to CET map-based (cf. Fig. 6) [75,76]. Level 3 then adds the time-dependent variability parameter distributions, as derived above (Eq. (2)), on top of the projected mean parameter shift (cf. Level 3 in Figs. 18 and 1e) [41,77–80].

Level 1–3 circuit simulations evaluate the circuit at *static* degradation projected at a specified time. In contrast to that, Level 4 simulation incorporates the *temporal* stochastic behavior of individual traps and allows transient simulations. Level 3 and Level 4 simulations are now discussed.

#### 3.1. Level 3 circuit simulations

Similarly to Level 2, Level 3 circuit simulations rely on projecting mean degradation  $\langle \Delta V_{th}(t) \rangle$  for realistic workload for every device, as outlined in Section 2.2.1.1.

The significance of incorporating time-dependent variability in Level 3, and in particular, our defect-centric approach (Eq. (3)) in circuit simulations, is addressed in Fig. 19. For high- $\sigma$  designs, such as large SRAM arrays [82], circuit simulations show that incorpora-

tion of time-dependent variability will influence the distribution tails [81], as was already alluded to in Fig. 17. The distribution tails determine the product failure rates in the field and correct incorporation of time-dependent variability is therefore essential.

For low- $\sigma$  designs, such as logic data paths [71,78,79], we notice that the choice of the time-dependent variability distribution will be visible even at low  $\sigma$  values, if product binning is considered [81]. This is because this standard manufacturing procedure allows the manufacturer to compensate for time-zero variability, which, however, increases the relative weight of time-dependent variability, not present and not assessable in the product at time-zero. At the moment it appears that the Level 3 approach (cf. Fig. 18 and Fig. 1d–f) has the best chance of being integrated in commercial EDA tools.

To achieve the distributions in Fig. 19, simulations were repeated with the same circuit instantiated with the FET threshold voltages randomly selected from the total distribution (Fig. 17) in each iteration. This brute-force MC technique, however, does not scale well to offer insights into the distribution tails. We have therefore recently developed a fully *non*-MC technique, relying on first describing the circuit with a *response surface*, followed by numerically propagating the total  $V_{th}$  distribution (Fig. 17) through it. Using this method, projections to  $\pm 7\sigma$  (Fig. 20) can be made with a modest CPU effort for certain circuits [83].

## 3.2. Level 4 circuit simulations

Level 4 (Fig. 18) allows transient circuit simulations with the impact of individual traps, allowing to study e.g. RTN effect on circuits, such as sensor arrays [63], after aging. It is physically the most accurate, but also correspondingly more CPU intensive. To initialize the simulation, Level 3 simulation can be first performed up to the simulated age of the circuit. Then, each device is instantiated with a Poisson-distributed number of traps and each trap is instantiated with  $\tau_e(V_G)$ ,  $\tau_c(V_G)$ , and  $\Delta V_{th}$ , taken from the

corresponding distributions (Figs. 6 and 10) [17,84]. The impact on  $\Delta V_{th}$  is adjusted according Eq. (2). During the simulation, the trap occupancies are dynamically evaluated in each simulation time step depending on  $\tau_e(V_G)$  and  $\tau_c(V_G)$  of each trap.

Fig. 21 shows snapshots of one instance of the inverter simulation at the beginning of its operating lifetime (Fig. 21b–e) and after  $10^8$  s (Fig. 21f–h). Fig. 21b shows the pFET threshold voltage  $V_{th}$  behavior at the beginning of the circuit operation.  $V_{th}$  is changing as single holes are captured in two fast "cyclo-stationary RTN" [85] defects when the inverter input is low (i.e., the pFET gate is stressed), and subsequently emitted when the inverter input is high (i.e., pFET  $V_C = V_S$ ). The same two defects are still active after  $10^8$  s of the circuit operation (Fig. 21f); note, however, the pFET  $V_{th}$  is further degraded with respect to its initial value (Fig. 21b) due to the charge capture in slow defects. This latter behavior thus naturally emulates the "classical" BTI degradation.

The inverter switching transients are also illustrated in Fig. 21. It is apparent that there is a variation in the inverter switching delay from period to period (see Fig. 21c-e and f-h), resulting in the so-called delay jitter [86]. The overall slowdown of the inverter after 10<sup>8</sup> s of operation is also apparent (cf. Fig. 21c-e and f-h).

#### 4. Conclusions

We have argued that time-dependent variability (reliability variability) is an emerging concern that needs to be considered in circuit design in addition to time-zero variability and mean device degradation [87]. We moreover have claimed that the time-dependent variability in deeply scaled devices can be best understood in terms of an ensemble of individual defects and their time, voltage, and temperature dependent properties. We have discussed the properties of gate oxide defects and have shown how, within the so-called defect-centric picture, these properties can be used to construct time-dependent variability distributions and can be propagated up to transistor-level circuits. At the moment it appears that the approach presented as Level 3 in Section 3.1 is the most suitable for being integrated in commercial EDA tools. The necessary formalism has been presented.

## Acknowledgments

The presented work has been performed within the imec Logic INSITE Partner Program. The work has been in part supported by the European Commission under FP7 project 261868 (MORDRED) and project 619234 (MORV).

## References

- Degraeve R, Groeseneken G, Bellens R, Depas M, Maes HE. A consistent model for the thickness dependence of intrinsic breakdown in ultra-thin oxides. In: Int Electron Dev Meeting (IEDM) Tech Dig; 1995. p. 863.

- [2] Kaczer B, Degraeve R, Rasras M, De Keersgieter A, Van de Mieroop K, Groeseneken G. Analysis and modeling of a digital CMOS circuit operation and reliability after gate oxide breakdown: a case study. Microel Reliab 2002;42(4):555–64.

- [3] Degraeve R, Aoulaiche M, Kaczer B, Roussel PhJ, Kauerauf T, Sahhaf S, et al. Review of reliability issues in high-k/metal gate stacks. In: IEEE Int Symp Physical and Failure Analysis of Integrated Circuits (IPFA); 2008. p. 1–6.

- [4] Ralls KS, Skocpol WJ, Jackel LD, Howard RE, Fetter LA, Epworth RW, et al. Discrete resistance switching in submicrometer silicon inversion layers: individual interface traps and low-frequency (1/f?) noise. Phys Rev Lett 1984;52:228–31.

- [5] Kirton MJ, Uren MJ. Noise in solid-state microstructures: a new perspective on individual defects, interface states and low-frequency (1/f) noise. Adv Phys 1989;38:367–468.

- [6] Campbell JP, Qin J, Cheung KP, Yu LC, Suehle JS, Oates A, et al. Random telegraph noise in highly scaled nMOSFETs. In: Proc Int Reliab Phys. Symp (IRPS); 2009. p. 382–8.

- [7] Nagumo T, Takeuchi K, Yokogawa S, Imai K, Hayashi Y. New analysis methods for comprehensive understanding of random telegraph noise. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2009. p. 759–62.

- [8] Nagumo T, Takeuchi K, Hase T, Hayashi Y. Statistical characterization of trap position, energy, amplitude and time constants by RTN measurement of multiple individual traps. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2010. p. 628–31.

- [9] Grasser T, Kaczer B, Goes W, Reisinger H, Aichinger T, Hehenberger P, et al. The paradigm shift in understanding the bias temperature instability: from reaction-diffusion to switching oxide traps. IEEE Trans Electron Dev 2011;58 (11):3652–66.

- [10] HMiki et al. Statistical Measurement of random telegraph noise and its impact in scaled-down high-κ/metal-gate MOSFETs. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2012. p. 19.1.1–19.1.4.

- [11] Simoen E, Romeo T, Pantisano L, Luque Rodríguez A, Jiménez Tejada JA, Aoulaiche M, et al. Insights in low frequency noise of advanced and highmobility channel transistors. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2012. p. 28.7.1–28.7.4.

- [12] Theodorou CG, Ioannidis EG, Haendler S, Planes N, Josse E, Dimitriadis CA, et al. New LFN and RTN analysis methodology in 28 and 14nm FD-SOI MOSFETs. In: Proc Int Reliab Phys Symp (IRPS); 2015. p XT.1.1–XT.1.6.

- [13] Fleetwood D, Brown D, Girard S, Gouker P, Gerardin S, Quinn H, et al. 2015 Special issue of IEEE transactions on nuclear science modeling and simulation of radiation effects. IEEE Trans Nuclear Sci 2015;62(4):1439–706.

- [14] Kaczer B, Roussel PhJ, Grasser T, Groeseneken G. Statistics of multiple trapped charges in the gate oxide of deeply scaled MOSFET devices—application to NBTI. IEEE Electron Dev Lett 2010;31:411.

- [15] Kaczer B, Grasser T, Roussel Ph J, Franco J, Degraeve R, Ragnarsson L-A, et al. Origin of NBTI Variability in Deeply Scaled pFETs. In: Proc Int Reliab Phys Symp (IRPS); 2010. p. 26–32.

- [16] Kaczer B et al. Origins and implications of increased channel hot carrier variability in nFinFETs. In: Proc IEEE Int Reliab Phys Symp (IRPS); 2015. p. 3B.5.1–3B.5.6.

- [17] Kaczer B, Mahato S, Valduga de Almeida Camargo V, Toledano-Luque M, Roussel PhJ, Grasser T, et al. Atomistic approach to variability of biastemperature instability in circuit simulations. In: Proc IEEE Int Reliab Phys Symp (IRPS); 2011. p. XT.3.1–XT.3.5.

- [18] Grasser T, Goes W, Wimmer Y, Schanovsky F, Rzepa G, Waltl M, et al. On the microscopic structure of hole traps in pMOSFETs. In: Int Electron Devices Meeting (IEDM) Tech Dig; 2014. p. 21.1.1–21.1.4.

- [19] Asenov A et al. Advanced simulation of statistical variability and reliability in nano CMOS transistors. In: Int Electron Devices Meeting (IEDM) Tech Dig; 2008. p. 15–17.

- [20] Kuhn KJ, Giles MD, Becher D, Kolar P, Kornfeld A, Kotlyar R, et al. Process technology variation. IEEE Trans Electron Dev 2011;58(8):2197–208.

- [21] Mizutani T, Kumar A, Hiramoto T. Analysis of transistor characteristics in distribution tails beyond ±5.4σ of 11 billion transistors. In: Int Electron Devices Meeting (IEDM) Tech Dig; 2013. p. 33.3.1–33.3.4.

- [22] Pelgrom MJM, Duinmaijer ACJ, Welbers APG. Matching properties of MOS transistors. J Solid State Circ 1989;24:1433.

- [23] Mezzomo CM, Bajolet A, Cathignol A, Di Frenza R, Ghibaudo G. Characterization and modeling of transistor variability in advanced CMOS technologies. IEEE Trans Electron Dev 2011;58(8):2235–48.

- [24] Simicic M, Subirats A, Weckx P, Kaczer B, Franco J, Roussel P, et al. Comparative experimental analysis of time-dependent variability using a transistor array. In: Int Reliab Phys Symp (IRPS); 2016.

- [25] Kerber A. Methodology for determination of process induced BTI variability in MG/HK CMOS technologies using a novel matrix test structure. IEEE Electron Dev Lett 2014;35(3):294–6.

- [26] Roussel P, Degraeve R, Kerber A, Pantisano L, Groeseneken G. Accurate reliability evaluation of non-uniform ultrathin oxynitride and high-k layers. In: Proc IEEE Int Reliab Phys Symp (IRPS); 2003. p. 29–33.

- [27] Angot D et al. BTI variability fundamental understandings and impact on digital logic by the use of extensive dataset. In: Int Electron Devices Meeting (IEDM) Tech Dig; 2013. p. 15.4.1–15.4.4.

- [28] Kaczer B, Franco J, Roussel PhJ, Groeseneken G, Chiarella T, Horiguchi N, et al. Extraction of the random component of time-dependent variability using matched pairs. IEEE Electron Dev Lett 2015;36(4):300–2.

- [29] Procel LM, Crupi F, Franco J, Trojman L, Kaczer B. Defect-centric distribution of channel hot carrier degradation in nano-MOSFETs. IEEE Electron Dev Lett 2014;35(12):1167–9.

- [30] Grasser T, Kaczer B, Goes W. An energy-level perspective of bias temperature instability. In: Proc Int Reliab Phys Symp (IRPS); 2008. p. 28–38.

- [31] El-Sayed AM, Watkins MB, Afanas'ev VV, Shluger AL. Nature of intrinsic and extrinsic electron trapping in SiO<sub>2</sub>. Phys Rev B 2014;89:125201.

- [32] El-Sayed AM, Watkins MB, Grasser T, Afanas'ev VV, Shluger AL. Hydrogeninduced rupture of strained Si–O bonds in amorphous silicon dioxide. Phys Rev Lett 2015:114:115503.

- [33] Grasser T, Reisinger H, Wagner P-J, Schanovsky F, Goes W, Kaczer B. The time dependent defect spectroscopy (TDDS) for the characterization of the bias temperature instability. In: Proc Int Reliab Phys Symp (IRPS); 2010. p. 16–25.

- [34] Grasser T, Rott K, Reisinger H, Wagner P-J, Goes W, Schanovsky F, et al. Advanced characterization of oxide traps: the dynamic time-dependent defect spectroscopy. In: Proc IEEE Int Reliab Phys Symp (IRPS); 2013. p. 2D.2.1– 2D.2.7

- [35] Rzepa G, Waltl M, Goes W, Kaczer B, Grasser T. Microscopic oxide defects causing BTI, RTN, and SILC on high-k FinFETs. In: International Conference on Simulation of Semiconductor Processes and Devices (SISPAD); 2015. p. 144–47.

- [36] Goes W, Waltl M, Wimmer Y, Rzepa G, Grasser T. Advanced modeling of charge trapping: RTN, 1/f noise, SILC, and BTI. In: International Conference on Simulation of Semiconductor Processes and Devices (SISPAD); 2014. p. 77–80.

- [37] Reisinger H, Grasser T, Gustin W, Schlünder C. The statistical analysis of individual defects constituting NBTI and its implications for modeling DC- and AC-stress. In: Proc IEEE Int Reliab Phys Symp (IRPS); 2010. p. 7–15.

- [38] Rzepa G, Goes W, Rott G, Rott K, Karner M, Kernstock C, et al. Physical modeling of NBTI: from individual defects to devices. IN: Int Conf Sim Semicond. Processes Devices (SISPAD); 2014. p. 81–84.

- [39] Weckx P, Kaczer B, Kukner H, Roussel PJ, Raghavan P, Catthoor F, et al. Defect-based methodology for workload-dependent circuit lifetime projections application to SRAM. In: Proc Int Reliab Phys Symp (IRPS); 2013. p. 3A.4.1–3A.4.7.

- [40] Grasser T, Wagner P-J, Reisinger H, Aichinger Th, Pobegen G, Nelhiebel M, et al. Analytic modeling of the bias temperature instability using capture/emission time maps. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2011. p. 27.4.1–27.4.4.

- [41] Rodopoulos D, Weckx P, Noltsis M, Catthoor F, Soudris D. Atomistic pseudotransient BTI simulation with inherent workload memory. IEEE Trans Dev Mater Reliab 2014;14(2):704–14.

- [42] Grasser T, Waltl M, Goes W, Wimmer Y, El-Sayed A-M, Shluger AL, et al. On the volatility of oxide defects: activation, deactivation, and transformation. In: Proc Int Reliab Phys Symp (IRPS); 2015. p. 5A.3.1–5A.3.8.

- [43] Kaczer B, Chen C, Weckx P, Roussel PhJ, Toledano-Luque M, Franco J, et al. Maximizing reliable performance of advanced CMOS circuits—a case study. In: Proc Int Reliab Phys Symp (IRPS); 2014. p. 2D.4.1.

- [44] Toledano-Luque M, Kaczer B, Simoen E, Degraeve R, Franco J, Roussel PhJ, et al. Correlation of single trapping and detrapping effects in drain and gate currents of nanoscaled nFETs and pFETs. In: Proc IEEE Int Reliab Phys Symp(IRPS); 2012. p. XT.5.1—XT.5.6.

- [45] Goes W, Toledano-Luque M, Baumgartner O, Bina M, Schanovsky F, Kaczer B, et al. Understanding correlated drain and gate current fluctuations. In: IEEE Int Symp Physical and Failure Analysis of Integrated Circuits (IPFA); 2013. p. 51–6.

- [46] Bury E, Degraeve R, Cho M, Kaczer B, Goes W, Grasser T, et al. Study of (correlated) trap sites in SILC, BTI and RTN in SiON and HKMG devices. In: IEEE Int Symp Physical and Failure Analysis of Integrated Circuits (IPFA); 2014. p. 250-3.

- [47] Gerrer L, Ding J, Amoroso SM, Adamu-Lema F, Hussin R, Reid D, et al. Modelling RTN and BTI in nanoscale MOSFETs from device to circuit: a review. Microelectron Reliab 2014;54(4):682–97.

- [48] Sonoda K, Ishikawa K, Eimori T, Tsuchiya O. Discrete dopant effects on statistical variation of random telegraph signal magnitude. IEEE Trans Electron Dev 2007;54(8):1918–25.

- [49] Ghetti A, Compagnoni CM, Spinelli AS, Visconti A. Comprehensive analysis of random telegraph noise instability and its scaling in deca-nanometer flash memories. IEEE Trans Electron Dev 2009;56:1746.

- [50] Franco J, Kaczer B, Toledano-Luque M, Roussel PhJ, Groeseneken G, Schwarz B, et al. Reduction of the BTI time-dependent variability in nanoscaled MOSFETs by body bias. In: Proc Int Reliab Phys Symp (IRPS); 2013. p. 2D.3.1–2D.3.6.

- [51] Toledano-Luque M, Kaczer B, Franco J, Roussel PhJ, Bina M, Grasser T, et al. Degradation of time dependent variability due to interface state generation. In: Symp VLSI Technol; 2013. p. T190–T191.

- [52] Franco J, Kaczer B, Toledano-Luque M, Bukhori MF, Roussel PhJ, Mitard J, et al. Impact of single charged gate oxide defects on the performance and scaling of nanoscaled FETs. In: Proc Int Reliab Phys Symp (IRPS); 2012. p. 5A.4.1.

- [53] Franco J, Kaczer B, Toledano-Luque M, Roussel PhJ, Kauerauf T, Mitard J, et al. SiGe channel technology: superior reliability toward ultra-thin EOT devices— Part II: time-dependent variability in nanoscaled devices and other reliability issues. IEEE Trans Electron Dev 2013;60(1):405–12.

- [54] Franco J, Kaczer B, Waldron N, Roussel PhJ, Alian A, Pourghaderi MA, et al. RTN and PBTI-induced time-dependent variability of replacement metal-gate highk InGaAs FinFETs. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2014. p. 2021-2024

- [55] Toledano-Luque M, Kaczer B, Roussel PhJ, Franco J, Ragnarsson L-Å, Grasser T, et al. Depth localization of positive charge trapped in silicon oxynitride field effect transistors after positive and negative gate bias temperature stress. Appl Phys Lett 2011;98:183506.

- [56] Toledano-Luque M, Kaczer B, Franco J, Roussel PhJ, Grasser T, Hoffmann TY, et al. From mean values to distributions of BTI lifetime of deeply scaled FETs through atomistic understanding of the degradation. In: Symp VLSI Technol; 2011. p. 152–3.

- [57] Subirats A, Garros X, El Husseini J, Vincent E, Reimbold G, Ghibaudo G. Modeling the dynamic variability induced by charged traps in a bilayer gate oxide. IEEE Trans Electron Dev 2015;62(2):485–92.

- [58] Weckx P, Kaczer B, Chen C, Franco J, Bury E, Chanda K, et al. Characterization of time-dependent variability using 32k transistor arrays in an advanced HK/MG technology. In: Proc Int Reliab Phys Symp (IRPS); 2015. p. 3B.1.1–3B.1.6.

- [59] Cho M, Roussel PhJ, Kaczer B, Degraeve R, Franco J, Aoulaiche M, et al. Channel hot carrier degradation mechanism in long/short channel n-FinFETs. IEEE Trans Electron Dev 2013;60(12):4002–7.

- [60] Huard V et al. NBTI degradation: from transistor to SRAM arrays. In: Proc Int Reliab Phys Symp (IRPS); 2008. p. 289–300.

- [61] Kaczer B, Toledano-Luque M, Franco J, Weckx P. Statistical distribution of defect parameters. In: Grasser T, editor. Bias temperature instability for devices and circuits. Springer; 2014.

- [62] Magnone P et al. Impact of hot carriers on nMOSFET variability in 45- and 65-nm CMOS technologies. IEEE Trans Electron Dev 2011;58(8):2347-53.

- [63] Kuroda R, Yonezawa A, Teramoto A, Li T-L, Tochigi Y, Sugawa S. A statistical evaluation of random telegraph noise of in-pixel source follower equivalent surface and buried channel transistors. IEEE Trans Electron Dev 2013;60 (10):3555-61.

- [64] Ito K, Matsumoto T, Nishizawa S, Sunagawa H, Kobayashi K, Onodera H. The impact of RTN on performance fluctuation in CMOS logic circuits. In: Proc Int Reliab Phys Symp (IRPS); 2011. p. CR.5.1—CR.5.4.

- [65] Simicic M, Putcha V, Parvais B, Weckx P, Kaczer B, Groeseneken G, et al. Advanced MOSFET variability and reliability characterization array. Presented at IEEE International Integrated Reliability Workshop (IIRW); 2015.

- [66] Weckx P, Kaczer B, Raghavan P, Franco J, Simicic M, Roussel PJ, et al. Characterization and simulation methodology for time-dependent variability in advanced technologies. In: IEEE Custom Integrated Circuits Conference (CICC); 2015. p. 1–8.

- [67] Putcha V, Bury E, Weckx P, Franco J, Kaczer B, Groeseneken G. Design and simulation of on-chip circuits for parallel characterization of ultrascaled transistors for BTI reliability. In: IEEE International Integrated Reliability Workshop (IIRW) Final Report; 2014. p. 99–102.

- [68] Putcha V, Simicic M, Weckx P, Parvais Bertrand, Franco J, Kaczer B, et al. Smartarray for pipelined BTI characterization. In: Presented at IEEE International Integrated Reliability Workshop (IIRW); 2015.

- [69] Weckx P, Kaczer B, Franco J, Roussel PhJ, Bury E, Subirats A, et al. Defect-centric perspective of combined BTI and RTN time-dependent variability. Presented at IEEE International Integrated Reliability Workshop (IIRW); 2015.

- [70] Hussin R, Amoroso SM, Gerrer L, Kaczer B, Weckx P, Franco J, et al. Interplay between statistical variability and reliability in contemporary pMOSFETS: measurements versus simulations. IEEE Trans Electon Dev 2014;61 (9):3265–73.

- [71] Kerber A, Nigam T. Challenges in the characterization and modeling of BTI induced variability in metal gate/high-k CMOS technologies. In: Proc Int Reliab Phys Symp (IRPS); 2013. p. 2D.4.1–2D.4.6.

- [72] Kerber A, Srinivasan P. Impact of stress mode on stochastic BTI n scaled MG/HK CMOS devices. IEEE Electron Dev Lett 2014;35(4):431–4.

- [73] Kwasnick R, Lucero A. Computer reliability: establishing goals and use conditions for IC reliability engineering. In: IEEE Int Reliab Phys Symp (IRPS), Tutorial M4.3; 2014.

- [74] Wang W, Yang S, Bhardwaj S, Vrudhula S, Liu F, Cao Y. The impact of NBTI effect on combinational circuit: modeling, simulation, and analysis. IEEE Trans VLSI Syst 2010;18(2):173–83.

- [75] Eilers R, Metzdorf M, Helms D, Nebel W. Efficient NBTI modeling technique considering recovery effects. In: Proc Int Symp Low Power Electronics and Design (ISLPED); 2014. p. 177–82.

- [76] Giering K-U, Sohrmann C, Rzepa G, Heiss L, Grasser T, Jancke Roland. NBTI modeling in analog circuits and its application to long-term aging simulations. In: IEEE Int Integrated Reliab Workshop (IIRW) Final Report; 2014. p. 29–34.

- [77] Khan S, Agbo I, Hamdioui S, Kukner H, Kaczer B, Raghavan P, et al. Bias temperature instability analysis of FinFET based SRAM cells. In: Design, Automation and Test in Europe (DATE) Conf; 2014. p. 1–6.

- [78] Kukner H, Weckx P, Morrison S, Raghavan P, Kaczer B, Catthoor F, et al. NBTI aging on 32-bit adders in the downscaling planar FET technology nodes. In: Digital System Design (DSD) Euromicro Conference; 2014. p. 98-107.

- [79] Kukner H, Khatib M, Morrison S, Weckx P, Raghavan P, Kaczer B, et al. Degradation analysis of datapath logic subblocks under NBTI aging in FinFET technology. In: Int Symp Quality Electronic Design (ISQED); 2014. p. 473–9.

- [80] Goel N, Dubey P, Kawa J, Mahapatra S. Impact of time-zero and NBTI variability on sub-20nm FinFET based SRAM at low voltages. In: Proc Int Reliab Phys Symp (IRPS); 2015. p. CA.5.1-CA.5.7.

- [81] Weckx P, Kaczer B, Toledano-Luque M, Raghavan P, Franco J, Roussel PhJ, et al. Implications of BTI-induced time-dependent statistics on yield estimation of digital circuits. IEEE Trans Electron Dev 2013;61(3):666–73.

- [82] El Husseini J, Garros X, Cluzel J, Subirats A, Makosiej A, Weber O, et al. Complete characterization and modeling of the BTI-induced dynamic variability of SRAM arrays in 28-nm FD-SOI technology. IEEE Trans Electron Dev 2014:61(12):3991–9.

- [83] Weckx P, Kaczer B, Kukner H, Roussel PhJ, Raghavan P, Catthoor F, et al. Non-Monte-Carlo methodology for high-sigma simulations of circuits under workload-dependent BTI degradation—application to 6T SRAM. In: Proc Int Reliab Phys Symp (IRPS); 2014. p. 5D.2.1–5D.2.6.

- [84] Martin-Martinez J, Ayala N, Rodriguez R, Nafria M, Aymerich X. RELAB: a tool to include MOSFETs BTI and variability in SPICE simulators. In: Int Conf Synthesis, Modeling, Analysis and Simulation Methods and Applications to Circuit Design (SMACD); 2012. p. 249–52.

- [85] Wirth G, da Silva R, Srinivasan P, Krick J, Brederlow R. Statistical model for MOSFET low-frequency noise under cyclo-stationary conditions. In: Int Electron Dev Meeting (IEDM) Tech Dig; 2009. p. 715.

- [86] Lu J, Jiao G, Vaz C, Campbell JP, Ryan JT, Chung KP, et al. PBTI-induced random timing jitter in circuit-speed random logic. IEEE Trans Electron Dev 2014;61 (11):3613–8.

- [87] Kaczer B et al. The defect-centric perspective of device and circuit reliability from individual defects to circuits. In: 45th European Solid State Device Research Conference (ESSDERC); 2015. p. 218–25.