Home Search Collections Journals About Contact us My IOPscience

On the limits of applicability of drift-diffusion based hot carrier degradation modeling

This content has been downloaded from IOPscience. Please scroll down to see the full text.

2016 Jpn. J. Appl. Phys. 55 04ED14

(http://iopscience.iop.org/1347-4065/55/4S/04ED14)

View the table of contents for this issue, or go to the journal homepage for more

Download details:

IP Address: 128.131.68.158

This content was downloaded on 17/03/2016 at 14:39

Please note that terms and conditions apply.

# On the limits of applicability of drift-diffusion based hot carrier degradation modeling

Markus Jech<sup>1\*</sup>, Prateek Sharma<sup>1</sup>, Stanislav Tyaginov<sup>1,2</sup>, Florian Rudolf<sup>1</sup>, and Tibor Grasser<sup>1</sup>

<sup>1</sup>Institute for Microelectronics, TU Wien, Gusshausstrasse 27-29/E-360, 1040 Vienna, Austria

Received September 30, 2015; revised December 18, 2015; accepted January 14, 2016; published online March 16, 2016

We study the limits of the applicability of a drift-diffusion (DD) based model for hot-carrier degradation (HCD). In this approach the rigorous but computationally expensive solution of the Boltzmann transport equation is replaced by an analytic expression for the carrier energy distribution function. On the one hand, we already showed that the simplified version of our HCD model is quite successful for LDMOS devices. On the other hand, hot carrier degradation models based on the drift-diffusion and energy transport schemes were shown to fail for planar MOSFETs with gate lengths of 0.5–2.0 µm. To investigate the limits of validity of the DD-based HCD model, we use planar nMOSFETs of an identical topology but with different gate lengths of 2.0, 1.5, and 1.0 µm. We show that, although the model is able to adequately represent the linear and saturation drain current changes in the 2.0 µm transistor, it starts to fail for gate lengths shorter than 1.5 µm and becomes completely inadequate for the 1.0 µm device. © 2016 The Japan Society of Applied Physics

#### 1. Introduction

Hot carrier degradation (HCD) is one of the key issues in the field of reliability of microelectronic devices, in particular of MOSFETs.<sup>1)</sup> However, for a proper physics-based description of this complex phenomenon, one needs a detailed knowledge about the carrier transport in the targeted devices.<sup>2–13)</sup> Hot-carrier degradation is accepted to be driven by the generation of traps at or near the Si/SiO<sub>2</sub> interface. These traps are assumed to be generated by the dissociation of pristine Si-H bonds. This process can be induced either by cold or hot carriers<sup>2,5,7,9)</sup> which trigger the multiple- or singlecarrier bond-breakage mechanisms. Note that in a real device subjected to hot-carrier stress both cold and hot carriers are present, and thus both mechanisms contribute. 14,15) As a consequence, to evaluate the rates of these two competing processes one needs to distinguish between "cold" and "hot" carriers. Therefore, the key point in HCD modeling is to know how carriers are distributed over energy.

This information is provided by the carrier energy distribution functions (DFs), which can be obtained from a solution of the Boltzmann transport equation (BTE).<sup>8,16)</sup> Usually the BTE is solved either by a stochastic Monte-Carlo method, 16) or a deterministic method based on a spherical harmonics expansion (SHE)<sup>8,17</sup> of the carrier DFs. However, even for ultra-scaled planar CMOS devices these methods are computationally challenging and time consuming. Thus, the former one requires substantial computational effort, while the latter one requires a massive amount of memory to store all variables. 16) Devices with larger dimensions or non-planar interfaces and geometrical features, like LDMOS devices, dramatically aggravate this situation, making the modeling of HCD intricate. As a result, simplified approaches to the BTE solution have attracted attention. 12,18-23) These simplified techniques are often based on the moments of the Boltzmann transport equation, usually the drift-diffusion (DD) scheme, and are computationally far more inexpensive than the aforementioned ones.

We have recently proposed an HCD model for LDMOS transistors based on the DD scheme, <sup>22,24,25)</sup> which uses an analytic expression that considers both high and low energy carriers. The problem, of course, is that the energy distribution functions in LDMOS devices have different shapes

compared to those in planar nMOSFET structures. In Ref. 19 it was suggested that the DD scheme is applicable to devices with gate lengths longer than  $0.5\,\mu m$ . However, as we have shown in Ref. 21, drift-diffusion and even hydrodynamic approaches can be inadequate for modeling HCD in nMOSFETs with gate lengths of  $2.0\,\mu m$ . Thus, in this context, the analysis of the limits of the validity of the DD-based model is a very important task. For this purpose, we use a series of planar nMOSFET structures of a similar architecture but with different gate lengths.

#### 2. Simulation framework

Our HCD model covers and links the three main aspects of hot-carrier degradation: carrier transport treatment in the semiconductor with the evaluation of the carrier energy distribution function, a microscopic description of the defect generation kinetics at the  $\mathrm{Si/SiO_2}$  interface, and simulation of the degraded device. First the carrier DFs are computed for a particular device geometry and given stress/operating conditions. These DFs are then used to evaluate the bond-breakage rates, and hence to simulate the interface state density  $N_{\mathrm{it}}$  as a function of the lateral coordinate x for each stress time step t. The obtained  $N_{\mathrm{it}}(x,t)$  profiles are then used to simulate the characteristics of the degraded devices.

In this work we compare the results of two versions of our HCD model which differ only in the way the carrier energy distribution functions are obtained. The reference model employs the BTE solution produced by the open source deterministic BTE solver ViennaSHE, which is based on the spherical harmonics expansion of the carrier DF.<sup>26)</sup> The second version of the model is computationally less expensive and relies on an analytic expression for the carrier DF based on macroscopic device quantities obtained from the DD scheme.<sup>22,24)</sup>

### 2.1 Carrier transport

The carrier energy distribution function is the most important information and one of the two main constituents of our physics-based HCD model. The full version of our model employs the deterministic solver ViennaSHE for evaluating the DFs and is used as a reference for validating the DD-based approach. The DD approach represents the DFs by an analytic expression with the parameters linked to

<sup>&</sup>lt;sup>2</sup> Ioffe Physical-Technical Institute, Polytechnicheskaya 26, 194021 St-Petersburg, Russia

<sup>\*</sup>E-mail: jech@iue.tuwien.ac.at

the moments of the BTE.<sup>22,24)</sup> In recent years extensive efforts were made to develop different analytical approaches/expressions trying to mimic the shape of the DF in different regions. Some of such expressions are the heated Maxwellian,<sup>27)</sup> the approach developed by Cassi et al.,<sup>18)</sup> Hasnat et al.<sup>19)</sup> and the Reggiani approach.<sup>12)</sup> Our model uses the following expression for the DF:<sup>24)</sup>

$$f(\varepsilon) = A \exp\left[-\left(\frac{\varepsilon}{\varepsilon_{\text{ref}}}\right)^b\right] + C \exp\left(-\frac{\varepsilon}{k_{\text{B}}T_{\text{L}}}\right),$$

(1)

where the first term accounts for hot carriers in the ensemble and the second, Maxwellian term, represents the contribution of cold, thermalized, carriers. The parameters A, C, and  $\varepsilon_{\rm ref}$  are determined by the moments of the BTE and the DFs normalization criterion:

$$\int_{0}^{\infty} f(\varepsilon) d\varepsilon = 1,$$

$$\int_{0}^{\infty} f(\varepsilon)g(\varepsilon) d\varepsilon = n,$$

$$\int_{0}^{\infty} Ef(\varepsilon)g(\varepsilon) d\varepsilon = \frac{3}{2} nk_{\rm B}T_{\rm n}.$$

(2)

Further knowledge about the density of states  $g(\varepsilon)$  and the carrier temperature  $T_n$  is required. The density of states is modeled by an expression proposed in Ref. 28:

$$g(\varepsilon) = g_0 \sqrt{\varepsilon} (1 + \eta \varepsilon),$$

(3)

which provides an excellent approximation to the typically used non-parabolic model of Kane but has the advantage of being analytically integrable Under quasi-equlibrium conditions in long channel devices, the carrier temperature can be approximately obtained by

$$T_{\rm n} = T_{\rm L} + \frac{2}{3} \frac{q}{k_{\rm P}} \tau \mu F^2,$$

(4)

where  $T_{\rm L}$  is the lattice temperature,  $\tau$  the energy relaxation time, F the electric field, and  $\mu$  the carrier mobility. All of these parameters can be evaluated from the drift-diffusion simulation. It is worth to emphasize that in our recent publication<sup>23)</sup> we have compared our analytic expression for the carrier DF against those used in the aforementioned models in the context of hot-carrier degradation. It was shown that our model is the most suitable one for an adequate description of HCD and will thus be used in the following.

### 2.2 Defect generation

The second important sub-module of our physics-based HCD model is the detailed microscopical description of defect generation. Si–H bonds at the Si/SiO<sub>2</sub> interface can be excited and eventually broken by electrons and holes of different energies. These bonds will be converted into electrically active interface traps which, when occupied, disturb the electrostatics and degrade the mobility due to additional charged scattering centres.

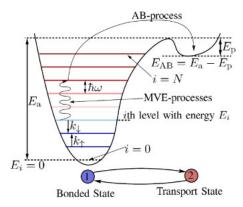

In our model these Si–H bonds are treated within the truncated harmonic oscillator model (see Fig. 1), which can be excited via two main competing pathways. The first one is called "AB-process". It can occur if a solitary high-energetic carrier hits the bond. In this scenario one of the bonding electrons is excited to an antibonding (AB) state. The second pathway is related to multivibrational excitations (MVE) of

**Fig. 1.** (Color online) A schematic representation of the truncated harmonic oscillator model used for the derivation of our physics-based HCD model. The Si–H bond is ruptured at the transition from the bonded state 1 to the transport state 2. The required activation energy  $E_a$  for overcoming this barrier can be effectively lowered by the interplay between the AB- and the MVE-mechanism.

the bond and is referred to as the "MVE-process". In this case the bond is subsequently bombarded by a series of carriers with energies below the threshold for triggering the AB-mechanism and is therefore able to climb up the ladder of eigenstates of the harmonic oscillator. Note that we also consider all possible superpositions of the AB- and MVE-mechanism. This means that the bond can be preheated, i.e., excited to an intermediate level, by a cascade of colder carriers. The potential barrier, separating the bonded and the transport state, is reduced and the probability of finding a single carrier with sufficient energy to overcome this barrier is higher.

Two additional factors, which affect the trap generation rates, are also implemented in our HCD model. First, the reduction of the activation energy  $E_{\rm a}$  due to the interaction of the oxide field with the dipole moment of the bond, <sup>6,29)</sup> and second, stochastic variations of  $E_{\rm a}$  caused by structural disorder. <sup>30,31)</sup>

The corresponding rates for the AB- and MVE-process are determined by the carrier acceleration integral (AI):<sup>9,10,32,33)</sup>

$$I_{\text{AB/MVE}} = \int_0^\infty f(\varepsilon)g(\varepsilon)v(\varepsilon)\sigma_0(\varepsilon - \varepsilon_{\text{th}})^p d\varepsilon, \tag{5}$$

where  $f(\varepsilon)$  is the DF,  $g(\varepsilon)$  the density of states (DOS),  $v(\varepsilon)$  the carrier group velocity, and  $\sigma_0(\varepsilon)$  the reaction cross section.

### 2.3 Simulations of the degraded devices

The  $N_{\rm it}(x,t)$  profiles generated using the information of the carrier DFs, are then loaded into the device and circuit simulator MiniMOS-NT<sup>34)</sup> (based on the drift-diffusion and energy transport schemes) used in the GTS framework, <sup>35)</sup> which models the characteristics of the degraded devices. One of the important ingredients needed for the simulations of the degraded devices is a proper mesh. This mesh should be fine enough in all crucial device segments but still contain a moderate number of elements. To achieve this goal the adaptive meshing framework ViennaMesh, which generates meshes based on the gradient of the built-in potential containing a reasonable number of cells, is used. <sup>36,37)</sup>

In our recent work we have already presented and validated both versions of the model in the context of hot-carrier degradation in LDMOS devices. 15,22) N- and

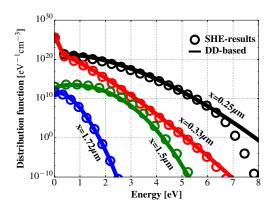

Fig. 2. (Color online) Electron DFs simulated for  $V_{\rm GS}=18\,\rm V$  and  $V_{\rm DS}=2.0\,\rm V$  at different values of the lateral coordinate for the nLDMOS device with the deterministic solver ViennaSHE (symbols) and with the DD-based analytical approach (lines).

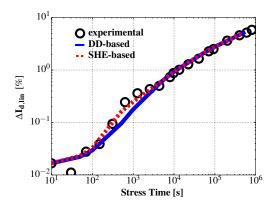

Fig. 3. (Color online)  $\Delta I_{D,lin}(t)$  degradation traces: experiment (symbols) vs simulation using the full (dashed)- and the DD-based (solid) model.

p-channel LDMOS transistors were stressed at different combinations of  $V_{\rm GS}$  and  $V_{\rm DS}$  voltages and the changes of the linear and saturation drain current ( $\Delta I_{\rm D,lin}$  and  $\Delta I_{\rm D,sat}$ ) were recorded. Figure 2 shows the carrier energy distribution functions simulated for the nLDMOS transistor for different device sections, i.e., at the bird's beak and near the drain, with ViennaSHE and the DD-based analytical model for  $V_{\rm GS}=18\,{\rm V}$  and  $V_{\rm DS}=2.0\,{\rm V}$ . As can be seen, the agreement between the DFs is very good. Figure 3 shows the characteristics of the nLDMOS devices stressed at the same voltages as those used in Fig. 2 within a stress time window of up to 1 Ms. One can see that the simulated DFs with different approaches are in very good agreement as both versions of the model lead to very similar theoretical  $\Delta I_{\rm D,lin}(t)$  and  $\Delta I_{\rm D,sat}(t)$  traces and can properly represent the experimental data

In order to analyze whether the DD-based model is able to capture HCD in planar structures with shorter channel lengths, we have generated a series of three devices with a similar topology but different gate lengths  $L_{\rm G}$ , namely 2.0, 1.5, and 1.0  $\mu$ m. To generate the structure of these devices we used the Sentaurus process simulator. <sup>38)</sup>

## 3. Results and discussion

While applying both versions of our HCD model to planar nMOSFETs, we have used more typical stress voltages for these transistors as compared to the reference nLDMOS device, i.e.,  $V_{\rm GS} = 7.5\,\rm V$  and  $V_{\rm DS} = 2.5\,\rm V$ , see Refs. 32, 39,

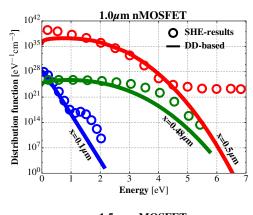

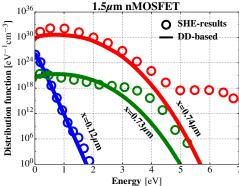

**Fig. 4.** (Color online) Electron distribution functions at different lateral positions along the channel for the three nMOSFETs with  $L_{\rm G}=1.0,\,1.5,\,{\rm and}\,2.0\,{\rm \mu m}$  simulated with ViennaSHE and the DD-based version of the model. Symbols correspond to ViennaSHE results, solid lines to results obtained with the analytic approach.

and 40. We simulated electron DFs, interface state density profiles  $N_{\rm it}(x)$ , and degradation traces  $\Delta I_{\rm D,lin}(t)$  as well as  $\Delta I_{\rm D,sat}(t)$  for up to 50 ks.

Figure 4 summarizes the simulated electron energy distribution functions obtained with ViennaSHE and the DD-based approach at different lateral coordinates along the channel. At low and moderate energies the DFs computed with the analytic approach Eq. (1) reasonably mimic the DFs obtained from a BTE solution of ViennaSHE. However, at higher energies, the curvatures of the DFs evaluated with the two approaches are different. It can be seen that the accuracy deteriorates for shorter channel lengths. On the other hand, the occupation numbers at these energies have already dropped by several orders of magnitude, and it is not obvious whether this discrepancy in the DFs translates into a sizeable error in the interface state profiles  $N_{\rm it}(x)$  and the  $\Delta I_{\rm D,lin/sat}$  degradation traces.

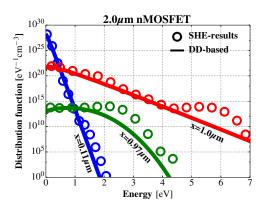

**Fig. 5.** (Color online) Acceleration integrals for the AB- and the MVE-process calculated from the DFs obtained from the DD-based model (solid lines) and ViennaSHE (dashed lines) for  $V_{\rm GS} = 7.5 \, {\rm V}$  and  $V_{\rm DS} = 2.5 \, {\rm V}$ .

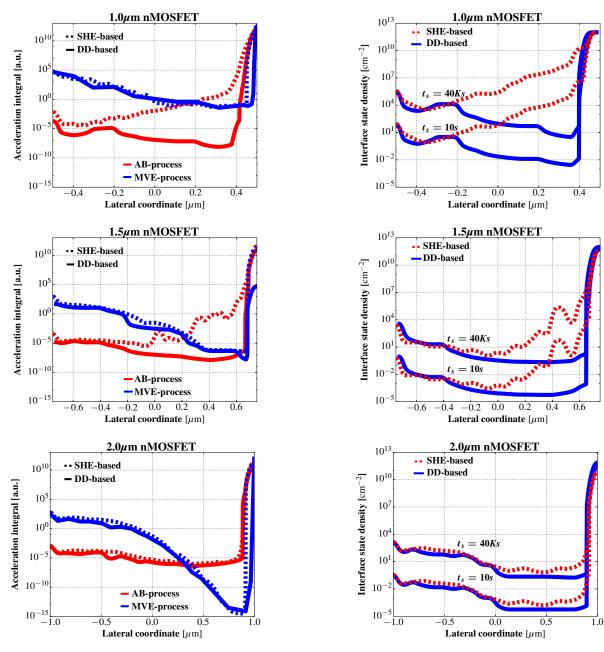

**Fig. 6.** (Color online)  $N_{\rm it}(x)$  profiles evaluated for the three nMOSFETs with gate lengths  $L_{\rm G}=1.0,\,1.5,\,{\rm and}\,2.0\,{\rm \mu m}$  by both versions of the model for stress times of 10 s and 40 ks.

To check this in a greater detail we plot the acceleration integrals, which determine the corresponding rates, for the AB- and the MVE-mechanism simulated along the Si/SiO<sub>2</sub> interface with both versions of the model (see Fig. 5). For the 2 µm device the bond-breakage rates for the AB- and MVE-process are almost the same. This reflects the good agreement of the DFs in Fig. 4. For the shorter structures, the acceleration integrals of both mechanisms calculated with the two versions of the model are significantly different. Since in these devices the interface state profiles  $N_{it}(x)$ , and therefore also the degradation, are mainly determined by the ABprocess, the DD-based version of our model should be able to properly capture the HCD traces for the 1.5 µm structure. The situation deteriorates for the shortest device. Although the contribution of the MVE-mechanism is properly represented by the simplified approach, the bond-breakage rates of the AB-process are profoundly underestimated. While the SHE-

based versions predicts a significant build up of interface states in the channel, triggered by the interplay between the AB- and MVE-mechanism, which is not adequately described by the DD-based approach.

In order to investigate the mismatch of the DFs (Fig. 4) and the impact of the bond-breakage rates (Fig. 5) onto the interface trap profiles, we plot the  $N_{\rm it}(x)$  values simulated with both versions of the model (see Fig. 6). One can see that in the case of the longest device, i.e., the 2 µm nMOSFET structure, the  $N_{\rm it}(x)$  profiles are very similar. This is caused by the fact that the electron DFs are properly approximated by the DD-based model as can be seen in Fig. 4. The situation starts to change for the shorter structure with  $L_{\rm G}=1.5\,\mu{\rm m}$ , i.e., agreement between both models deteriorates. For the device with  $L_{\rm G}=1.5\,\mu{\rm m}$  the discrepancy between the  $N_{\rm it}(x)$  values is visible at  $N_{\rm it}\sim 10^8\,{\rm cm}^{-2}$ . The  $N_{\rm it}$  peak at the drain side becomes broader and is shifted towards the channel as

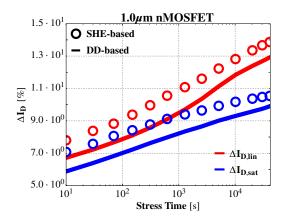

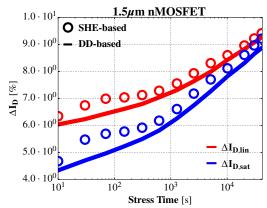

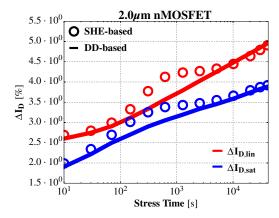

**Fig. 7.** (Color online)  $\Delta I_{\text{D,lin}}$  and  $\Delta I_{\text{D,sat}}$  degradation curves obtained for the three nMOSFETs with both versions model.

can be concluded from Fig. 5. The DD-based approach is not able to capture this trend. Since  $N_{\rm it}$  values of  $\sim 10^8\,{\rm cm}^{-2}$  do not contribute to the total device degradation, a significant deviation between the  $\Delta I_{\rm D,lin/sat}$  degradation curves simulated by the two model versions is not expected. For the shortest device, however, the interface trap densities already differ by about  $\sim 10^{12}\,{\rm cm}^{-2}$ . Such large values provide a considerable contribution to HCD and lead to a visible discrepancy between the drain current degradation traces.

As a result, best correspondence between  $\Delta I_{\rm D,lin/sat}$  obtained with the SHE- and DD-based models is achieved for the 2.0  $\mu$ m nMOSFET (see Fig. 7). Note, however, that even for this device the analytic model leads to lower  $\Delta I_{\rm D,lin/sat}$  values at short stress times. This is because, as we showed in Refs. 22 and 25, short-term HCD is determined by the DFs at the drain, which are underestimated by the DD-based model (see Fig. 4). The same argument also holds for

the  $1.5\,\mu m$  device where the agreement is still reasonable. Hot carrier degradation is slightly underestimated over the whole stress time range due to the mismatch of the interface state profiles visible in Fig. 6. For the shortest device the DD-based model completely fails to properly reproduce the data evaluated with the full model. This already becomes evident in Figs. 4–6 where one can see that the DD-based model is not capable of reasonable mimicking the ViennaSHE results, respectively the big discrepancies between the shape of the interface state profiles.

#### 4. Conclusion

We have found that the drift-diffusion based hot-carrier degradation model works reasonably well in terms of the carrier distribution functions, bond-breakage rates, interface state density profiles, and changes of device characteristics such as the saturation and drain currents for MOSFETs with channels longer than 1.5 µm. The reason is that the DD-based model is not able to catch more complicated DF shapes visible in shorter devices. This is especially pronounced at high energies because the DFs simulated with ViennaSHE and by the DD-based HCD model have different curvatures.

In the case of the 2 µm device the curvature change occurs only when the DF values have dropped by several orders of magnitude, and therefore such a discrepancy does not translate into mismatches between bond-breakage rates,  $N_{it}(x)$ profiles and  $\Delta I_{D,lin}(t)$ ,  $\Delta I_{D,sat}(t)$  degradation traces. As for shorter devices, the discrepancy in the DF curvature appears at higher population numbers, and thus is related to more pronounced errors. In the device with  $L_G = 1.5 \,\mu m$  this results in a mismatch in  $N_{it}(x)$  profiles visible at  $10^8 \,\mathrm{cm}^{-2}$ , and thereby does not substantially impact the  $\Delta I_{\text{D,lin}}(t)$ ,  $\Delta I_{\text{D,sat}}(t)$ changes. As for the shortest nMOSFET, Nit values differ severely at values of 10<sup>12</sup> cm<sup>-2</sup>, and hence the changes of the linear and saturation drain currents simulated with the two versions of the model are completely inconsistent. To summarize, our DD-based model for hot-carrier degradation works properly for the device with  $L_G = 2.0 \,\mu\text{m}$ , it is still applicable in the case  $L_G = 1.5 \,\mu\text{m}$ , and fails for  $L_G = 1.0 \,\mu\text{m}$ .

## Acknowledgments

The authors acknowledge support by the Austrian Science Fund (FWF), Grant P23598 and by the European Union FP7 projects ATHENIS 3D (Grant No. 619246) and MoRV (Grant No. 619234).

- 1) International Technology Roadmap for Semiconductors (ITRS), 2013.

- W. McMahon, K. Matsuda, J. Lee, K. Hess, and J. Lyding, Proc. Int. Conf. Modeling and Simulation of Microsystem, 2002, p. 576.

- W. McMahon, A. Haggag, and K. Hess, IEEE Trans. Nanotechnol. 2, 33 (2003).

- A. Bravaix and V. Huard, Proc. European Symp. Reliability of Electron Devices Failure Physics and Analysis (ESREF), Tutorial, 2010, p. 1267.

- A. Bravaix, C. Guerin, V. Huard, D. Roy, J.-M. Roux, and E. Vincent, Proc. Int. Reliability Physics Symposium (IRPS), 2009, p. 531.

- 6) C. Guerin, V. Huard, and A. Bravaix, J. Appl. Phys. **105**, 114513 (2009).

- S. Tyaginov and T. Grasser, Proc. Int. Integrated Reliability Workshop (IIRW), 2012, p. 206.

- M. Bina, K. Rupp, S. Tyaginov, O. Triebl, and T. Grasser, IEDM Tech. Dig., 2012, p. 713.

- M. Bina, S. Tyaginov, J. Franco, K. Rupp, Y. Wimmer, D. Osinstev, B. Kaczer, and T. Grasser, IEEE Trans. Electron Devices 61, 3103 (2014).

- S. Tyaginov, M. Bina, J. Franco, Y. Wimmer, D. Osintsev, B. Kaczer, and T. Grasser, Proc. Simulation of Semiconductor Processes and Devices (SISPAD), 2014, p. 89.

- A. Zaka, P. Palestri, Q. Rafhay, R. Clerc, M. Iellina, D. Rideau, C. Tavernier, G. Pananakakis, H. Jaouen, and L. Selmi, IEEE Trans. Electron Devices 59, 983 (2012).

- S. Reggiani, G. Barone, E. Gnani, A. Gnudi, G. Baccarani, S. Poli, R. Wise, M.-Y. Chuang, W. Tian, S. Pendharkar, and M. Denison, Solid-State Electron. 102, 25 (2014).

- S. Reggiani, G. Barone, S. Poli, E. Gnani, A. Gnudi, G. Baccarani, M.-Y. Chuang, W. Tian, and R. Wise, IEEE Trans. Electron Devices 60, 691 (2013).

- S. Tyaginov, M. Bina, J. Franco, Y. Wimmer, F. Rudolf, H. Enichlmair, J.-M. Park, B. Kaczer, H. Ceric, and T. Grasser, Proc. Int. Integrated Reliability Workshop (IIRW), 2014, p. 63.

- P. Sharma, S. Tyaginov, M. Jech, Y. Wimmer, F. Rudolf, H. Enichlmair, J.-M. Park, H. Ceric, and T. Grasser, Solid-State Electron, 115, 185 (2016).

- C. Jungemann and B. Meinerzhagen, Hierarchical Device Simulation (Springer, New York, 2003).

- 17) K. Rupp, T. Grasser, and A. Jungel, IEDM Tech. Dig., 2011, p. 789.

- 18) D. Cassi and B. Ricco, IEEE Trans. Electron Devices 37, 1514 (1990).

- K. Hasnat, C.-F. Yeap, S. Jallepalli, S. Hareland, V. Agostinelli, A. Tasch, and C. Maziar, IEEE Trans. Electron Devices 44, 129 (1997).

- C. Fiegna, F. Venturi, M. Melanotte, E. Sangiorgi, and B. Ricco, IEEE Trans. Electron Devices 38, 603 (1991).

- S. Tyaginov, I. Starkov, C. Jungemann, H. Enichlmair, J.-M. Park, and T. Grasser, Proc. European Solid-State Device Research Conf. (ESSDERC), 2011, p. 151.

- 22) P. Sharma, S. Tyaginov, Y. Wimmer, F. Rudolf, K. Rupp, M. Bina, H. Enichlmair, J.-M. Park, R. Minixhofer, H. Ceric, and T. Grasser, IEEE Trans. Electron Devices 62, 1811 (2015).

- P. Sharma, S. Tyaginov, Y. Wimmer, F. Rudolf, H. Enichlmair, J.-M. Park, H. Ceric, and T. Grasser, Microelectron. Reliab. 55, 1427 (2015).

- 24) P. Sharma, S. Tyaginov, Y. Wimmer, F. Rudolf, H. Enichlmair, J.-M. Park,

- H. Ceric, and T. Grasser, Int. EUROSOI Workshop/Int. Conf. Ultimate Integration on Silicon (EUROSOI-ULIS), 2015, p. 21.

- 25) Y. Wimmer, S. Tyaginov, F. Rudolf, K. Rupp, M. Bina, H. Enichlmair, J.-M. Park, R. Minixhofer, H. Ceric, and T. Grasser, Proc. Int. Integrated Reliability Workshop (IIRW), 2014, p. 58.

- 26) Web [http://viennashe.sourceforge.net/].

- T. Grasser, T.-W. Tang, H. Kosina, and S. Selberherr, Proc. IEEE 91, 251 (2003).

- T. Grasser, H. Kosina, C. Heitzinger, and S. Selberherr, J. Appl. Phys. 91, 3869 (2002).

- 29) J. McPherson, Proc. Int. Reliability Physics Symp. (IRPS), 2007, p. 209.

- G. Pobegen, S. Tyaginov, M. Nelhiebel, and T. Grasser, IEEE Electron Device Lett. 34, 939 (2013).

- 31) A. Stesmans, Appl. Phys. Lett. 68, 2076 (1996).

- 32) S. E. Tyaginov, I. A. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello, J. M. Park, H. Enichlmair, M. Karner, C. Kernstock, E. Seebacher, R. Minixhofer, H. Ceric, and T. Grasser, Proc. Int. Symp. Physical and Failure Analysis of Integrated Circuits (IPFA), 2010.

- S. Tyaginov, M. Bina, J. Franco, D. Osintsev, O. Triebl, B. Kaczer, and T. Grasser, Proc. Int. Reliability Physics Symp. (IRPS), 2014, XT.16-1.

- MiniMOS-NT Device and Circuit Simulator (Institute for Microelectronic, TU Wien).

- 35) Web [http://www.globaltcad.com/en/products/minimos-nt.html].

- 36) Web [http://viennamesh.sourceforge.net/].

- F. Rudolf, J. Weinbub, K. Rupp, and S. Selberherr, J. Comput. Appl. Math. 270, 166 (2014).

- Sentaurus Process: Advanced Simulator for Process Technologies (Synopsis).

- S. Tyaginov, I. Starkov, O. Triebl, J. Cervenka, C. Jungemann, S. Carniello,

J. Park, H. Enichlmail, C. Kernstock, E. Seebacher, R. Minixhofer, H.

Ceric, and T. Grasser, Microelectron. Reliab. 50, 1267 (2010).

- S. Tyaginov, I. Starkov, O. Triebl, H. Ceric, T. Grasser, H. Enichlmair, J.-M. Park, and C. Jungemann, Proc. Int. Conf. Simulation of Semiconductor Processes and Devices (SISPAD), 2011, p. 123.