# Bias-temperature instability on the back gate of single-layer double-gated graphene field-effect transistors

Yury Yu. Illarionov<sup>1,2</sup>, Michael Waltl<sup>1</sup>, Anderson D. Smith<sup>3</sup>, Sam Vaziri<sup>3</sup>, Mikael Ostling<sup>3</sup>, Max C. Lemme<sup>4</sup>, and Tibor Grasser<sup>1</sup>

Received September 29, 2015; revised November 5, 2015; accepted November 6, 2015; published online February 24, 2016

We study the positive and negative bias-temperature instabilities (PBTI and NBTI) on the back gate of single-layer double-gated graphene field-effect transistors (GFETs). By analyzing the resulting degradation at different stress times and oxide fields we show that there is a significant asymmetry between PBTI and NBTI with respect to their dependences on these parameters. Finally, we compare the results obtained on the high-*k* top gate and SiO<sub>2</sub> back gate of the same device and show that SiO<sub>2</sub> gate is more stable with respect to BTI. © 2016 The Japan Society of Applied Physics

#### 1. Introduction

Graphene is a superior two-dimensional (2D) material which is characterized by unique physical and electrical properties, such as an extremely high room-temperature carrier mobility<sup>1,2)</sup> and high saturation velocity.<sup>3)</sup> A nice compatibility of this material with standard CMOS technology<sup>4)</sup> is especially crucial for enhancement of the performance and functionality of advanced microelectronic devices and, consequently, silicon integrated circuits. Therefore, in the meantime graphene is considered a promising candidate for various industrial applications. In particular, different groups have recently succeeded in fabricating graphene field effect transistors (GFETs)<sup>5-10)</sup> and related electronic devices.<sup>11,12)</sup> These achievements create a demand for characterization of the reliability of these devices. Nevertheless, only a few attempts to study the reliability of GFETs with respect to bias-temperature instabilities (BTI) have been undertaken by other groups. 13-16) At the same time, we have reported several studies for both BTI and hot-carrier degradation (HCD) in single-layer double-gated GFETs. 17-20) However, only the reliability of high-k top gate oxide has been examined in our previous works.

Here we study the bias-temperature instability resulting from a voltage applied on the  $SiO_2$  back gate of double-gated GFET. We show that there is an asymmetry between positive and negative BTI (PBTI and NBTI) in terms of the degradation magnitude and its dependence on the stress oxide field. Finally, we compare the results obtained on the  $SiO_2$  back gate and high-k top gate of the same device.

### 2. Devices

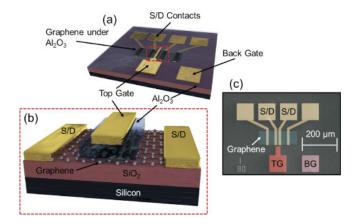

We perform our study on single-layer double-gated GFETs fabricated on a thermally oxidized silicon substrate using a standard lithography process. An isometric view and a schematic cross-section of these devices are given in Fig. 1. Contrary to our previous works,  $^{17-20)}$  the thickness of the SiO2 layer in these devices is 92 nm rather than 1800 nm. This allowed us to observe back gate BTI at reasonable stress voltages. The top gate insulator is a 25 nm thick  $Al_2O_3$  layer, while the channel has a length of 4  $\mu m$  and a width of 80  $\mu m$ . Also, in order to reduce the device-to-device variability, the

**Fig. 1.** (Color online) (a) Schematic layout of the double-gated single-layer GFET. (b) A cross-section of the channel region. The graphene channel is sandwiched between  $Al_2O_3$  as a top gate insulator and  $SiO_2$  as a back gate insulator. (c) Top view of the investigated double-gated GFET obtained using scanning-electron microscopy (SEM). The top gates and source/drain pads are made of Ti/Au and the back gates of Al.

devices have been baked at T = 300 °C for 5 h before the experiments.

### 3. Experiment

All our experiments were performed in vacuum ( $\sim 10^{-5}$  Torr), in order to avoid the detrimental impact of the environment. The BTI dynamics were examined as follows: after measuring the reference gate transfer characteristics, the subsequent stresses with increasing  $V_{\rm BG}-V_{\rm D}$  (back gate voltage minus Dirac point voltage) and top gate voltage  $V_{\rm TG}=0$  were applied. The resulting gate transfer characteristics were measured after each stress using  $V_{\rm d}=20\,{\rm mV}$ , while in some cases the recovery of the stressed device was monitored as well. This allowed us to capture the degradation magnitude versus the stress oxide field  $F_{\rm ox}$ . A similar technique with increasing  $V_{\rm TG}-V_{\rm D}$  and  $V_{\rm BG}=0$  was applied for the top gate BTI measurements.

## 4. Back gate BTI: Stress oxide field dependence and recovery

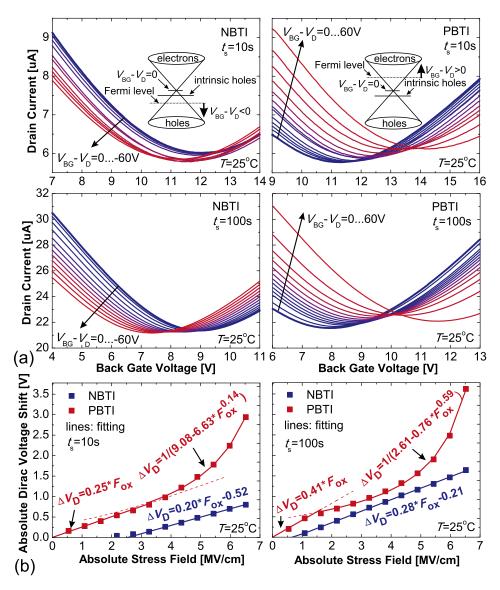

In Fig. 2(a) we show the measured evolution of the back gate

<sup>&</sup>lt;sup>1</sup>Institute for Microelectronics, TU Wien, 27-29 Gusshausstr., 1040 Vienna, Austria

<sup>&</sup>lt;sup>2</sup> loffe Physical-Technical Institute, Polytechnicheskaya 26, 194021 St-Petersburg, Russia

<sup>&</sup>lt;sup>3</sup>KTH Royal Institute of Technology, 22 Isafjordsgatan, 16440 Kista, Sweden

<sup>&</sup>lt;sup>4</sup>University of Siegen, 3 Holderlinstrasse, 57076 Siegen, Germany

Fig. 2. (Color online) (a) Evolution of the back gate transfer characteristics after subsequent stresses with increasing  $V_{BG} - V_D$  and two different stress times for NBTI (left) and PBTI (right). (b) The resulting  $V_D$  shift versus stress oxide field for  $t_S = 10 \text{ s}$  (left) and  $t_S = 100 \text{ s}$  (right).

transfer characteristics after the subsequent NBTI and PBTI stresses with  $V_{BG} - V_D$  varied from 0 to  $\pm 60$  V in  $\pm 5$  V steps. As was suggested in Refs. 17 and 18, we express the degradation magnitude in terms of a Dirac point voltage shift  $\Delta V_{\rm D}$ . This quantity is directly linked to the charged trap density shift  $\Delta N_{\rm T} = \Delta V_{\rm D} C_{\rm ox}/q$  with  $C_{\rm ox}$  being the oxide capacitance. The resulting dependences of  $\Delta V_{\rm D}$  on the stress oxide field  $F_{\text{ox}} = (V_{\text{BG}} - V_{\text{D}})/d_{\text{ox}}$  are plotted in Fig. 2(b) for the stress times  $t_s = 10$  and 100 s. Contrary to Si technologies, in both cases PBTI degradation is stronger than its NBTI counterpart. Moreover, there is a significant difference between PBTI and NBTI with respect to the dependence of the observed Dirac voltage shifts on the stress oxide field. While the NBTI shift linearly increases versus  $F_{ox}$ , growth of PBTI shift is linear only at small  $F_{ox}$  and can be fitted with a Langmuir power law  $f(x) = 1/(a - bx^c)$  at larger oxide fields. At the same time, for both NBTI and PBTI the slopes in the linear regions increase versus  $t_s$ . This is because the probability of carrier trapping becomes larger for longer stresses.

Interestingly, transition of PBTI curves to a Langmuir-like behavior takes place at smaller  $F_{\rm ox}$  if  $t_{\rm s}$  is larger. This leads to a smaller difference between PBTI and NBTI shifts at

moderate  $t_s$ , although PBTI still remains stronger than NBTI [Fig. 2(b), right]. Since in GFETs PBTI is associated with electron trapping and NBTI is due to hole trapping, we assume that the main reason for the observed behavior is the difference in the kinetics of the two processes, as well as the energetic alignment of the trap bands with the Fermi level in the graphene channel. Another issue which contributes the asymmetry between NBTI and PBTI is the positive initial values of  $V_D$ , which are typical for all our GFETs. This means that our graphene is p-doped, i.e., some intrinsic holes are present even if  $V_{BG} = 0$ . Most likely, trapping of these intrinsic holes is less efficient, especially if the stress time is small. Therefore, NBTI degradation is weakly pronounced at small  $F_{ox}$ , when  $-V_D < V_{BG} - V_D < 0$ , i.e., the applied voltage is not enough to shift the Fermi level below the intrinsic level [Fig. 2(a), inset].

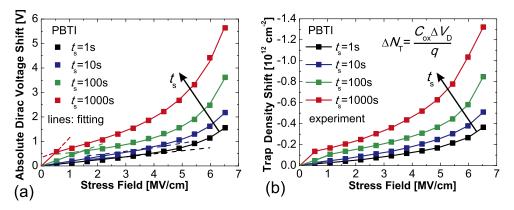

Contrary to NBTI, PBTI is independent of the intrinsic hole level position, since any stress with  $V_{\rm BG} - V_{\rm D} > 0$  introduces extrinsic electrons and shifts the Fermi level into the conduction band. That is why some PBTI degradation is clearly visible even after a stress with  $t_{\rm s} = 1\,{\rm s}$  and  $F_{\rm ox} < 1\,{\rm MV/cm}$  [Fig. 3(a)]. However, the dependence of the

Fig. 3. (Color online) Stress field dependence of the  $\Delta V_D$  (a) and  $\Delta N_T$  (b) after PBTI stresses with different  $t_s$ .  $\Delta N_T < 0$  means electron trapping.

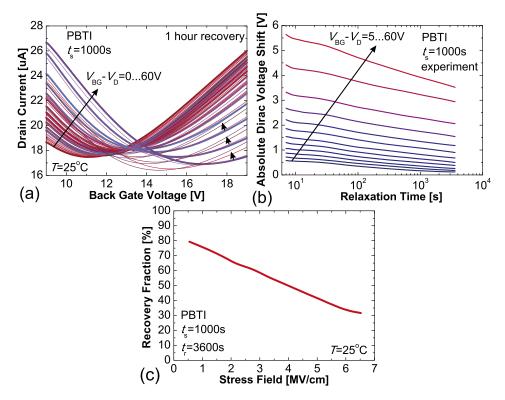

Fig. 4. (Color online) (a) Time evolution of the back gate transfer characteristics after subsequent PBTI stress/recovery rounds with increasing  $V_{\rm BG} - V_{\rm D}$ . (b) The corresponding  $\Delta V_{\rm D}(t_{\rm r})$  recovery traces. (c) The recovery fraction measured 1 h after the stress decreases versus the stress oxide field.

magnitude of the PBTI shifts on the stress oxide field is strongly correlated with the stress time. For example, if  $t_{\rm s}$  is small, the PBTI shift moderately increases in a linear manner up to quite large  $F_{\rm ox}$ . Conversely, in the case of long stresses a strong linear dependence of  $\Delta V_{\rm D}$  on  $F_{\rm ox}$  is observed only in a very narrow range of small  $F_{\rm ox}$ , being immediately substituted by a Langmuir-like behavior. Obviously, the same type of oxide field dependence is typical for the charged trap density shift  $\Delta N_{\rm T}$ , which is proportional to  $\Delta V_{\rm D}$  [Fig. 3(b)]. However, the values of  $\Delta N_{\rm T}$  observed for GFETs are  $10^{11}$ – $10^{12}$  cm<sup>-2</sup>, which is significantly larger than for Si technologies  $(10^{10}$ – $10^{11}$  cm<sup>-2</sup>).<sup>22)</sup>

Next we examine the time evolution of the back gate transfer characteristics after the BTI stress. In order to do this, we fix a comparably large  $t_s = 1000 \,\mathrm{s}$  and monitor the recovery during 1 h after the end of stress with a certain  $V_{\mathrm{BG}} - V_{\mathrm{D}}$ . This allows to express the recovery dynamics in

terms of the traces  $\Delta V_{\rm D}$  versus the relaxation time  $t_{\rm r}$ . The results obtained for PBTI are shown in Fig. 4. Clearly, the back gate BTI degradation in GFETs is recoverable, similarly to its counterpart observed on the high-k top gate  $^{17,18}$ ) and also to Si technologies. Remarkably, after the stress with smaller oxide field the recovery is faster, while the fraction of recovered degradation is larger [Fig. 4(c)]. The latter observation is also similar to Si technologies. At the same time, the distances between the recovery traces increase versus  $V_{\rm BG} - V_{\rm D}$ , following the Langmuir-like dependence which is typical for PBTI with  $t_{\rm s} = 1000$  s [cf. Fig. 3(a)].

### 5. Comparison with top gate BTI

Finally, we measured the oxide field dependences of the Dirac point voltage shift after the PBTI stress applied on the high-k top gate. The results for PBTI degradation obtained on the SiO<sub>2</sub> back gate and Al<sub>2</sub>O<sub>3</sub> top gate of the same GFET are

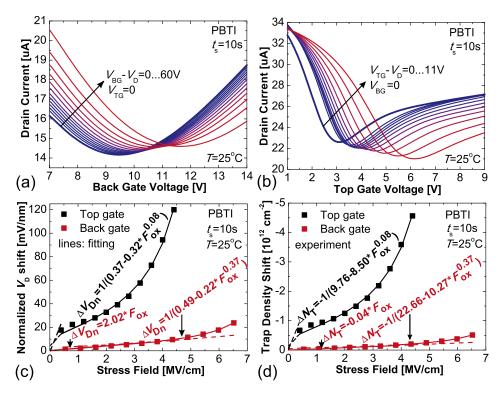

Fig. 5. (Color online) Evolution of the back gate (a) and top gate (b) transfer characteristics after the subsequent PBTI stresses with increasing oxide field. Comparison of the resulting  $\Delta V_{Dn}$  (c) and  $\Delta N_T$  (d).

compared in Fig. 5. One can see that the direction of the Dirac point voltage shift is the same [Figs. 5(a) and 5(b)], which means that an electron trapping takes place independently of whether the PBTI stress is applied on the top or back gate of GFET. At the same time, the Dirac point current is shifted in opposite directions, which is most likely because the negatively charged traps situated in  $SiO_2$  and  $Al_2O_3$  interfacial layers impact the carrier mobility in a different manner.

However, a significant difference in the oxide thicknesses requires us to operate with a normalized Dirac point voltage shift  $\Delta V_{\rm Dn} = \Delta V_{\rm D}/d_{\rm ox}$  (cf. Ref. 29) when making a quantitative comparison of the degradation magnitudes on the top and back gates. The  $\Delta V_{\rm Dn}(F_{\rm ox})$  dependences obtained for the two cases are shown in Fig. 5(c). Clearly, the magnitude of PBTI degradation on the top gate is considerably larger. This is similar to Si technologies, where the reliability of high-k oxides also presents an important issue. 30) At the same time, the dependence on  $F_{ox}$  in the case of top gate PBTI is purely Langmuir-like, while an abrupt linear increase is expected only close to  $F_{ox} = 0$ , to maintain zero degradation at zero oxide field. This is despite  $t_s = 10 \,\mathrm{s}$ , which leads to a significant linear region in the case of back gate PBTI. In other words, the behaviour of the top gate PBTI degradation versus  $F_{ox}$  observed using  $t_s = 10 \,\mathrm{s}$  is similar to those which has been measured on the back gate with significantly larger stress times (Fig. 3). Also, it is clear that the resulting charged trap density shift is larger for the top gate PBTI [Fig. 5(d)]. Therefore, we can conclude that the high-k top gate is considerably less stable with respect to BTI than the SiO<sub>2</sub> back gate.

### 6. Conclusions

We have performed an experimental study of BTI on the back gate of double-gated GFETs. It has been found that

there is a considerable asymmetry between NBTI and PBTI in terms of degradation magnitude and its dependence on the stress parameters. At the same time, the recovery of the back gate BTI has been shown to be similar to those previously reported for Si technologies and for the high-k top gate BTI in GFETs. Finally, the back gate BTI degradation dynamics is similar to the one observed on the high-k top gate, although the magnitude in the latter case is significantly larger. Therefore, we can conclude that the BTI stability of the SiO<sub>2</sub> back gate is better compared to the high-k top gate, which is similar to Si technologies.

### Acknowledgements

The support within the STREP projects MoRV (No. 619234) and GRADE (No. 317839), an ERC Starting Grant (InteGraDe, No. 307311), and the German Research Foundation (DFG, LE 2440/1-1 and 2-1).

- K. S. Novoselov, A. K. Geim, S. V. Morozov, D. Jiang, Y. Zhang, S. V. Dubonos, I. V. Grigorieva, and A. A. Firsov, Science 306, 666 (2004).

- 2) A. K. Geim and K. S. Novoselov, Nat. Mater. 6, 183 (2007).

- 3) V. E. Dorgan, M.-H. Bae, and E. Pop, Appl. Phys. Lett. 97, 082112 (2010).

- S. Vaziri, G. Lupina, A. Paussa, A. D. Smith, C. Henkel, G. Lippert, J. Dabrowski, W. Mehr, M. Ostling, and M. C. Lemme, Solid-State Electron. 84, 185 (2013).

- M. C. Lemme, T. J. Echtermeyer, M. Baus, and H. Kurz, IEEE Electron Device Lett. 28, 282 (2007).

- Y.-M. Lin, K. A. Jenkins, A. Valdes-Garcia, J. P. Small, D. B. Farmer, and P. Ayouris. Nano Lett. 9, 422 (2009).

- J. S. Moon, D. Curtis, M. Hu, D. Wong, C. McGuire, P. M. Campbell, G. Jernigan, J. L. Tedesco, B. VanMil, R. Myers-Ward, C. Eddy, and D. K. Gaskill, IEEE Electron Device Lett. 30, 650 (2009).

- I. Meric, C. Dean, A. Young, J. Hone, P. Kim, and K. L. Shepard, IEDM Tech. Dig., 2010, 23.2.1.

- S.-J. Han, Z. Chen, A. A. Bol, and Y. Sun, IEEE Electron Device Lett. 32, 812 (2011).

- M. Engel, M. Steiner, A. Lombardo, A. C. Ferrari, H. v. Löhneysen, P. Avouris, and R. Krupke, Nat. Commun. 3, 906 (2012).

- S. Vaziri, G. Lupina, C. Henkel, A. D. Smith, M. Ostling, J. Dabrowski, G. Lippert, W. Mehr, and M. C. Lemme, Nano Lett. 13, 1435 (2013).

- H. Yang, J. Heo, S. Park, H. J. Song, D. H. Seo, K.-E. Byun, P. Kim, I. Yoo, H.-J. Chung, and K. Kim, Science 336, 1140 (2012).

- 13) S. A. Imam, S. Sabri, and T. Szkopek, Micro Nano Lett. 5, 37 (2010).

- B. Liu, M. Yang, C. Zhan, Y. Yang, and Y.-C. Yeo, Proc. VLSI, 2011, p. 22.

- W. J. Liu, X. W. Sun, X. A. Tran, Z. Fang, Z. R. Wang, F. Wang, L. Wu, J. F. Zhang, J. Wei, H. L. Zhu, and H. Y. Yu, IEEE Trans. Device Mater. Reliab. 12, 478 (2012).

- 16) W. J. Liu, X. W. Sun, Z. Fang, Z. R. Wang, X. A. Tran, F. Wang, L. Wu, G. I. Ng, J. F. Zhang, J. Wei, H. L. Zhu, and H. Y. Yu, IEEE Electron Device Lett. 33, 339 (2012).

- 17) Yu. Yu. Illarionov, A. D. Smith, S. Vaziri, M. Ostling, T. Mueller, M. C. Lemme, and T. Grasser, Proc. SNW, 2014, p. 29.

- Yu. Yu. Illarionov, A. D. Smith, S. Vaziri, M. Ostling, T. Mueller, M. C. Lemme, and T. Grasser, Appl. Phys. Lett. 105, 143507 (2014).

- Yu. Yu. Illarionov, M. Waltl, A. D. Smith, S. Vaziri, M. Ostling, M. C. Lemme, and T. Grasser, Proc. EUROSOI-ULIS, 2015, p. 81.

- 20) Yu. Yu. Illarionov, M. Waltl, A. D. Smith, S. Vaziri, M. Ostling, T.

- Mueller, M. C. Lemme, and T. Grasser, Proc. IRPS, 2015, XT.2.1.

- 21) W. J. Liu, X. W. Sun, X. A. Tran, Z. Fang, Z. R. Wang, F. Wang, L. Wu, J. F. Zhang, J. Wei, H. L. Zhu, and H. Y. Yu, IEEE Trans. Electron Devices 60, 2682 (2013).

- 22) T. Grasser, W. Goes, and B. Kaczer, IIRW Final Report (2006) p. 5.

- 23) T. Grasser, W. Gos, V. Sverdlov, and B. Kaczer, Proc. IRPS, 2007, p. 268.

- 24) T. Grasser, B. Kaczer, Ph. Hehenberger, W. Gos, R. O'Connor, H. Reisinger, W. Gustin, and C. Schlunder, IEDM Tech. Dig., 2007, p. 801.

- 25) Ph. Hehenberger, H. Reisinger, and T. Grasser, IIRW Final Report (2010)

- D. S. Ang, Z. Q. Teo, T. J. Ho, and C. M. Ng, IEEE Trans. Device Mater. Reliab. 11, 19 (2011).

- 27) K. Rott, H. Reisinger, S. Aresu, C. Schlunder, K. Kolpin, W. Gustin, and T. Grasser, Microelectron. Reliab. 52, 1891 (2012).

- 28) R. Shangqing, Y. Hong, T. Bo, X. Hao, L. Weichun, T. Zhaoyun, X. Yefeng, X. Jing, W. Dahai, L. Junfeng, Y. Jiang, Z. Chao, C. Dapeng, Y. Tianchun, and W. Wenwu, J. Semicond. 36, 014007 (2015).

- H. Reisinger, R. P. Vollertsen, P. J. Wagner, T. Huttner, A. Martin, S. Aresu, W. Gustin, T. Grasser, and C. Schlunder, IIRW Final Report (2008) p. 1.

- G. Ribes, J. Mitard, M. Denais, S. Bruyere, F. Monsieur, C. Parthasarathy, E. Vincent, and G. Ghibaudo, IEEE Trans. Device Mater. Reliab. 5, 5 (2005).