#### **Meeting Abstracts**

ma.ecsdl.org

Abstract MA2017-02 837

# (Invited) Impact of Gate Dielectrics on the Threshold Voltage in MoS<sub>2</sub> Transistors

Theresia Knobloch<sup>a</sup>, Gerhard Rzepa<sup>a</sup>, Yury Yuryevich Illarionov<sup>a,b</sup>, Michael Waltl<sup>a</sup>, Dmitry Polyushkin<sup>c</sup>, Andreas Pospischil<sup>c</sup>, Marco Furchi<sup>c</sup>, Thomas Mueller<sup>c</sup> and Tibor Grasser<sup>d</sup>

+ Author Affiliations

#### Abstract

#### Introduction

$\mathsf{MoS}_2$  is a next-generation 2D material which is considered for applications in digital electronics [1–3]. Although enormous progress has been made in the area of  $\mathsf{MoS}_2$  FETs, the available prototypes do not yet meet the high expectations. Commonly known reliability issues like the frequently observed hysteresis in the  $\mathsf{I}_D(\mathsf{V}_G)$  characteristics [4–6] and the large drifts of the threshold voltage over time [7] prohibit stable device operation for this technology. Apart from fabrication related issues, these performance limiting issues are the most critical obstacles inhibiting industrial applications of  $\mathsf{MoS}_2$  FETs. Complementing our previous works [7–9], here we present a physical modeling approach for studying the charging and discharging of preexisting defects in the surrounding dielectrics.

#### Devices

We compare the hysteresis widths measured at the gates of  $MoS_2$  based FET devices at different sweep frequencies. Additionally, we study the drifts of the threshold voltage on these devices in a systematic way by evaluating the threshold voltage shifts observed after stressing the devices for different time spans and stress voltages. From the wide range of samples available, we choose devices using a thermal  $SiO_2$  layer as a back-gate dielectric. The  $MoS_2$  is either exposed to the ambient or covered by an amorphous  $Al_2O_3$  layer. This thin dielectric layer enables a top gate contact and is at the same time necessary to prevent any degradation of the device characteristics due to the impact of the ambient [4,8].

### **Degradation Modeling**

For simulating the transfer characteristics we use a TCAD device simulator solving the drift-diffusion equations [10]. This approach is valid for devices with large dimensions and a large number of scattering centers, even if 2D channel materials are used [11]. The impact of interface defects is considered by using the standard SRH model. The transient charging and discharging of oxide defects leading to the hysteresis and the long-term drifts of the threshold voltage are described using the four-state NMP model [12,13]. The physical defect properties determining the degradation, such as trap positions and energy levels, depend on the respective oxide and have been studied in detail for SiO<sub>2</sub> [8,14] and Al<sub>2</sub>O<sub>3</sub> [9].

#### Results

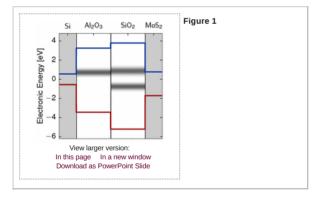

In accordance with our previous experimental work [7], we argue here that the common cause for the hysteresis in the  $I_D(V_G)$  and the observed long-term drifts are charge capture and emission events in the surrounding dielectrics. Even though several groups claim that the hysteresis is due to charge trapping at the interface [6,15,16], we argue here that interface traps can only impact the threshold voltage via a change in the sub-threshold slope. An observed hysteresis provides information about fast-switching oxide traps, while the systematic stress measurements reveal details about slow-switching oxide traps. One important quantity, necessary for understanding the size of the observed threshold voltage shifts, is the band alignment of the defect bands in the dielectrics with respect to the band edges of the semiconductors, illustrated in Fig. 1.

# Conclusions

We use a drift-diffusion based simulation methodology to describe the cause of the threshold voltage drifts observed in the  $I_D(V_G)$  characteristics of  $\mathsf{MoS}_2$  FETs, namely the charge capture and emission processes in the gate oxide traps. Thus, it is of utmost importance not only to investigate the fabrication of 2D layers, but also to focus on the quality and the defect bands of amorphous dielectrics to enable further progress in the area of FETs based on 2D materials.

## Acknowledgments

1 of 2 12/20/17, 4:12 PM

The authors gratefully acknowledge financial support through FWF grant  $\rm n^0 l2606\textsc{-}N30.$

#### References

- [1] B. Radisavljevic et al., Nature nanotechnology 6, 147 (2011).

- [2] G. Fiori et al., Nature Nanotechnology 9, 768 (2014).

- [3] S. Wachter et al., arXiv preprint 1612.00965 (2016).

- [4] D. J. Late et al., ACS Nano 6, 5635 (2012).

- [5] A.-J. Cho et al., ECS Solid State Letters 3, Q67 (2014).

- [6] Y. Park et al., Applied Physics Letters 108, 083102 (2016).

- [7] Y. Y. Illarionov et al., 2D Materials 3, 1 (2016).

- [8] Y. Y. Illarionov et al., ACS Nano 10, 9543 (2016).

- [9] Y. Y. Illarionov et al., 2D Materials 1, Under Review (2017).

- [10] Global TCAD Solutions, Minimos-NT Manual, 2015.

- [11] S. V. Suryavanshi et al., Journal of Applied Physics 120, 224503 (2016).

- [12] T. Grasser et al., IEEE Trans. Dev. Mat. Reliability 58, 3652 (2011).

- [13] T. Grasser, Microelectronics Reliability 52, 39 (2012).

- [14] G. Rzepa et al., 2016 VLSI Symposium 208 (2016).

- [15] Y. Guo et al., Applied Physics Letters 106, (2015).

- [16] K. Choi et al., Nanoscale 7, 5617 (2015).

Fig. 1: Band alignment of defect bands in Al<sub>2</sub>O<sub>3</sub> and SiO<sub>2</sub>.

© 2017 ECS - The Electrochemical Society

# **Related Article**

#### 2D and Beyond Materials and Devices:

Theresia Knobloch, Gerhard Rzepa, Yury Yuryevich Illarionov, Michael Waltl, Dmitry Polyushkin, Andreas Pospischil, Marco Furchi, Thomas Mueller, and Tibor Grasser

(Invited) Impact of Gate Dielectrics on the Threshold Voltage in  ${\rm MoS}_2$  Transistors

ECS Trans. 2017 80(1): 203-217; doi:10.1149/08001.0203ecst

Abstract Full Text (PDF)

2 of 2 12/20/17, 4:12 PM