# Efficient Physical Defect Model Applied to PBTI in High- $\kappa$ Stacks

G. Rzepa, \*\* J. Franco, \*A. Subirats, \*M. Jech, \*A. Chasin, \*A. Grill, \*M. Waltl, \*T. Knobloch, \*B. Stampfer, \*T. Chiarella, \*N. Horiguchi, \*L.Å. Ragnarsson, \*D. Linten, \*B. Kaczer, \*and T. Grasser

<sup>⋄</sup>Institute for Microelectronics, TU Wien, Austria •imec, Leuven, Belgium \*visiting imec

Abstract-Instabilities in MOS-based devices with various substrates ranging from Si, SiGe, IIIV to 2D channel materials, can be explained by defect levels in the dielectrics and nonradiative multi-phonon (NMP) barriers. However, recent results obtained on single defects have demonstrated that they can show a highly complex behaviour since they can transform between various states. As a consequence, detailed physical models are complicated and computationally expensive. As will be shown here, as long as only lifetime predictions for an ensemble of defects is needed, considerable simplifications are possible. We present and validate an oxide defect model that captures the essence of full physical models while reducing the complexity substantially. We apply this model to investigate the improvement in positive bias temperature instabilities due to a reliability anneal. Furthermore, we corroborate the simulated defect bands with prior defect-centric studies and perform lifetime projections.

*Index Terms*— bias temperature instabilities, high-k dielectric materials, semiconductor device reliability

#### I. Introduction

Over the last decades, a number of BTI models have been developed [1]. While simple power-law descriptions give reasonable results for the evolution of the threshold voltage shift  $\Delta V_{\rm th}$  as a function of stress time  $t_{\rm s}$ , they do not include recovery and give overly pessimistic life-time estimations because they do not cover the experimentally observed saturation of  $\Delta V_{\text{th}}$  at long  $t_{\text{s}}$  [2]. Several physics based models give more accurate predictions as discussed in Section II, in particular, models which are based on pre-existing defects with distributed capture and emission time constants give consistent results [3,4]. NMP theory [5–7] provides the most accurate physical description of these constants and various phenomena related to oxide defects across multiple technologies [8–10]. In particular, the four-state NMP model [11] has been successfully applied to model BTI recovery for negative (NBTI) and positive (PBTI) gate voltages  $V_G$  [12]. This model also gives a consistent explanation for random telegraph noise (RTN) [13] and stress-induced leakage currents (SILC) [14, 15]. Very recent modeling attempts led to an extension of this model to describe the hydrogen release mechanism [16].

While these models are in line with density functional theory studies and allow for detailed physical insights [17], they typically require time-consuming TCAD simulations with numerous physical model parameters. Capture/emission time (CET) map based models were proposed as efficient alternatives with a limited number of parameters to provide a physical approximation for the full four-state NMP model [18, 19]. However, these models consider the  $V_{\rm G}$  dependence only empirically. Another modeling approach which enables fast AC circuit simulation was proposed recently [20]. This model

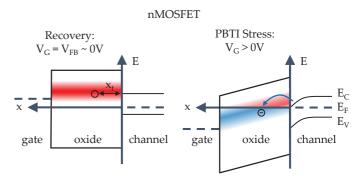

**Fig. 1:** Schematic band diagrams for recovery (**left**) and stress conditions (**right**) depicting the charging of oxide defects. In a simple picture with oxide defects interacting with carriers from the channel, all acceptor-like defects above the Fermi level of the channel will be neutral (red) and those below the Fermi level will be negatively charged (blue) for equilibrium conditions. The transient degradation depends on the interface distance  $x_T$  of the individual defect as  $x_T$  affects the tunneling process and the energy barrier of the transition

builds on top of bias and temperature dependent time constants of defects and therefore depends on input from four-state NMP TCAD simulations.

Here we present an effective two-state NMP model to bridge the gap between models which are accurate but complex and models which are compact but miss important aspects of charge trapping. While the abstraction from the full four-state model inevitably implies a slight loss of physicality, which affects the characteristics of individual defects (temporary RTN, switching defects, multi-state frequency dependence [21]), it still provides accurate results for  $\Delta V_{\rm th}$ , is efficient and convenient to use and, has a very limited number of physical parameters.

Due to its physical foundation, this two-state NMP model describes charging of oxide defects with "90% accuracy at 10% complexity" and is applicable across technologies and stress polarities. In this work the foundations of this claim are established. Degradation mechanisms which act beyond charging of oxide defects can be easily modeled additionally if they have a significant contribution to the overall degradation. For example this may be necessary at elevated source-drain voltages where hot-carrier degradation (HCD) is observed together with BTI.

## II. PREVIOUS PBTI STUDIES

Zafar et al. proposed a PBTI model based on oxide defects with distributed capture time constants [23]. This model was later extended to account for de-trapping [24]. Saturation at long  $t_s$  is predicted, however, bias and temperature is only considered with empirical parameters. Shanware et al. proposed a similar model with a log- $t_s$  dependent degrada-

tion and again empirical parameters to account for bias and temperature dependence [25]. Kerber *et al.* concluded in an early study that PBTI is due to *charging of pre-existing defects* and suggested a defect band with tunneling limited charge transfer [26]. Torii *et al.* investigated the microscopic nature of defects contributing to PBTI and proposed recoverable oxide vacancies in  $HfO_2$  as possible candidates. They identified only a marginal increase of  $D_{it}$  accompanied with PBTI [27].

Ribes *et al.* assessed different degradation mechanisms and suggested bulk oxide defects which are governed by SRH and tunneling mechanisms to be responsible for PBTI in high- $\kappa$  devices [28]. Later, Mitard *et al.* presented a detail experimental study where they identified three different regimes of PBTI degradation. In addition to recoverable defects, they suggested defect generation for long term stress [29]. Zhao *et al.* suggested that "NBTI and PBTI share similar microscopic

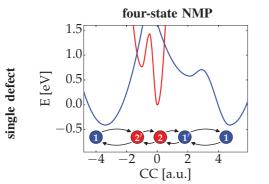

Fig. 2: CC-diagrams of exemplary single defects with neutral (blue) and positive states (red). The four-state NMP model (left) accounts for two NMP transistions with charge exchange (state  $1 \leftrightarrow 2'$  and  $1' \leftrightarrow 2$ ) and structural relaxation in each charge state (state  $1 \leftrightarrow 1'$  and  $2 \leftrightarrow 2'$ ). The two-state model (right) only consideres one effective NMP transition (state  $1 \leftrightarrow 2$ ) with the energy barrier  $\varepsilon_{12}$  for hole capture and  $\varepsilon_{21}$  for hole emission.

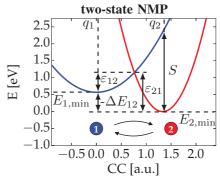

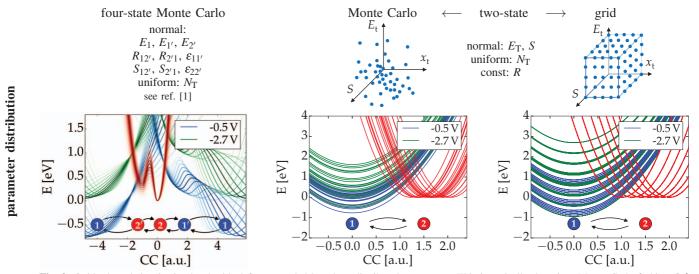

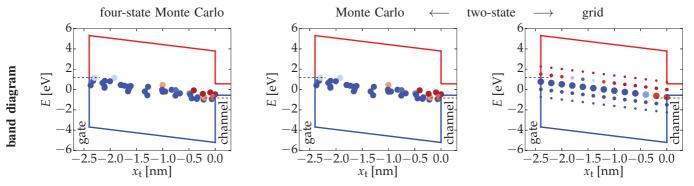

Fig. 3: Oxide degradation is simulated with defects sampled based on distributed parameters. This is typically done in a Monte Carlo fashion (left for the four-state [22] and middle for the effective two-state model). This enables variability studies, however, it is not efficient for simulations of the mean degradation. Due to the limited number of parameters, the two-state model allows for fast and deterministic simulation where the defects are sampled on a 3D grid (right). Top: The parameters of four-state and two-state defects with schematic distributions. Bottom: Exemplary CC-diagrams of ensembles of defects for two gate voltages.

**Fig. 4:** The charge state of the defects is evaluated based on the device electrostatics and the individual parameters of the discrete defects. Shown are exemplary band diagrams of an  $SiO_2$  pMOS for the three simulation modes. The defects are depicted according to their interface distance and defect level while the color indicates their charge for equilibrium conditions. Note that the band diagrams for four-state MC (**left**) and two-state MC (**middle**) are identical as the  $E_T$  and  $x_T$  of four-state and two-state defects are the same. However, there can be deviations of the transient occupancy for these two modes. For two-state defects sampled on a grid (**right**), the samples points are weighted as indicated by their size.

trapping/de-trapping mechanism" [3] and successfully applied the framework of microscopic defects with individual capture and emission times to model PBTI. Vandelli *et al.* went a step further and calculated capture and emission times from relaxation energies, and extended the framework for trap to trap tunneling [4]. On the contrary, with respect to SILC it has been suggested that defect generation is the root cause (instead of defect activation) [30] while others have demonstrated the recoverable nature of SILC and PBTI related degradation [31, 32] indicating a defect activation mechanism in the framework of NMP theory [33].

#### III. MODELING

The spatial location in the oxide and the defect level  $E_{\rm T}$  are fundamental properties of oxide defects. While  $E_{\rm T}$  determines the charge of defects for equilibrium conditions, the transient charge capture and emission events are more involved. Tunneling processes have to be considered and additional energy barriers govern the capture  $(\tau_{\rm c})$  and emission time constants  $(\tau_{\rm e})$  as described in the framework of NMP theory [5–7]. A schematic charge capture process is depicted in **Fig. 1**.

In the four-state model,  $\tau_c$  and  $\tau_e$  are determined by two NMP transitions and two pure thermal transitions between the stable (1, 2) and metastable states (1', 2').

In the two-state model we only considering one effective NMP transition between two stable states (1, 2). The potential energy surface for this transition is approximated with a quantum harmonic oscillator along the transition path [1]. The transition barriers can be depicted in configuration coordinate (CC) diagrams (see **Fig. 2**). With the parabolic potentials

$$E_1 = E_{1,\min} + c_1 (q - q_1)^2, \tag{1}$$

$$E_2 = E_{2 \min} + c_2 (q - q_2)^2, \tag{2}$$

the energy barriers  $\varepsilon_{12}$  and  $\varepsilon_{21}$  depend on the ratio of the curvatures  $R^2=c_1/c_2$ , the exitation energy for optical transitions S, and on the bias dependent energy difference  $\Delta E_{12}=E_{2,\min}\left(V_{\rm G}\right)-E_{1,\min}\left(V_{\rm G}\right)$ .

Since the distribution of R was found to be narrow, we approximated R to be constant to make the two-state model more concise. Furthermore, we assume the spatial distribution of defects within a defect band to be uniform with the defect density  $N_{\rm T}$ , while the distribution of their  $E_{\rm T}$  is approximated to be normal. This leaves three distributed parameters for the two-state model:  $E_{\rm T}$ ,  $N_{\rm T}$ , and  $S_{\rm c}$ . In addition to the sampling of a set of defects from these distributions in a Monte Carlo (MC) fashion, the limited number of distributed parameters of the two-state model enables deterministic simulations with representative defects placed on a grid in the space spanned by the three distributed parameters  $E_{\rm T}$ ,  $S_{\rm t}$ , and the distance from the channel interface  $x_{\rm T}$ , where the latter is a consequence of the uniformly distributed  $N_{\rm T}$  (**Fig. 3**). This either gives devices with discrete defects which enables studies of variability (MC) or the mean values for the given technology (grid). The corresponding band diagrams are shown in Fig. 4.

The effect of oxide defects on the device characteristics can be quantified by the shift of the threshold voltage  $\Delta V_{\text{th}}$ . In a simple approximation, the oxide charge is assumed to be

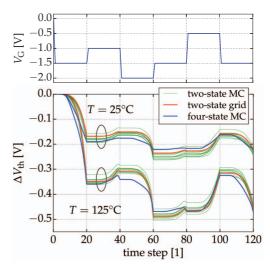

**Fig. 5:** While the abstraction of four states to two states can affect the characteristics of single defects, the differences appear to average out for multiple defects. This is verified by simulating a multi-level stress pattern (**top**). Each stress phase has  $t_s = 100$  s, sampled on a log scale (20 time steps = 100 s). The simulation results for this stress pattern with the full four-state NMP TCAD model show good agreement with the two-state model (MC and grid) for two different temperatures (**bottom**). Note that the deviations do not accumulate over time. The two-state MC was calculated with 10 different samples, each with 20k defects.

spread over a charge sheet with the interface distance  $x_T$  [36]. For single layer oxides with thickness  $t_{ox}$ , width W, and length L,  $\Delta V_{th}$  evaluates to

$$\Delta V_{\rm th} = -q_{\rm t} \frac{t_{\rm ox} \left(1 - \frac{x_{\rm t}}{t_{\rm ox}}\right)}{\varepsilon_0 \varepsilon_{\rm r} W L},\tag{3}$$

where the charge of the oxide defect  $q_t$  is the product of the elementary charge and the occupancy of the positive charge state. The occupancy  $p_1$  of the neutral state 1 and  $p_2$  of the positive state 2 can be calculated based on  $p_1 + p_2 = 1$  and the Master equation

$$\frac{\mathrm{d}p_1(t)}{\mathrm{d}t} = -p_1 \sum_{i=1}^{N} k_{12,i} + p_2 \sum_{i=1}^{N} k_{21,i}$$

(4)

with the rates  $k_{12,i}$  from state 1 to state 2 and the sum over i indicating the various charge carrier reservoirs (with N being the number of reservoirs) which may interact with the oxide defect. For the example of the reservoir being electrons at the conduction band edge of the channel, the rate is [1]

$$k_{21} = n v_{\text{th n}} \sigma_{0 n} \vartheta_{n} e^{-\beta \varepsilon_{21}} \tag{5}$$

where n is the concentration of electrons in the channel,  $v_{\rm th,n}$  their thermal velocity,  $\sigma_{0,n}$  their capture cross section,  $\vartheta_n$  their tunneling coefficient,  $\beta=1/k_{\rm B}T$ , and  $\varepsilon_{21}=\varepsilon_{12}-\Delta E_{12}$  the energy barrier from state 2 to state 1. Assuming parabolic potential energy surfaces,  $\varepsilon_{12}$  can be approximated by [1]

$$\varepsilon_{12} = \frac{S}{(R^2 - 1)^2} \left( 1 - R\sqrt{\frac{S + \Delta E_{12}(R^2 - 1)}{S}} \right)^2, \tag{6}$$

with R, S, and  $\Delta E_{12}$  as introduced above (see also Fig. 2). Note that  $\Delta E_{12}$  is a function of  $E_{\rm T}$ , of the energy of the carrier at the reservoir, and of the device electrostatics, and therefore of the gate voltage  $V_{\rm G}$ .

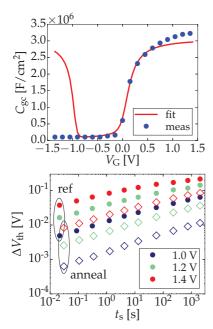

**Fig. 6:** For the extraction of the defect bands, the two-state model requires the surface potential which can be calculated from CV curves (**top**) using the CVC Hauser tool [34] and BTI measurements. The improvement in PBTI due to the anneal is apparent in the eMSM experiments for different  $V_{\rm OV}$  at  $T=125^{\circ}{\rm C}$  (**bottom**).

#### IV. MODEL VERIFICATION

In order to verify the validity of the abstraction of four states to two states, an exemplary NBTI multi-state stress pattern was simulated on a 2.4 nm thick  $SiO_2$  device (**Fig. 5**, **top**). For the full four-state TCAD simulation, the previously extracted parameters for  $SiO_2$  were used [12]. For the two-state model the *same*  $E_T$  and  $N_T$  were used while R and S

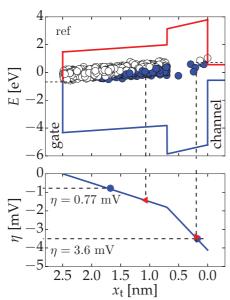

**Fig. 8:** The extracted defects of the reference device depicted in the band diagram (**top**) and  $\eta$  estimated with the charge sheet approximation (**bottom**). The centroid of the charges (vertical dashed lines) is compared to the two distinct contributions obtained by defect-centric studies [35] (horizontal dashed lines). The deviation for charges in the HK is probably due to differences in the processing and the  $t_s$  dependence of the extraction. Note that the gate area was scaled to match  $\eta$  of the IL which allows for a comparison of  $\eta$  of the HK.

TABLE I: Defect bands extracted with the two-state model.

|                                  |             | HfO <sub>2</sub>     |        | SiO <sub>2</sub>     |        |

|----------------------------------|-------------|----------------------|--------|----------------------|--------|

|                                  |             | ref                  | anneal | ref                  | anneal |

| $\langle E_{\mathrm{T}} \rangle$ | [eV]        | 0.99                 | 1.26   | 0.69                 | 0.85   |

| $\sigma_{\rm E_T}$ $N_{ m T}$    | [eV]        | 0.18                 |        | 0.2                  |        |

| $N_{ m T}$                       | $[cm^{-3}]$ | $5.0 \times 10^{20}$ |        | $8.7 \times 10^{18}$ |        |

| $\langle S \rangle$              | [eV]        | 1.39                 |        | 2.7                  |        |

| $\sigma_{\rm S}$                 | [eV]        | 0.32                 |        | 0.8                  |        |

| R                                | [1]         | 0.4                  |        | 0.5                  |        |

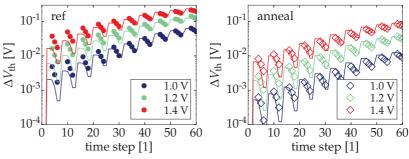

**Fig. 7:** Fast optimization of the six physical model parameters in the "grid" mode of the twostate model gives a good agreement for the reference device (**left**) and the device with the reliability anneal (**right**). Shown are measurements (symbols) and simulation results (lines) for a full eMSM signal with stress and recovery phases. If the anneal had mainly an affect on  $N_{\rm ot}$ , the reference curve would be shifted in the log plots, hence, the bias dependence would be different.

were optimized to obtain a match with the results from the four-state model (**Fig. 5, bottom**). The obtained R and S have a physical meaning, but represent effective values which abstract the physics from all four states. However,  $E_{\rm T}$  and  $N_{\rm T}$  retain their full physical meaning which enables the extraction of defect bands.

## V. APPLICATION TO HIGH- $\kappa$ STACKS

We employ the new effective two-state model to extract the defect bands responsible for PBTI in high- $\kappa$  gate stacks (note that this model describes the behavior of oxide defects, and hence it is not limited to PBTI studies only). Although PBTI is *not* the most severe reliability issue for current Si FinFET logic technology [37], the study of high- $\kappa$  defects is of

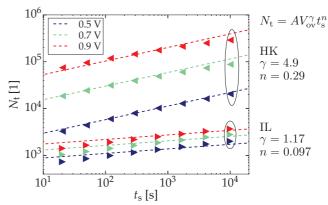

**Fig. 9:** The number of trapped electrons  $(N_t)$  in the HK and in the IL of the simulated reference device (symbols) compared to the time and voltage acceleration exponents as obtained by defect centric studies [35]. Note that the magnitude A, hence  $N_T$ , was scaled to fit the simulation results since only the power-law factors for  $V_{\text{ov}}(\gamma)$  and  $t_{\text{s}}(n)$  were given in the defect-centric studies.

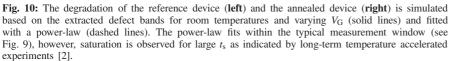

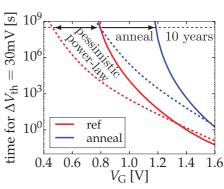

**Fig. 11:** The two-state simulations show an improvement of  $V_{\rm G}$  for 10 years life time due to the reliability anneal from  $V_{\rm G}=0.8$  to 1.2 V (solid lines), The power-law extrapolation is more pessimistic (dashed lines).

relevance for many novel technologies which are frontrunner candidates for future CMOS nodes, e.g., Ge/IIIV high-mobility channel devices fabricated in low thermal budget processes [38], stacked device technology [39,40], and 2D channel transistors [10]. Moreover, the study of high- $\kappa$  defects is relevant for DRAM periphery transistors which still employ thick oxides and high temperature anneals for gate leakage suppression and work function engineering [41]. The well understood FinFET technology used here as a *study case* allows for a broad verification of the obtained results which is necessary to validate the presented approach.

The experiments were conducted on nMOS devices of a high- $\kappa$  FinFET technology with a 1nm (EOT) gate stack (HfO<sub>2</sub> (HK) with a SiO<sub>2</sub> interface layer (IL)), targeting the 14 nm node. The effect of thermal treatment on defect properties is investigated by comparing a high- $\kappa$  replacement metal gate (RMG) with a post metalization anneal (PMA,  $T=900^{\circ}$ C for few seconds) to a reference gate stack without a PMA.

The two-state model was implemented in a python script which calculates the quantities for the physical defect model based on the surface potential. The surface potential in turn was obtained from capacitance-voltage (CV) measurements using the CVC Hauser tool [34] (Fig. 6, top for nFinFET split-CV showing the gate-channel capacitance  $C_{\rm gc}$ ). PBTI was characterized for a reference stack and for an annealed stack using the extended measure-stress-measure (eMSM) technique [42] covering stress times from 10 ms up to 2 ks and overdrive voltages  $V_{\rm ov} = V_{\rm G} - V_{\rm th}$  between 1.0 and 1.4 V (**Fig.** 6, bottom). Based on these input data, the two-state model parameters were fitted for the annealed device. The dominant effect of the anneal on the defect properties was found to be a shift of  $E_{\rm T}$  and as such  $\langle E_{\rm T} \rangle$  was optimized for the reference device, while all other parameters were kept at the values obtained from the annealed device.

The two-state model captures  $\Delta V_{\text{th}}$  during the *stress and recovery* phases (10 s recovery after each stress phase) for the reference and the annealed gate stack (**Fig. 7**). A dominant electron defect band in the HK was extract which is in line with recent *ab initio* studies [43]. Additionally, an electron defect band in the IL with a rather low  $N_{\text{T}}$  was extracted (see **Table I**). The latter should not be confused with the hole defect band which is commonly observed in SiO<sub>2</sub> for NBTI with a

much higher  $N_T$  at lower  $\langle E_T \rangle$ . Evidence for the extracted *electron band* in SiO<sub>2</sub> comes from PBTI experiments [44] and RTN studies [45]. Furthermore, its presence is confirmed by defect-centric studies [35]. A qualitative comparison of the simulated mean step heights  $\eta$  to results from these defect centric studies confirms the two distinct defect contributions (**Fig. 8**).

In addition, also the  $V_{\rm ov}$  and  $t_{\rm s}$  dependence of the *individual* contribution from the HK and the IL is compared to values obtained from the defect-centric studies (**Fig. 9**). The good agreement with these experimental data confirms the validity of the model and the extracted parameters.

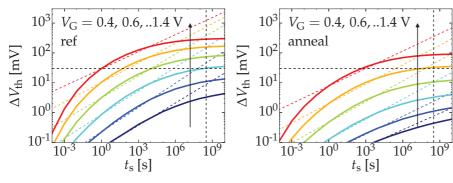

The two-state model allows for fast simulations of BTI for arbitrary stress signals and temperatures based on the extracted defect bands. The extrapolation of  $\Delta V_{\rm th}$  for long  $t_{\rm s}$  and various  $V_{\rm G}$  at room temperature is shown in **Fig. 10** (single-core simulation time on a typical workstation is below 2 seconds for a full stress trace). While the power-law gives good agreement for the time window of typical experiments (Fig. 9), there is a clear deviation from the power-law for longer  $t_{\rm s}$  (Fig. 10) which leads to overly pessimistic life time estimations of power-law extrapolations. Finally, we calculate the  $V_{\rm G}$  dependent life time and find an improvement due to the reliability anneal in the maximum operating voltage for 10 years of 0.4 V (**Fig. 11**).

### VI. CONCLUSIONS

We have introduced a two-state NMP model which is based on physical oxide defects and have verified its validity with TCAD simulations and experiments. The new model retains the main features of the four-state NMP model, and in particular the important defect properties  $E_{\rm T}$  and  $N_{\rm T}$  are maintained. This allows for an efficient extraction of defect properties and a reliable projection for various voltages, temperatures, and technologies. The application to high- $\kappa$  stacks has revealed the properties of the two electron defect bands which contribute to PBTI. Finally, we have found that the anneal of this gate stack improves life time because of a shift of  $E_{\rm T}$  towards the conduction band edges and compared the life time extrapolation to the more pessimistic power-law extrapolations.

#### ACKNOWLEDGMENTS

The research leading to these results has received funding from the Austrian Science Fund (FWF) project n°26382-N30, the European Community's FP7 project n°619234 (MoRV), as well as the Intel Sponsored Research Project n°2013111914. GTS (Global TCAD Solutions) is acknowledged for support.

#### REFERENCES

- [1] T. Grasser, ed., Bias Temperature Instability for Devices and Circuits. Springer, New York, 2014.

- [2] G. Pobegen and T. Grasser, "On the Distribution of NBTI Time Constants on a Long, Temperature-Accelerated Time Scale," *IEEE Trans. Electron Devices*, vol. 60, no. 7, pp. 2148–2155, 2013.

[3] K. Zhao, J. Stathis, B. Linder, E. Cartier, and A. Kerber, "PBTI

- [3] K. Zhao, J. Stathis, B. Linder, E. Cartier, and A. Kerber, "PBTI Under Dynamic Stress: From a Single Defect Point of View," in *Proc. Intl. Rel. Phys. Symp.* (IRPS), pp. 372–380, Apr. 2011.

- [4] L. Vandelli, L. Larcher, D. Veksler, et al., "A Charge-Trapping Model for the Fast Component of Positive Bias Temperature Instability (PBTI) in High-κ Gate-Stacks," *IEEE Trans.Electron Devices*, vol. 61, no. 7, pp. 2287–2293, 2014.

- [5] K. Huang and A. Rhys, "Theory of Light Absorption and Non-Radiative Transitions in F-Centres," *Proc.R.Soc.A*, vol. 204, pp. 406–423, 1950.

- [6] D. Lang and C. Henry, "Nonradiative Recombination at Deep Levels in GaAs and GaP by Lattice-Relaxation Multiphonon Emission," *Physical Review Letters*, vol. 35, no. 22, pp. 1525–1528, 1975.

- [7] M. Kirton and M. Uren, "Noise in Solid-State Microstructures: A New Perspective on Individual Defects, Interface States and Low-Frequency (1/f) Noise," Adv. Phys., vol. 38, no. 4, pp. 367–486, 1989.

[8] J. Franco, B. Kaczer, J. Mitard, et al., "NBTI Reliability of SiGe and

- [8] J. Franco, B. Kaczer, J. Mitard, et al., "NBTI Reliability of SiGe and Ge Channel pMOSFETs With SiO<sub>2</sub> and HfO<sub>2</sub> Dielectric Stack," *IEEE Trans. Dev. Mat. Rel.*, vol. 13, no. 4, pp. 497–506, 2013.

- [9] A. Grill, G. Rzepa, P. Lagger, et al., "Charge Feedback Mechanisms at Forward Threshold Voltage Stress in GaN / AlGaN HEMTs," Proc. Intl. Integrated Reliability Workshop, 2015.

- [10] Y. Y. Illarionov, G. Rzepa, M. Waltl, et al., "The Role of Charge Trapping in MoS<sub>2</sub> / SiO<sub>2</sub> and MoS<sub>2</sub> / hBN Field-Effect Transistors," 2D Materials, vol. 3, no. 3, pp. 1–11, 2016.

- [11] T. Grasser, "Stochastic Charge Trapping in Oxides: From Random Telegraph Noise to Bias Temperature Instabilities," *Microelectronics Reliability*, vol. 52, pp. 39–70, 2012.

- [12] G. Rzepa, M. Waltl, W. Goes, et al., "Complete Extraction of Defect Bands Responsible for Instabilities in n and pFinFETs," in IEEE Symposium on VLSI Technology Digest of Technical Papers, pp. 208– 209, 2016.

- [13] T. Grasser, K. Rott, H. Reisinger, et al., "A Unified Perspective of RTN and BTI," in Proc. Intl.Rel.Phys.Symp. (IRPS), pp. 4A.5.1–4A.5.7, June 2014.

- [14] W. Goes and T. Grasser, "Charging and Discharging of Oxide Defects in Reliability Issues," in *Proc. Intl.Integrated Reliability Workshop*, pp. 27– 32, 2007.

- [15] W. Goes, M. Waltl, Y. Wimmer, G. Rzepa, and T. Grasser, "Advanced Modeling of Charge Trapping: RTN, 1/f noise, SILC, and BTI," in *Proc. Simulation of Semiconductor Processes and Devices*, pp. 77–80, 2014.

- [16] T. Grasser, M. Waltl, Y. Wimmer, et al., "Gate-Sided Hydrogen Release as the Origin of Permanent NBTI Degradation: From Single Defects to Lifetimes," in Proc. Intl. Electron Devices Meeting (IEDM), pp. 401–404, Dec. 2015.

- [17] T. Grasser, W. Goes, Y. Wimmer, et al., "On the Microscopic Structure of Hole Traps in pMOSFETs," in *Proc. Intl. Electron Devices Meeting (IEDM)*, Dec. 2014.

- [18] T. Grasser, P.-J. Wagner, H. Reisinger, et al., "Analytic Modeling of the Bias Temperature Instability Using Capture/Emission Time Maps," in Proc. Intl. Electron Devices Meeting (IEDM), pp. 27.4.1–27.4.4, Dec. 2011.

- [19] R. Eilers, M. Metzdorf, D. Helms, and W. Nebel, "Efficient NBTI Modeling Technique Considering Recvoery Effects," in *IEEE Int. Symposium on Low Power Electronics and Design*, Aug. 2014.

- [20] K.-U. Giering, C. Sohrmann, G. Rzepa, et al., "NBTI Modeling in Analog Circuits and its Application to Long-Term Aging Simulations," in Proc. Intl.Integrated Reliability Workshop, pp. 29–34, 2014.

- [21] T. Grasser, H. Reisinger, K. Rott, M. Toledano-Luque, and B. Kaczer, "On the Microscopic Origin of the Frequency Dependence of Hole Trapping in pMOSFETs," in *Proc. Intl. Electron Devices Meeting (IEDM)*, pp. 19.6.1–19.6.4, Dec. 2012.

- [22] G. Rzepa, W. Goes, G. Rott, et al., "Physical Modeling of NBTI: From Individual Defects to Devices," in Proc. Simulation of Semiconductor Processes and Devices, pp. 81–84, 2014.

- [23] S. Zafar, A. Callegari, E. Gusev, and M. V. Fischetti, "Charge Trapping in High k Gate Dielectric Stacks," in *Proc. Intl. Electron Devices Meeting* (*IEDM*), pp. 517–520, 2002.

- [24] S. Zafar, A. Kerber, and R. Muralidhar, "Physics Based PBTI Model for Accelerated Estimation of 10 Year Lifetime," in *IEEE Symposium* on VLSI Technology Digest of Technical Papers, 2014.

- [25] A. Shanware, M. Visokay, J. J. Chambers, et al., "Characterization and Comparison of the Charge Trapping in HfSiON and HfO<sub>2</sub> Gate Dielectrics," in Proc. Intl. Electron Devices Meeting (IEDM), pp. 939– 942, 2003.

- [26] A. Kerber, E. Cartier, L. Pantisano, et al., "Origin of the Threshold Voltage Instability in SiO<sub>2</sub>/HfO<sub>2</sub> Dual Layer Gate Dielectrics," *IEEE Electron Device Lett.*, vol. 24, no. 2, pp. 87–89, 2003.

- [27] K. Torri, K. Shiraishi, S. Miyazaki, et al., "Physical model of BTI, TDDB and SILC in HfO<sub>2</sub>-based high-k gate dielectrics," in Proc. Intl. Electron Devices Meeting (IEDM), pp. 129–132, 2004.

- [28] G. Ribes, J. Mitard, M. Denais, et al., "Review on High-k Dielectrics Reliability Issues," *IEEE Trans. Dev. Mat. Rel.*, vol. 5, no. 1, pp. 5–19, 2005.

- [29] J. Mitard, X. Garros, L. Nguyen, et al., "Large-Scale Time Characterization and Analysis of PBTI In HfO<sub>2</sub>/Metal Gate Stacks," in Proc. Intl.Rel.Phys.Symp. (IRPS), no. 2, pp. 174–178, 2006.

- [30] S. Mukhopadhyay, K. Joshi, V. Chaudhary, et al., "Trap Generation in IL and HK Layers During BTI/TDDB Stress in Scaled HKMG N and P MOSFETS" in Proc. Intl. Rel. Phys. Symp. (IRPS), pp. 1–11, 2014.

- P MOSFETs," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 1–11, 2014.

[31] D. Ioannou, S. Mittl, and G. La Rosa, "Positive Bias Temperature Instability Effects in nMOSFETs with HfO<sub>2</sub>/TiN Gate Stacks," *IEEE Trans.Electron Devices*, vol. 9, no. 2, pp. 128–134, 2009.

- [32] E. Cartier and A. Kerber, "Stress-Induced Leakage Current and Defect Generation in nFETs with HfO<sub>2</sub>/TiN Gate Stacks During Positive-Bias Temperature Stress," in *Proc. Intl.Rel.Phys.Symp. (IRPS)*, pp. 486–492, 2009.

- [33] D. Veksler and G. Bersuker, "Gate Dielectric Degradation: Pre-Existing vs. Generated Defects," *J.Appl.Phys.*, vol. 115, no. 3, pp. 1–11, 2014.

- [34] J.R. Hauser, CVC version 5.0.

- [35] P. Weckx, B. Kaczer, C. Chen, et al., "Characterization of Time-Dependent Variability Using 32k Transistor Arrays in an Advanced HK/MG Technology," in Proc. Intl.Rel.Phys.Symp. (IRPS), 2015.

- [36] T. Tewksbury, Relaxation Effects in MOS Devices due to Tunnel Exchange with Near-Interface Oxide Trans. Ph.D. Thesis, MIT. 1992.

- change with Near-Interface Oxide Traps. Ph.D. Thesis, MIT, 1992.

[37] K. Lee, C. Kang, O. Yoo, et al., "PBTI-Associated High-Temperature Hot Carrier Degradation of nMOSFETs With Metal-Gate/High-k Dielectrics," IEEE Electron Device Lett., vol. 29, no. 4, pp. 389–391, 2008.

- [38] J. Franco, A. Vais, S. Sioncke, et al., "Demonstration of an InGaAs Gate Stack with Sufficient PBTI Reliability by Thermal Budget Optimization, Nitritdation, High-k Material Choice, and Interface Dipole," in IEEE Symposium on VLSI Technology Digest of Technical Papers, 2016.

- [39] A. Tsiara, X. Garros, C.-M. V. Lu, C. Fenouillet-Béranger, and G. Ghibaudo, "Impact of Low Thermal Processes on Reliability of HK/MG Stacks," J. Vac. Sci. Technol. B, vol. 114, 2017.

- [40] J. Franco, L. Witters, others, et al., "Gate Stack Thermal Stability and PBTI Reliability Challenges for 3D Sequential Integration: Demonstration of a Suitable Gate Stack for Top and Bottom Tier nMOS," in Proc. Intl.Rel.Phys.Symp. (IRPS), 2017.

- [41] R. Ritzenthaler, T. Schram, E. Bury, et al., "Low-power DRAM-compatible Replacement Gate High-k / Metal Gate Stacks," in Proc. ESSDERC, pp. 242–245, 2012.

- [42] B. Kaczer, T. Grasser, P. Roussel, *et al.*, "Ubiquitous Relaxation in BTI Stressing New Evaluation and Insights," in *Proc. Intl.Rel.Phys.Symp.* (*IRPS*), pp. 20–27, 2008.

- [43] M. Kaviani, J. Strand, V. V. Afanas'Ev, and A. L. Shluger, "Deep Electron and Hole Polarons and Bipolarons in Amorphous Oxide," *Physical Review B*, vol. 94, no. 2, pp. 1–6, 2016.

- [44] A. Kerber, K. Maitra, A. Majumdar, et al., "Characterization of Fast Relaxation During BTI Stress in Conventional and Advanced CMOS Devices With HfO<sub>2</sub>/TiN Gate Stacks," *IEEE Trans.Electron Devices*, vol. 55, no. 11, pp. 3175–3183, 2008.

- [45] T. Nagumo, K. Takeuchi, S. Yokogawa, K. Imai, and Y. Hayashi, "New Analysis Methods for Comprehensive Understanding of Random Telegraph Noise," in *Proc. Intl. Electron Devices Meeting (IEDM)*, pp. 759– 762, 2009.