# On the Subthreshold Drain Current Sweep Hysteresis of 4H-SiC nMOSFETs

Gerald Rescher, Gregor Pobegen, Thomas Aichinger and Tibor Grasser, Fellow, IEEE

Abstract—We study the subthreshold drain current hysteresis of 4H silicon carbide Si-face (0001) and a-face (1120) n-channel power MOSFETs between gate voltage sweeps from accumulation to inversion and vice versa. Depending on the direction of the gate voltage sweep, the MOSFETs show a different subthreshold drain current at the same gate voltage. The observed hysteresis between up-sweep and down-sweep can be expressed as a subthreshold voltage shift and may reach several volts. We show that the voltage shift is caused by hole capture in border traps during accumulation and is directly propotional to the charge pumping signal. The voltage shift is fully recoverable by applying a gate bias above the threshold voltage and does not impact device reliability.

Index Terms—4H-SiC, MOSFET, subthreshold hysteresis, border states, Si-face, a-face

#### I. Introduction

Silicon carbide (SiC) offers superior material properties for power metal oxide semiconductor field effect transistors (MOSFETs). Due to the larger band gap, critical field and thermal conductivity, MOSFETs based on SiC promise an operation at higher temperature, higher power density, higher frequency and higher voltage than silicon (Si) based MOSFETs. Although advanced processing techniques like post oxidation anneal (POA) in nitrogen (N) containing atmosphere have led to major improvements within the last couple of years [1]–[9], available devices still perform far below their theoretical limits [10]–[16].

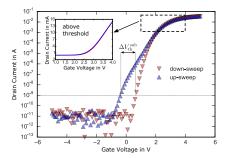

In this work, we investigate the subthreshold drain current sweep hysteresis observed for SiC power MOSFETs, which behave significantly different from silicon based power devices. It will be shown that it is an intrinsic feature of SiC-MOSFETs, that the subthreshold drain current  $I_{\rm D}$  at a certain gate voltage  $V_{\rm G}$  depends on the preceding gate voltage. We define  $V_{\rm G}$  at which  $I_{\rm D}$  reaches 1 nA as subthreshold voltage  $V_{\rm th}^{\rm sub}$ .  $V_{\rm th}^{\rm sub}$  depends on the sweep direction as indicated in Fig. 1. A  $V_{\rm G}$  sweep in the positive direction (up-sweep) starting at  $V_{\rm G}=-5\,\rm V$  results in a  $V_{\rm th}^{\rm sub}$  of  $-400\,\rm mV$ . In contrary, a  $V_{\rm G}$  sweep in the negative direction (down-sweep) starting at  $V_{\rm G}=5\,\rm V$  leads to a  $V_{\rm th}^{\rm sub}$  of  $+600\,\rm mV$ . The total hysteresis is expressed as a subthreshold voltage shift  $\Delta V_{\rm th}^{\rm sub}$  between down-sweep and up-sweep (e.g.  $\Delta V_{\rm th}^{\rm sub}=-1\,\rm V$  in Fig. 1).

## II. Experimental setup

All devices were fabricated on 4H-SiC n-doped substrates using an industrial process. The n-channel Si-face and a-face MOSFETs received a silicon dioxide  $(SiO_2)$  dielectric

deposited via chemical vapor deposition (CVD). POA was done in a nitric oxide (NO) containing atmosphere for all samples. The measurements are performed on wafer level using an Agilent B1500A parameter analyzer, an Agilent E5250A switching matrix and an Agilent 4294A impedance analyzer. Temperature sweeps are performed via an ATT Systems P40 cooling unit.

# III. GATE VOLTAGE, TIME AND TEMPERATURE DEPENDENCE

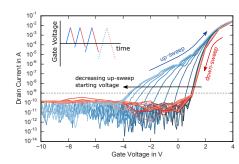

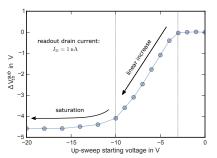

Fig. 2 shows the drain current  $I_D$  during a gate voltage  $V_{\rm G}$  sweep starting at a negative gate bias to  $V_{\rm G}=4\,{

m V}$ (up-sweep, blue) and from  $V_{\rm G}=4\,{\rm V}$  back to negative bias (down-sweep, red) at a drain voltage of  $V_D = 0.1 \,\mathrm{V}$ . The down-sweep was performed right after the up-sweep and  $V_{\rm G}$  was switched by a value of 0.1 V every 100 ms for the up-sweep and  $-1.0\,\mathrm{V}$  every  $100\,\mathrm{ms}$  for the down-sweep. While monitoring  $V_{\rm th}^{\rm sub}$  ( $I_{\rm D}(V_{\rm th}^{\rm sub})=1\,{\rm nA}$ ), we observe an increase in sweep hysteresis the more negative the up-sweep starting gate voltage. The dependence of  $\Delta V_{

m th}^{

m sub}$  on the up-sweep starting voltage is shown in Fig. 3. Nearly no  $\Delta V_{

m th}^{

m sub}$  is observed as long as the up-sweep starting voltage is higher or equal -3 V. From this point, the  $\Delta V_{

m th}^{

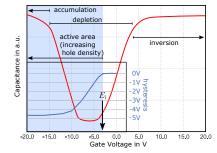

m sub}$  grows linearly with decreasing up-sweep starting voltage until it saturates for  $V_{\rm G} \leq -12\,{\rm V}$ . Decreasing the up-sweep starting voltage further does not lead to an increasing hysteresis. Furthermore, the hysteresis is independent of the high level of the gate pulse as long as it is above the threshold voltage  $V_{\mathrm{th}}.$  From the maximum  $\Delta V_{\mathrm{th}}^{\mathrm{sub}}$  of approximately  $-4.5\,\mathrm{V}$  we extract a density of trapped charges of approximately  $1.4 \times 10^{12} \, \mathrm{cm}^{-2}$  assuming all charges at the SiC-SiO<sub>2</sub> interface. The mechanism behind the hysteresis growth becomes more comprehensible by analyzing the capacitance voltage curves (Fig. 4). The hysteresis emerges as soon as the up-sweep starting voltage falls below the intrinsic Fermi level  $E_i$  allowing for hole capture in border traps. The process becomes increasingly efficient until deep accumulation is reached and the hysteresis saturates.

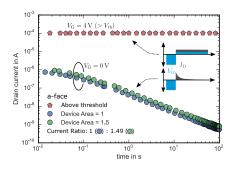

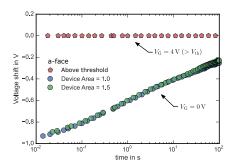

As shown in Fig. 3, a negative bias of  $V_{\rm G}=-15\,{\rm V}$  (accumulation) is sufficient to completely charge the border states and observe the maximum hysteresis. Therefore, switching directly from  $V_{\rm G}=-15\,{\rm V}$  to  $V_{\rm G}=0\,{\rm V}$  results in a measurable  $I_{\rm D}$  at  $V_{\rm G}=0\,{\rm V}$  due to the hysteresis effect. The hysteresis is only visible due to the very slow detrapping of charges for a Fermi level position around  $E_{\rm i}$ . Fig. 5 shows the time dependent decay of  $I_{\rm D}$  after the  $V_{\rm G}$  switch for two a-face devices with different active area but otherwise identical. The corresponding voltage shift at  $V_{\rm G}=0\,{\rm V}$  is shown in Fig. 6. Typically no current

10.8.1

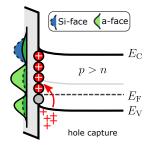

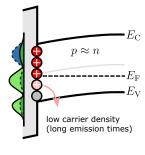

should flow at  $V_{\rm G} = 0 \, \rm V$ . However, due to the hysteresis effect caused by trapped positive charges, a drain current of approximately 1 µA is detected 10 ms after switching the bias from  $V_{\rm G} = -15 \,\rm V$  to  $V_{\rm G} = 0 \,\rm V$ .  $I_{\rm D}$  scales perfectly with device area indicating a distribution of the current over the whole device. This proofs that the hysteresis is not due to a local device leakage current caused by local electric field variations e.g. at the edges of the device. The charge density driven trapping mechanism is supported by the fact that the hysteresis becomes increasingly smaller when approaching  $V_{\rm th}$  and disappears for  $V_{\rm G} \geq V_{\rm th}$  (see red pentagons in Fig. 5 and Fig. 6), where the high electron interface density will cause very fast electron capture (hole emission) leading to a complete recovery. Even after several hundred charging and discharging repetitions, no permanent  $\Delta V_{

m th}^{

m sub}$  component is observed within the available measurement windows of 10 ms suggesting fully reversible trapping and detrapping for gate voltages above  $V_{\rm th}$ . The slow recovery in depletion is explained by the low density of electrons available at the interface but needed for electron capture. The model is sketched in Fig. 7. Temperature dependence of  $V_{

m th}^{

m sub}$  is depicted in Fig. 8. The maximum extent of the hysteresis varies between  $-4.2\,\mathrm{V}$ at 150 °C and -4.9 V at 30 °C.

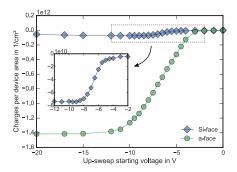

All measurements discussed above correspond to a-face (11 $\overline{2}0$ ) MOSFETs. We also investigated Si-face (0001) MOSFETs and observed the same trend although the observed  $\Delta V_{\rm th}^{\rm sub}$  is in the range of millivolts and therefore not that pronounced in the  $I_{\rm D}/V_{\rm G}$  curves. Compared to the a-face, the mobility  $\mu_0$  of the Si-face device is 3 times lower, consistent with recent studies [10]. Despite the lower channel mobility, the border trap density calculated from  $\Delta V_{\rm th}^{\rm sub}$  is about one order of magnitude lower on Si-face than on the a-face and depicted in Fig. 9. Also for Si-face MOSFETs, no permanent component in the hysteresis is observed.

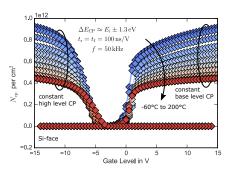

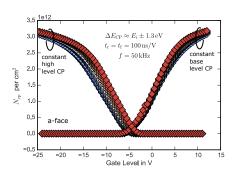

# IV. CHARGE PUMPING

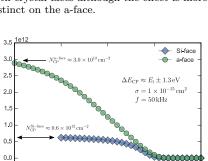

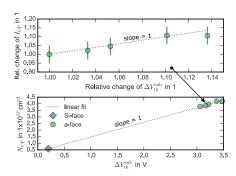

Charge pumping (CP) [17] is a suitable technique to investigate the sweep hysteresis because it is sensitive to interface and border states. The technique was recently demonstrated on 4H-SiC MOSFETs in various studies [18]–[22]. The temperature dependence of the number of pumped charges per cycle  $N_{\rm CP}$  in constant high level and constant base level CP measurements is shown in Fig. 10 for the Si-face device and Fig. 11 for the a-face device. The Si-face shows an increase in  $N_{\rm CP}$  for lower temperatures indicating higher trap densities close to the band edges of 4H-SiC, whereas the a-face device shows minor and inverted temerpature dependence indicating most of the CP signal originates from states located around midgap. Fig. 12 shows  $N_{\rm CP}$  depending on the low level of the gate pulse at 30 °C for both devices. Although the absolute number of trapped charges differ from Fig. 9. the same trend is observed. For the Si-face we extract a  $N_{\rm CP}$  of approximately  $0.6 \times 10^{12} \, {\rm cm}^{-2}$  and for the aface we extract a  $N_{\rm CP}$  of  $3 \times 10^{12} \, {\rm cm}^{-2}$  which is about 5 times higher. The linear correlation between  $\Delta V_{\mathrm{th}}^{\mathrm{sub}}$

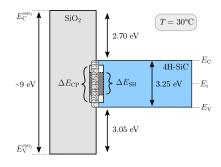

and the charge pumping current  $I_{\rm CP}$  for a-face devices is depicted in Fig. 13 (top). Devices which show an 5% increased hysteresis also show an 5% increased  $I_{\rm CP}$ . In the bottom plot of Fig. 13 the correlation of  $N_{\rm CP}$  and  $\Delta V_{\rm th}^{\rm sub}$  for both crystal planes is depicted. The result suggests the same origin for the hysteresis and increased charge pumping current on both crystal faces. The discrepancy in the total number of trapped charges extracted via the sweep hysteresis and the CP technique originates from various experimental limits of the sweep measurements, e.g extraction piont of  $\Delta V_{\rm th}^{\rm sub}$  and switching speed resulting in an narrower active energy window [23] (see Fig. 14).

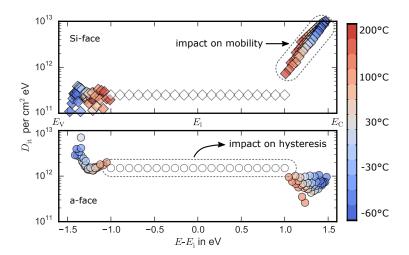

The energetic distribution of the interface/border state density  $D_{\rm it}$  was extracted using spectroscopic charge pumping [24], [25]. The result is shown in Fig. 15 for both crystal faces. For the Si-face device, we extract a  $D_{\rm it}$  of approximately  $0.25 \times 10^{12} \, {\rm cm^2 \, eV^{-1}}$  around midgap and an exponential increase close to  $E_{\rm C}$ . Even though the a-face device has a 5 times higher  $D_{\rm it}$  around midgap resulting in a more pronounced subthreshold hysteresis, the  $D_{\rm it}$  is much lower close to  $E_{\rm C}$  favoring higher mobility. A similar trend of the  $D_{\rm it}$  close to  $E_{\rm C}$  for both crystal faces was reported by Kimoto et al [26] using the  $C - \psi_{\rm s}$  method, which is based on the theoretical capacitance curve.

The atomic origin of the sweep hysteresis and the difference in hysteresis for a-face and Si-face 4H-SiC power MOSFETs might be a difference in interface structure for Si-face and a-face MOSFETs. Ion contamination as a cause of the hysteresis is excluded by the sign of the voltage shift, the speed of the capture and emission process and the temperature dependence.

# V. Conclusion

We investigated the *subthreshold* drain current hysteresis  $\Delta V_{\mathrm{th}}^{\mathrm{sub}}$  during gate voltage up and down-sweeps for 4H-SiC Si-face (0001) and a-face (11 $\overline{2}$ 0) MOSFETs, which behave significantly different from silicon based power devices. We show that  $\Delta V_{\rm th}^{\rm sub}$  scales with the charge pumping signal and disappears for gate voltages above the threshold voltage within the available measurement window of 10 ms. The difference in  $\Delta V_{

m th}^{

m sub}$  and mobility for a-face and Si-face devices is explained by the energetic distribution of the border states obtained via spectroscopic charge pumping: a-face devices show a more distinct hysteresis due to a higher border state density around midgap, but also higher mobility due to a lower border state density close to the conduction band edge of 4H-SiC.  $\Delta V_{

m th}^{

m sub}$  is fully recoverable via biasing the device near or above its  $V_{\rm th}$ . Thus, the normally off characteristics of the SiC-MOSFET is maintained in any switching case despite of the reported hysteresis effect in the subthreshold regime.

#### Acknowledgment

This work was jointly funded by the Austrian Research Promotion Agency (FFG, Project No. 854247) and the Carinthian Economic Promotion Fund (KWF, contract KWF-1521|28101|40388).

Figure 1. Sweep hysteresis between up-sweep starting at -5 V (blue) and down-sweep starting at 5 V (red). The dotted line corresponds to the readout current of the  $V_{\rm th}^{\rm sub}$  at 1 nA. The inset shows the characteristics above the threshold voltage where the hysteresis effect vanishes.

Figure 2. Increase of the sweep hysteresis depending on the starting voltage of the upsweep (blue) with inset of the measurement procedure, a gate voltage sweep with varying low level and constant high level.

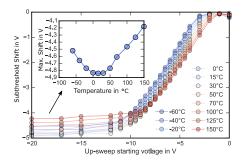

Figure 3. Subthreshold voltage shift at a drain current of  $1\,\mathrm{nA}$  as a function of the up-sweep starting voltage. The hysteresis at  $1\,\mathrm{nA}$  starts to increase linearly as soon as the up-sweep starting voltage falls below  $-3\,\mathrm{V}$  and satturates for up-sweep starting voltages below  $-12\,\mathrm{V}$ .

Figure 4. Subthreshold voltage shift (blue) and capacitance voltage curve (red). The hysteresis starts to grow, as soon as the Fermi level falls below the intrinsic Fermi level  $E_{\rm i}$  and holes are available at the interface. The hysteresis satturates as soon as the Fermi level approaches the conduction band of 4H-SiC (accumulation).

Figure 5. Recovery of  $I_{\rm D}$  at  $V_{\rm G}$  below and above the  $V_{\rm th}$  after a charging pulse at  $V_{\rm G}=-15\,{\rm V}$  on an a-face device. In the subthreshold regime at  $V_{\rm G}=0\,{\rm V}$  (circles),  $I_{\rm D}$  recovery shows a logarithmic dependence in time and scales with active area indicating a uniform distribution of the hysteresis current above the whole device area. The hysteresis effect is not visible for  $V_{\rm G}>V_{\rm th}$  (red, pentagons). The same trend is observed on Si-face devices. The measurement pattern is depicted in the inset.

Figure 6. Voltage shift according to the recovery of the drain current in Fig. 5. After switching from accumulation at  $V_{\rm G}=-15\,{\rm V}$  to depeltetion at  $V_{\rm G}=0\,{\rm V}$ , the voltage shift recovers with a logarithmic dependen in time. The voltage shift is independent of the active area (circles) and disappears for gate voltages above the threshold voltage, e.g. at  $V_{\rm G}=4\,{\rm V}$  (red, pentagons) within the measurement window of 10 ms after the bias change.

Figure 7. Schematic band diagram of the mechanism causing the sweep hysteresis. Left: hole capture in accumulation (Fermi level close to the valence band). Middle: At a Fermi level position close to midgap only a few carriers are available resulting in a slow recovery of the trapped holes. Right: recombination due to very high electron density at the interface for a Fermi level position close to the conduction band.

Figure 8. Temperature dependence of the hysteresis between  $-60\,^{\circ}\mathrm{C}$  and  $150\,^{\circ}\mathrm{C}$ . The maximum of the hysteresis stays within  $-4.2\,\mathrm{V}$  and  $-4.9\,\mathrm{V}$ .

Figure 9. Trapped charges per device area as a function of the up-sweep starting voltage for a Si-face (diamonds) and an a-face (circles) device. The same trend is observed on both crystal faces although the effect is more distinct on the a-face.

cm<sup>2</sup>

cycle

charges

-10

-5

Figure 12. Number of charges pumped during a constant high level charge pumping measurement at 30 °C for the a-face (circles, green) and Si-face (diamonds, blue) device. Although the a-face devices show better mobility, the state density is a factor of 5 higher. The increase is most likely due to defect states close to  $E_i$ .

-15

Figure 10. Charges pumped per cycle extracted from constant base level CP (right side) and constant high level CP (left side) for the Si-face device. The increase in CP current originates from trap states close to the the band edges of 4H-SiC.

Figure 13. Top: linear increase of the charge pumping current  $I_{\rm CP}$  with increasing sweep hysteresis  $\Delta V_{\rm th}^{\rm sub}$  on a-face devices. Bottom: increase in the number of pumped charges per cycle  $N_{\mathrm{CP}}$  with increasing hysteresis for the Si-face (diamonds, blue) and a-face (circles, green). Due to the linear dependency,  $\Delta V_{

m th}^{

m sub}$ most likely originates from border states at the SiC-SiO<sub>2</sub> interface.

Figure 11. Same as Fig. 10 but now for the aface device. We observe a minor and inverted temperature dependence indicating the major contribution to the charge pumping current originates from states around midgap.

Figure 14. Schematic band diagram of the SiC-SiO<sub>2</sub> system to illustrate the difference in the active energy window in the charge pumping  $\Delta E_{\rm CP}$  and sweep hysteresis  $\Delta E_{\rm SH}$ measurements. Due to the slower slew rates,  $\Delta E_{\rm SH}$  is approximately 0.8 eV narrower at 30 °C resulting in a reduced number of interface and border states contributing to the measurement signal.

Figure 15. Energetic border/interface state distribution  $D_{it}$  for the Si-face (diamonds, top) and a-face (circles, bottom). Although the a-face shows 5 times higher  $D_{it}$  around midgap resulting in a more pronounced hysteresis, the  $D_{\rm it}$  close to  $E_{\rm C}$  is about one order of magnitude lower resulting in improved mobility.

## References

- H. Li et al., APL **70**, 2028 (1997)

- G. Chung et al., EDL 22, 176 (2001)

- V. Afanas'ev et al., APL 82, 568 (2003).

- G. Chung et al., APL 76, 1713 (2000).

- S. Dhar et al., APL 84, 1498 (2004).

- P. Jamet et al., JAP 90, 5058 (2001).

- L. A. Lipkin et al., MSF, TTP (2002), Vol. 389, p. 985.

- T. Kimoto et al., JJAP 44, 1213 (2005).

- P. Jamet et al., APL 79, 323 (2001).

- H. Yano et al., EDL 20, 611 (1999).

- H. Yano et al., APL 78, 374 (2001). [11]

- [12]G. Rescher et al., ICSCRM (2015)

- 13 M. Marinella et al., APL 90, 253508 (2007).

- T. Okayama et al., SSE **52**, 164 (2008).

- [15]G. Pobegen et al., IRPS, IEEE (2015), p. 6C.

- [16]X. Shen et al., APL 98, 063507 (2011)

- J. S. Brugler et al., TED 16, 297 (1969) [17]

- A. Salinaro et al., TED 62, 155 (2015).

- D. Okamoto et al., TED 55, 2013 (2008) [19]

- D. Habersat et al., MSF, TTP (2009), Vol. 600, p. 743.

- C. Scozzie et al., MSF, TTP (1998), Vol. 264, p. 985.

- L. C. Yu et al., MSF, TTP (2012), Vol. 717, p. 793.

- [23]

- G. Groeseneken et al., TED 31, 42 (1984).

G. Groeseneken et al., TED 38, 1820 (1991). [24]

- G. Van den Bosch et al., TED 38, 1820 (1991).

- T. Kimoto et al., WiPDA, IEEE (2013), p. 135.