# Mapping of CMOS FET degradation in bias space—Application to dram peripheral devices

B. Kaczer and J. FrancoS. TyaginovM. Jech, G. Rzepa, and T. GrasserB. J. O'Sullivan, R. Ritzenhaler, T. Schram, A. Spessot, D. Linten, and N. Horiguchi

Citation: Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials,

Processing, Measurement, and Phenomena 35, 01A109 (2017); doi: 10.1116/1.4972872

View online: http://dx.doi.org/10.1116/1.4972872

View Table of Contents: http://avs.scitation.org/toc/jvb/35/1

Published by the American Vacuum Society

### Articles you may be interested in

### In-depth study of the physics behind resistive switching in TiN/Ti/HfO2/W structures

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **35**, 01A11001A110 (2016); 10.1116/1.4973372

### Applications of clustering model to bimodal distributions for dielectric breakdown

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **35**, 01A11201A112 (2017); 10.1116/1.4972871

## Reliability improvements of TiN/Al2O3/TiN for linear high voltage metal-insulator-metal capacitors using an optimized thermal treatment

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **35**, 01A11101A111 (2017); 10.1116/1.4972232

### Impact of low thermal processes on reliability of high-k/metal gate stacks

Journal of Vacuum Science & Technology B, Nanotechnology and Microelectronics: Materials, Processing, Measurement, and Phenomena **35**, 01A11401A114 (2017); 10.1116/1.4973905

### Mapping of CMOS FET degradation in bias space—Application to dram peripheral devices

B. Kaczer<sup>a)</sup> and J. Franco imec, Kapeldreef 75, Leuven B-3001, Belgium

TU Vienna, Gusshausstrasse 27-29, Vienna A-1040, Austria and Ioffe Institute, Saint-Petersburg 194021, Russia

M. Jech. G. Rzepa, and T. Grasser

TU Vienna, Gusshausstrasse 27-29, Vienna A-1040, Austria

B. J. O'Sullivan, R. Ritzenhaler, T. Schram, A. Spessot, D. Linten, and N. Horiguchi imec, Kapeldreef 75, Leuven B-3001, Belgium

(Received 1 September 2016; accepted 5 December 2016; published 30 December 2016)

Mapping and visualization of all degradation modes in both n- and p-channel field effect transistors, specifically devices for dynamic random access memory periphery, is performed in the  $(V_G, V_D)$  bias space applicable for complementary metal-oxide-semiconductor operation. This "all-in-one" approach allows for tracking and studying in parallel all degradation regimes, including bias temperature instability, hot carrier degradation, and off-state stress, as well as the transitions between them. It should prove beneficial when developing new very large-scale integrated technologies, since it allows for simultaneous comparison and checking of all degradation regimes and promptly identifying "weak spots" of each technology option. It also allows to choose the correct criteria (voltages or fields) at a later time and postprocessing the data as necessary. © 2016 American Vacuum Society. [http://dx.doi.org/10.1116/1.4972872]

### I. INTRODUCTION

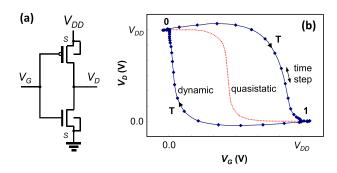

During operation of complementary metal-oxidesemiconductor (CMOS) digital circuits, transistors experience a range of combinations of gate  $V_G$  and drain  $V_D$  biases. An example for an n-channel and a p-channel Field Effect Transistor (nFET and pFET) in a logic inverter powered with supply voltage  $V_{DD}$  is given in Fig. 1. As the inverter input switches between logic levels, the  $V_G$  and  $V_D$  biases change, and consequently, the inverter FETs operate in different regimes.

In today's very large-scale integrated (VLSI) technologies, FET operation is accompanied by aging of the FETs, with a range of degradation regimes mapping onto the FET operation regimes. Specifically for the inverter at hand, when logic one, i.e.,  $V_{DD}$ , is applied to the gate, the nFET is "on" while the pFET is "off," and the inverter output  $V_D$  is 0 V. Consequently, no voltage is applied across the nFET source/ drain terminals, while full  $V_{DD}$  is applied across the pFET source/drain terminals. In this condition, the nFET is biased in a regime corresponding to bias temperature instability (BTI;  $|V_G| \sim V_{DD}$ ,  $V_D \sim 0 \text{ V}$ , while the pFET is biased in a regime referred to as off-state stress (OSS;  $V_G \sim 0 \, \text{V}$ ,  $|V_D| \sim V_{DD}$ , assuming the pFET biases are offset by  $V_{DD}$  so the source bias  $V_S = 0 \text{ V}$ ). <sup>3–8</sup> Conversely, for logic zero on the inverter input, the nFET undergoes OSS degradation while the pFET experiences BTI.

During the rapid switching between the two logic states, the inverter output  $V_D$  voltage momentarily lags behind the input (due to the considerable FET and interconnect impedances) and a combination of both nonzero  $V_G$  and  $V_D$  is

Given the above, we find it highly instructional to map the degradation in the entire  $(V_G, V_D)$  space applicable for CMOS FET operation. 13 The approach, reported here, allows for tracking and studying in parallel all degradation regimes,

Fig. 1. (Color online) (a) Inverter with input (gate voltage)  $V_G$  and output (drain voltage)  $V_D$ .  $V_{DD}$  is the (arbitrary) supply voltage. (b) Simulation of  $(V_G, V_D)$  combinations applied to an inverter subjected to  $\sim$ GHz digital signal (dynamic), compared to a slow sweep (quasistatic) (Ref. 1). "1" and "0" correspond to the logic state at the inverter input, "T" to the transition

briefly applied. In this regime, the FETs will undergo degradation due to carriers accelerated in the FET channel; hence, the term hot carrier degradation (HCD;  $|V_G|$  and  $|V_D| \sim V_{DD}$ ) is used.<sup>9,10</sup> Hot channel carriers in the subthreshold regime are also responsible for OSS, while only thermalized "equilibrium" carriers are present in the BTI regime. Appreciable gate oxide electric fields accelerating BTI are also present in sections of the gate oxide during all degradation regimes—a combination of degradation mechanisms is therefore taking place simultaneously as the FETs operate. 11,12 The relative contribution of each degradation mechanism will depend on the actual function of each FET in the circuit and the actual  $(V_G, V_D)$  workload on that device.

a) Electronic mail: kaczer@imec.be

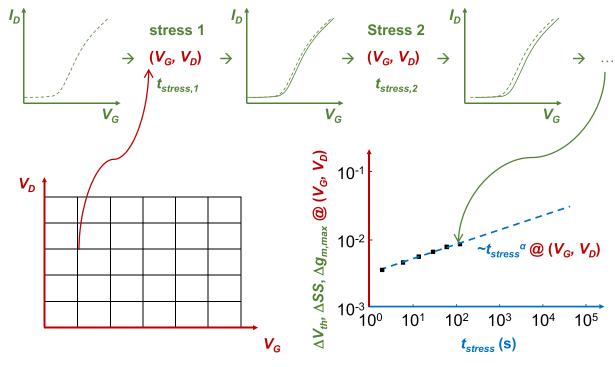

Fig. 2. (Color online) Schematic methodology applied in this work.

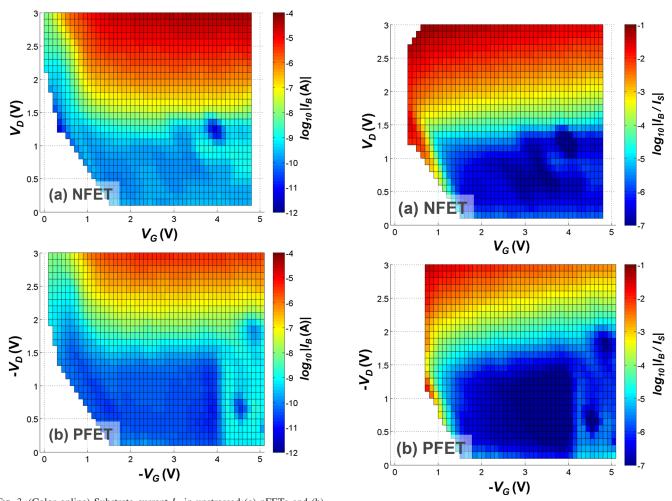

Fig. 3. (Color online) Substrate current  $I_B$  in unstressed (a) nFETs and (b) pFETs. A slight increase in background current in (b) for  $V_G < -4$  V is due to using less sensitive instrumentation for that part of the  $(V_G, V_D)$  matrix.

Fig. 4. (Color online) Multiplication factor  $I_B/I_S$  in unstressed (a) nFETs and (b) pFETs. Values at low  $|V_G|$ 's are not plotted as  $I_S$  is negligible there.

as well as the transitions between them. When developing new VLSI technologies, the "all-in-one" approach allows for simultaneous comparison and checking of all degradation regimes and promptly identifying "weak spots" of each technology option. Although not discussed here, the total degradation can be estimated by convoluting the actual device workload with the degradation maps. Furthermore, the simple and pragmatic methodology allows to gather sufficient reliability information in a systematic manner in a single pass and thus allows the experimenter to choose the correct criteria (voltages or fields) and postprocessing the data as necessary at a later time.

### II. EXPERIMENT

The only requirement of the methodology is the availability of a sufficient number of identical devices. We use  $\sim 100$  individual, nominally identical CMOS FETs, presently under development for dynamic random access memory periphery input—output applications  $(V_{DD} \sim 3 \text{ V})$ , <sup>14</sup> to map the degradation in the entire applicable  $(V_G, V_D)$  space. The simple measurement methodology is illustrated in Fig. 2. A fresh device with as-drawn  $L=70\,\mathrm{nm}$ ,  $W=1000\,\mathrm{nm}$ , and high-k gate

oxide with equivalent oxide thickness (EOT) ~4.5 nm is used here for every  $(V_G, V_D)$  combination selected from the matrix (Fig. 2, bottom left); low  $(V_G, V_D)$  combinations resulting in no appreciable stress are skipped. "Forward" (designated as fwd;  $V_D$  biased) and "reverse" (designated as rev;  $V_S$  biased) linear-regime I-V characteristics are measured, interlaced with stress phases at  $(V_G, V_D)$  with (exponentially) increasing stress times  $t_{\text{stress},i}$  and room temperature (Fig. 2, top). The *I-V* is adjusted during the *I-V* measurement to always guarantee sufficient information but simultaneously to avoid stressing the device. For the latter reason, measurement of saturation-regime I-V<sub>S</sub> is omitted altogether. In the experiment presented here, the precise I-V curve measurement is relatively slow ( $\sim 10 \,\mathrm{s}$  per sweep); hence, relaxation effects are not monitored. However, the experiment can be easily redesigned to perform relaxation measurements for each  $(V_G, V_D)$  combination, <sup>15</sup> as well as evaluation of other parameters.

Afterward, the threshold voltage  $V_{th}$ , the subthreshold slope SS, and the maximum transconductance  $g_{m,\max}$  are extracted from all I- $V_S$ , and the *shifts* with respect to the initial prestress values, designated by  $\Delta$ , are calculated, plotted versus the stress times  $t_{\text{stress}}$ , and fitted with a simple power

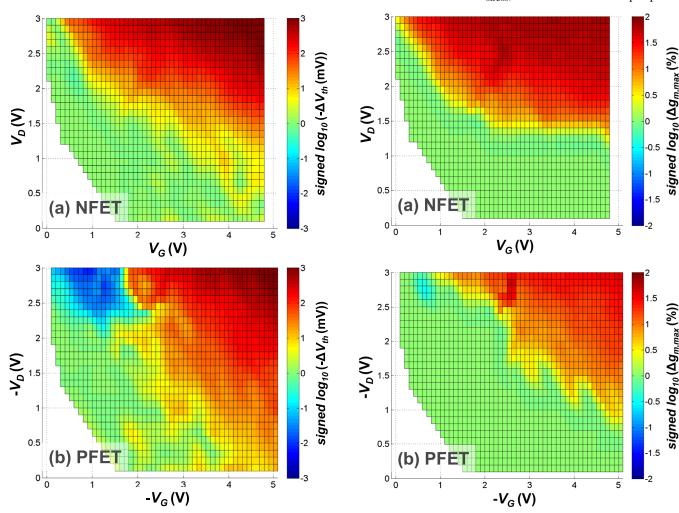

Fig. 5. (Color online) Degradation of threshold voltage  $V_{th}$  in (a) nFETs and (b) pFETs after 100 s, plotted vs  $(V_G, V_D)$ . Note pFET  $\Delta V_{th}$  changes sign between the OSS and HCD regimes.

Fig. 6. (Color online) Degradation of maximum transconductance  $g_{m,\text{max}}$ , normalized to the value before stress, in (a) nFETs and (b) pFETs after 100 s, plotted vs  $(V_G, V_D)$ .

law with exponent  $\alpha$  (Fig. 2). Fits of all quantities x at cumulative  $t_{\rm stress} = 100 \, {\rm s}$  are plotted for all  $(V_G, V_D)$  combinations  $(V_G \text{ and } V_D \text{ step size} = 0.3 \, {\rm V})$  and interpolated into contour plots. Function  ${\rm sign}(x).{\log_{10}}|x|$ , where  $|x| < min\_value \to x = min\_value$  is used to visualize data where applicable.

### **III. RESULTS AND DISCUSSION**

Figure 3 illustrates the typical contour plots resulting from the mapping of the entire applicable  $(V_G, V_D)$  space. Specifically, the figure shows the substrate current  $I_B$  extracted from unstressed devices at each  $(V_G, V_D)$  condition for both n and pFETs. The substrate current is a measure of impact ionization, which itself is indicative of the channel hot carrier energy. <sup>16,17</sup> Clearly, the channel carrier energy increases with increasing  $|V_D|$ , while the channel carriers remain "cold" in the BTI regime  $(|V_G| \sim V_{DD}, V_D \sim 0 \text{ V})$ .

The efficiency of hot carrier generation (hot carrier generation per channel carrier) can be assessed through the multiplication factor  $|I_B/I_S|$ , shown in Fig. 4.<sup>17</sup> It is apparent that the generation is the most efficient in the OSS regime ( $V_G \sim 0 \text{ V}$ ,  $|V_D| \sim V_{DD}$ ).

Figures 5–7 show the degradation of three important FET metrics: the threshold voltage  $V_{th}$ , the maximum

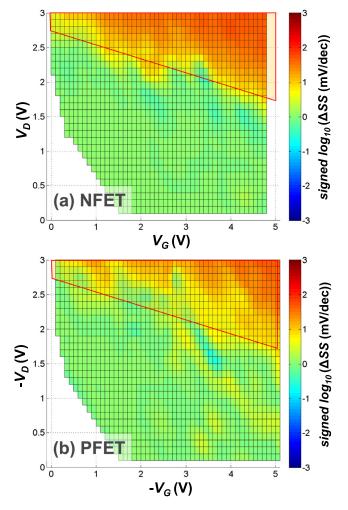

Fig. 7. (Color online) Degradation of subthreshold slope SS in (a) nFETs and (b) pFETs after 100 s, plotted vs  $(V_G,V_D)$ . Parts of  $(V_G,V_D)$  space showing degradation are demarcated.

transconductance  $g_{m,\text{max}}$ , and the subthreshold slope *SS*. From Figs. 5(a), 6(a), and 7(a), negligible positive BTI  $(V_G \sim V_{DD}, V_D \sim 0 \text{ V})$  degradation is apparent in the nFETs. This is understandable given the limited stress at room temperature. Some negative BTI (NBTI;  $V_G \sim V_{DD}, V_D \sim 0 \text{ V})$  degradation due to hole trapping is, however, already apparent in the pFETs [Fig. 5(b)]. It is also evident that NBTI still takes place at  $|V_D| > 0 \text{ V}$ , as the degradation extends above the horizontal  $(V_G)$  axis [Fig. 5(b)]. Neither maximum transconductance nor subthreshold slope is affected [Figs. 6(b) and 7(b), respectively].

Strong HCD ( $|V_G|$  and  $|V_D| \sim V_{DD}$ ) degradation is visible in both n and pFETs (Figs. 5–7), partially due to the FET junctions not having been optimized to reduce the lateral electric field. The HCD degradation tracks the maximum substrate current  $I_B$  (Fig. 3) for this channel length for both channel polarities. Degradation due to both gate oxide bulk charge trapping and interface state generation can be inferred, respectively, from  $\Delta V_{th}$  (Fig. 5) and  $\Delta SS$ ,  $\Delta g_{m,\max}$  (Figs. 6 and 7). The observed maximum  $\Delta V_{th}$  of  $\sim$ 1 V corresponds to an effective bulk trap density of  $\sim$ 4 × 10<sup>12</sup> cm<sup>-2</sup> (equivalent interface charge sheet) in the investigated gate stack, while the maximum  $\Delta SS$  of  $\sim$ 10 mV/dec corresponds to an interface state density of  $\sim$ 6 × 10<sup>11</sup> cm<sup>-2</sup>.

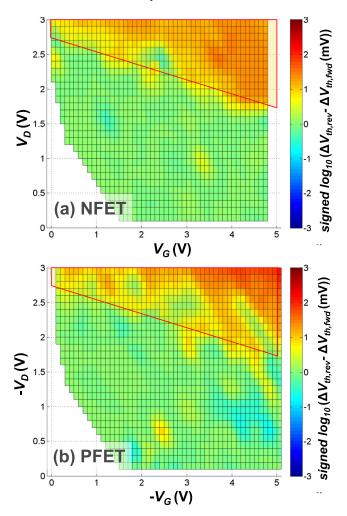

Fig. 8. (Color online) Localized degradation in (a) nFETs and (b) pFETs after 100 s, plotted vs  $(V_G, V_D)$ , inferred from  $\Delta V_{th,rev} - \Delta V_{th,fwd}$ .

Localization of the damage at the drain side in the HCD and OSS regimes can also be discerned from the nonzero difference of reverse and forward  $\Delta V_{th}$ 's in Fig. 8. <sup>18</sup> This particular quantity is sensitive to nonuniform charge formation in the channel. Clearly, a uniformly degraded FET will manifest the same  $\Delta V_{th}$  when measured in either source/drain direction (cf. Sec. II) and hence  $\Delta V_{th,rev} - \Delta V_{th,fwd}$  in such a case will be  $\sim$ 0 V, as is indeed the case outside the demarcated ( $V_G$ ,  $V_D$ ) space in Fig. 8. In contrast, nonzero  $\Delta V_{th,rev} - \Delta V_{th,fwd}$  will indicate nonuniform trap generation and charge trapping along the FET channel (at the drain side in our case). <sup>18</sup> Note that the demarcated ( $V_G$ ,  $V_D$ ) spaces in Figs. 7 and 8 are identical, likely indicating a common degradation mechanism.

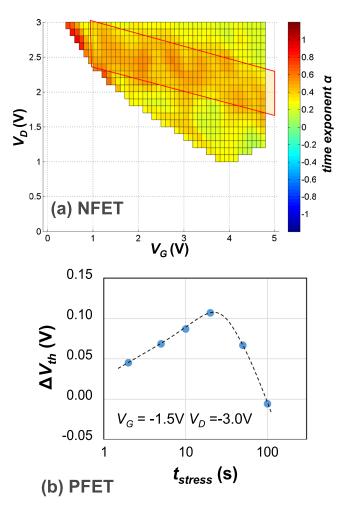

The stress-time power-law exponent  $\alpha$  (cf. Fig. 2) can be evaluated only for the nFETs [Fig. 9(a)]. The largest nFET  $\alpha$  values in Fig. 9(a) are observed in the delineated  $(V_G, V_D)$  region. At higher  $V_D$ 's, substantial  $\Delta V_{th}$  shifts are reached [cf. Fig. 3(a)] and saturation (i.e., a "deceleration") of the HCD  $t_{stress}$ -dependence takes place [cf. Fig. 9(a)]. Consequently, the values of  $\alpha$  are decreasing there.

Fig. 9. (Color online) (a) nFET time power-law exponent  $\alpha$  can be plotted in the entire  $(V_G, V_D)$  space since  $\Delta V_{th} > 0$  V (areas with  $\Delta V_{th} \sim 0$  V are suppressed in the plot). The region of  $(V_G, V_D)$  space with large  $\alpha$  is delineated. (b) An example of pFET time dependence in the OSS/HCD range of biases shows two opposite-polarity mechanisms taking place, preventing power-law fitting

In contrast to the nFETs, two concomitant oppositepolarity mechanisms take place in the pFET [Fig. 9(b)] between the OSS and HCD regimes [cf. Fig. 5(b)], preventing the extraction of  $\alpha$ . The additional mechanism is responsible for severe OSS  $(V_G \sim 0 \text{ V}, |V_D| \sim V_{DD})$  degradation in the pFETs, compared to the considerably weaker, albeit non-negligible OSS degradation in the nFETs [Figs. 5(a), 6(a), 7(a)]. The large positive  $\Delta V_{th}$  shifts in the OSS region of the pFET  $(V_G, V_D)$  space [Fig. 5(b)] indicate that electron trapping is taking place in addition to channel hole trapping. The trapped electrons are generated by impact ionization of channel holes in the drain region of the pFET. Recall that in the OSS regime the efficiency of this process is maximum [Fig. 3(b)].<sup>20</sup> We note that the final degradation can be calculated provided that the time dependences of both concomitant degradation mechanisms are properly modeled at each  $(V_G, V_D)$  combination.<sup>21</sup>

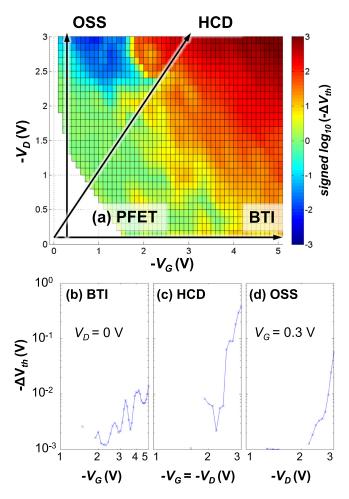

Finally, an example of postprocessing the data is shown in Fig. 10. Since the degradation data have been collected over the entire applicable  $(V_G, V_D)$  space, arbitrary "cut lines" can be taken in the space and the voltage acceleration of a given quantity can be extracted [Figs. 10(b)-10(d)] using a simple interpolation. The same methodology can be

Fig. 10. (Color online) (a) When a given degradation-monitor quantity [e.g.,  $\Delta V_{th}$  from Fig. 5(b)] is collected over the entire applicable ( $V_G$ ,  $V_D$ ) space, its voltage acceleration can be extracted along any cut line. Values of  $\Delta V_{th}$  pertaining to (b) BTI, (c) HCD, and (d) OSS cut lines are shown.

applied when comparing multiple technology options. In that case, however, the  $V_G$  axis and the given quantity have to be rescaled according to their respective  $V_{th}$  and EOT values or the electric fields, extracted, e.g., from the corresponding split C-V curves.

#### IV. CONCLUSIONS

In summary, mapping and visualization of all degradation modes in both n and pFETs has been performed in the applicable  $(V_G, V_D)$  bias space using a large number of nominally identical devices. This approach allows for studying all degradation regimes in parallel. The individual degradation regimes have been discussed here. This all-in-one approach should prove beneficial when developing new VLSI technologies, since it allows for simultaneous comparison and checking of all degradation regimes and promptly identifying weak spots of each technology option and postprocessing the data as necessary at a later time.

### **ACKNOWLEDGMENTS**

This work was performed as part of imec's Core Partner Program. The imec Core CMOS program members, the imec pilot line, and amsimec are gratefully acknowledged for their support.

- <sup>1</sup>B. Kaczer, F. Crupi, R. Degraeve, Ph. Roussel, C. Ciofi, and G. Groeseneken, *International Electron Device Meeting (IEDM)*, *Technical Digest* (2002), pp. 171–174.

- <sup>2</sup>K. Zhao, S. Krishnan, B. Linder, and J. H. Stathis, *Bias Temperature Instability for Devices and Circuits*, edited by T. Grasser (Springer, New York, Heidelberg, Dordrecht, London, 2014), Chap. 21.

- <sup>3</sup>A. Muehlhoff, Microelectron. Reliab. **41**, 1289 (2001).

- <sup>4</sup>K. Hofmann, S. Holzhauser, and C. Y. Kuo, Integrated Reliability Workshop (IRW) Final Report, 2004, pp. 94–98.

- <sup>5</sup>D. Varghese, H. Kufluoglu, V. Reddy, H. Shichijo, S. Krishnan, and M. A. Alam, *International Electron Device Meeting (IEDM), Technical Digest* (2006), pp. 1–4.

- <sup>6</sup>N. H. Lee, D. Baek, and B. Kang, IEEE Electron Device Lett. **32**, 856 (2011).

- <sup>7</sup>A. Spessot, M. Aoulaiche, M. Cho, J. Franco, T. Schram, R. Ritzenthaler, and B. Kaczer, *44th European Solid State Device Research Conference* (ESSDERC) (2014), pp. 365–368.

- <sup>8</sup>M. Cho, A. Spessot, B. Kaczer, M. Aoulaiche, R. Ritzenthaler, T. Schram, P. Fazan, N. Horiguchi, and D. Linten, *International Conference on IC Design and Technology (ICICDT)* (2015), pp. 1–4.

- <sup>9</sup>S. Tyaginov and T. Grasser, *Tutorial at International Integrated Reliabilty Workshop (IIRW)* (2012).

- <sup>10</sup>A. Bravaix, C. Guerin, V. Huard, D. Roy, J. M. Roux, and E. Vincent, Proceedings of the International Reliability Physics Symposium (IRPS) (2009), pp. 531–548.

- <sup>11</sup>X. Federspiel, M. Rafik, D. Angot, F. Cacho, and D. Roy, *Proceedings of the International Reliability Physics Symposium (IRPS)* (2013), pp. XT.9.1–XT.9.4.

- <sup>12</sup>G. A. Rott, K. Rott, H. Reisinger, W. Gustin, and T. Grasser, Microelectron. Reliab. 54, 2310 (2014).

- <sup>13</sup>G. A. Rott, H. Nielen, H. Reisinger, W. Gustin, S. Tyaginov, and T. Grasser, International Integrated Reliability Workshop (IIRW), Final Report, 2013, pp. 73–77.

- <sup>14</sup>S. Y. Cha, Short Course at International Electron Device Meeting (IEDM) (2011)

- <sup>15</sup>B. Kaczer, T. Grasser, Ph. J. Roussel, J. Martin-Martinez, R. O'Connor, B. J. O'Sullivan, and G. Groeseneken, *Proceedings of the International Reliability Physics Symposium (IRPS)* (2008), pp. 20–27.

- <sup>16</sup>C. Hu, S. C. Tam, F.-C. Hsu, P.-K. Ko, T.-Y. Chan, and K. W. Terrill, IEEE Trans. Electron Devices 32, 375 (1985).

- <sup>17</sup>P. Heremans, R. Bellens, G. Groeseneken, and H. E. Maes, IEEE Trans. Electron Devices 35, 2194 (1988).

- <sup>18</sup>T.-C. Ong, P. K. Ko, and C. Hu, IEEE Trans. Electron Devices 37, 1658 (1990)

- <sup>19</sup>I. Starkov, H. Enichlmair, S. E. Tyaginov, and T. Grasser, *Proceedings of the International Reliability Physics Symposium (IRPS)* (2012), pp. XT.7.1–XT.7.6.

- <sup>20</sup>M. Toledano-Luque, B. Kaczer, M. Aoulaiche, A. Spessot, Ph. J. Roussel, R. Ritzenthaler, T. Schram, A. Thean, and G. Groeseneken, Microelectron. Eng. 109, 314 (2013).

- <sup>21</sup>M. Koyanagi, A. G. Lewis, R. A. Martin, T.-Y. Huang, and J. Y. Chen, IEEE Trans. Electron Devices 34, 839 (1987).