# Reliability of Next-Generation Field-Effect Transistors with Transition Metal Dichalcogenides

Yu.Yu. Illarionov\*†, A.J. Molina-Mendoza‡, M. Waltl\*, T. Knobloch\*, M.M. Furchi‡, T. Mueller‡ and T. Grasser\*

- \* Institute for Microelectronics, TU Wien, Austria

- † Ioffe Physical-Technical Institute, Russia

- ‡ Institute for Photonics, TU Wien, Austria

Abstract—We perform a detailed reliability study of MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub> and WS<sub>2</sub> field-effect transistors fabricated on the same SiO<sub>2</sub>/Si substrate. First we analyze the sensitivity of these devices to adsorbate-type trapping sites on top of the channel and show that their contribution can be minimized at high temperatures, which leads to a domination of charge trapping by oxide traps. Then we compare the high-temperature dynamics of the hysteresis and bias-temperature instabilities for different devices. Our results show that the observed differences can be partially explained by the alignment of known defect bands in SiO<sub>2</sub> relative to the conduction and valence band edges of the two-dimensional channel materials. As such, our study provides strong fundamental insights into the reliability of these new technologies and opens further perspectives on how to reach commercial quality standards.

#### I. Introduction

Transition metal dichalcogenides (TMDs) present a wide class of two-dimensional (2D) materials which includes fascinating "beyond-graphene" semiconductors such as MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub>, WS<sub>2</sub> and WSe<sub>2</sub> [1–5]. Contrary to graphene [6], TMDs have sizable electronic bandgaps ranging from 1.7 eV for MoTe<sub>2</sub> to 2.5 eV for MoS<sub>2</sub> in the single-layer (1L) limit [7]. Owing to this, these materials are potentially interesting for channel applications in next-generation digital 2D electronics. At the same time, the recently achieved epitaxial growth of semiconducting TMDs [8, 9] represents a breakthrough for very large scale integration.

By now, several research groups have succeded at fabricating field-effect transistors (FETs) with MoS<sub>2</sub> [10–14], MoSe<sub>2</sub> [15], MoTe<sub>2</sub> [16], WS<sub>2</sub> [17] and WSe<sub>2</sub> [5]. Both n-FETs and p-FETs with various TMD channels have been demonstrated, as well as the possibility to adjust Schottky barriers between source/drain and channel to obtain n-type and p-type transistors using the same TMD material [18]. These achievements are very important for future CMOS circuit integration of TMD-based FETs, which requires both n- and p-FETs. However, commercialization of these next-generation devices is not possible without proper understanding and improvement of their reliability, which should be urgently addressed. By now, more or less detailed reliability studies have been performed only for MoS<sub>2</sub> FETs [14, 19]. In particular, it has been found that these devices suffer from charge trapping by both oxide traps [13, 14, 19, 20] and adsorbate-type trapping sites (e.g. water molecules) on the MoS<sub>2</sub> channel [10–12, 14]. This charge trapping leads to considerable hysteresis [10, 11, 13, 14] and bias-temperature instabilities (BTI) of the gate transfer characteristics [12, 14, 20]. While the contribution

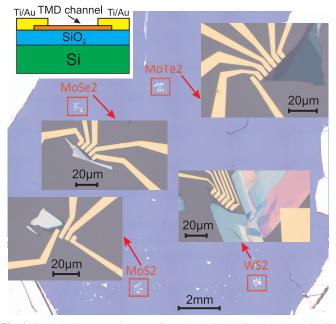

**Fig. 1:** Optical microscope images of our 1L MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub> and WS<sub>2</sub> FETs fabricated on the same chip. The devices are of a back-gated configuration with 90nm thick SiO<sub>2</sub> as a gate insulator and Ti(5nm)/Au(30nm) source and drain pads (see the schematic cross-section on top). The channel length is  $L=1.5\,\mu\mathrm{m}$  and the widths W are between 0.5 and  $8\,\mu\mathrm{m}$  for different devices.

from adsorbates can be minimized by treatment of the devices at higher temperatures [14], we argue that charge trapping by oxide traps, which are energetically aligned within certain defect bands [19,21,22], is dependent on the selected combination of the channel and insulator materials. In order to provide more insight into this hypothesis, we perform a detailed reliability study of MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub> and WS<sub>2</sub> FETs fabricated on the same SiO<sub>2</sub>/Si substrate and compare the results obtained for different devices.

## II. DEVICES

Our devices are back-gated 1L MoS<sub>2</sub>, MoSe<sub>2</sub>, MoTe<sub>2</sub> and WS<sub>2</sub> FETs with 90 nm thick SiO<sub>2</sub> as a gate insulator. For a proper comparison of the reliability characteristics, the devices have been fabricated on the same SiO<sub>2</sub>/Si substrate and using the same deterministic transfer method of [23]. First, the flakes of different TMD materials have been exfoliated from the bulk crystals using Nitto tape and a polydimethylsiloxane (PDMS) stamp. Then the PDMS surface containing exfoliated

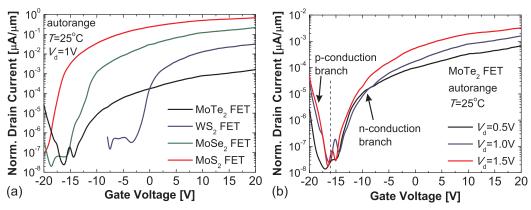

Fig. 2: (a) The  $I_D$ - $V_G$  characteristics of four different TMD FETs measured at  $V_D = 1$  V using the autorange mode. The current is normalized by the channel width W. (b) While MoS<sub>2</sub>, MoSe<sub>2</sub> and WS<sub>2</sub> devices are n-FETs, the MoTe<sub>2</sub> FET exhibits clear ambipolar behaviour. This is likely due to the smallest bandgap of MoTe<sub>2</sub> (1.7 eV) and also a smaller Schottky barrier for holes.

crystals has been scanned with an optical microscope in transmission mode, in order to identify single-layer flakes. After this, the desired flakes have been transferred onto the  ${\rm SiO_2}$  surface. Finally,  ${\rm Ti}(5\,{\rm nm})/{\rm Au}(30\,{\rm nm})$  source/drain pads have been created using standard e-beam lithography. The optical microscope images of our chip with different devices and the schematic device layout are shown in Fig. 1. TMD flakes are contacted by several pads which allowed us to obtain several devices for each material.

### III. EXPERIMENT

In order to avoid the detrimental impact of the ambient [11], all our measurements have been performed in a vacuum  $(\sim 5 \times 10^{-6} \text{ torr})$  at  $T = 25^{\circ}\text{C}$  and  $100^{\circ}\text{C}$ . First we have measured the gate transfer  $(I_D-V_G)$  characteristics using the autorange mode, which was necessary to verify the performance of our devices. Then we analyzed the hysteresis dynamics by measuring the  $I_D$ - $V_G$  characteristics using forward  $(V^+)$  and reversed  $(V^{-})$  sweep directions and different measurement frequencies  $f = 1/(Nt_{\text{step}})$ , with N being the number of  $V_{\text{G}}$ steps given by the step voltage  $V_{\text{step}}$  and  $t_{\text{step}}$  the sampling time [14]. Finally, we examined the BTI degradation and recovery dynamics by applying subsequent stress/recovery cycles with logarithmically increased stress times  $t_s$  [14, 24]. Similarly to a technique previously used for Si devices [25] and encapsulated MoS<sub>2</sub> FETs [26], a constant gate voltage was applied during both stress  $(V_S)$  and recovery  $(V_R)$ . The latter was necessary to minimize uncontrollable drifts of the potential at the back gate which is formed by the Si substrate, and thus make the results more reproducible. Furthermore, in order to maximally stabilize the device, we applied the recovery voltage  $V_R$  during few hours before the beginning of our BTI stress/recovery cycles. Also, in some cases we monitored the evolution of the  $I_D$ - $V_G$  curves during both stress and recovery.

## IV. RESULTS AND DISCUSSIONS

In Fig. 2a we show the  $I_D$ - $V_G$  characteristics measured using the autorange mode for all four TMD devices. The on/off current ratios vary from  $\sim 10^5$  for MoTe<sub>2</sub> FETs to  $> 10^7$  for MoSe<sub>2</sub> devices. Also, in agreement with literature reports [16],

MoTe<sub>2</sub> devices exhibit both electron and hole conduction, known as ambipolar behaviour (Fig. 2b). This feature originates from the comparably small electronic bandgap of MoTe<sub>2</sub> ( $\sim 1.7\,\mathrm{eV}$ ) [7] and likely a smaller Schottky barrier for holes compared to other TMDs. The presence of both n- and p-FET performance considerably extends possible applications of MoTe<sub>2</sub> FETs in integrated logic CMOS circuits, especially taking into account the reasonable on/off current ratio observed for these devices.

In Fig. 3a we compare the  $I_D$ - $V_G$  characteristics measured for different TMD devices at  $T = 100^{\circ}$ C using the sweep rate S = 0.02V/s, which corresponds to a total time of a return sweep between -20 and 20 V of more than an hour. Following our methodology from [14], we extract the hysteresis width  $\Delta V_{\rm H}$  around the threshold voltage  $V_{\rm th}$  from the  $I_{\rm D}$ - $V_{\rm G}$ characteristics measured using different sweep rates and plot them versus the measurement frequency f (Fig. 3b). Clearly, the largest hysteresis is observed for the MoTe<sub>2</sub> and MoSe<sub>2</sub> devices and the smallest is visible for the MoS<sub>2</sub> and WS<sub>2</sub> FETs. In order to understand the origin of this hysteresis, in Fig. 3c we compare the slow sweep hysteresis widths measured at  $T = 25^{\circ}\text{C}$ ,  $100^{\circ}\text{C}$  and  $25^{\circ}\text{C}$  after a week at  $100^{\circ}\text{C}$ . In agreement with our previous study [14], for the MoS<sub>2</sub> FET the hysteresis becomes smaller during and after the 100°C treatment. We speculate that this is due to the evaporation of a considerable number of adsorbates, most of which do not return to the MoS<sub>2</sub> surface after the temperature is decreased to 25°C. As for the WS2 and MoTe2 FETs, we observe an insignificant increase of the hysteresis at  $T = 100^{\circ}$ C, which likely means that the initial concentration of adsorbates is not that large. As such, in these devices thermal activation of charge trapping by oxide traps in SiO<sub>2</sub> and other remaining defects dominates over the annealing of adsorbates from the TMD surface. However, after the end of the 100°C treatment, the hysteresis in WS<sub>2</sub> and MoTe<sub>2</sub> FETs becomes even larger than it was before. This means that a number of new trapping sites have appeared on the TMD channel surface. Something similar is observed also for the MoSe<sub>2</sub> device, although at  $T = 100^{\circ}$ C the hysteresis was decreased, similar to the MoS<sub>2</sub> device. The latter means that the initial number of adsorbates on the surface of MoS<sub>2</sub> and MoSe<sub>2</sub> is relatively larger than for

Fig. 3: (a) The  $I_{\rm D}$ - $V_{\rm G}$  characteristics of four different TMD FETs measured at  $T=100^{\circ}{\rm C}$  using  $S=0.02{\rm V/s}$ . (b) The corresponding  $\Delta V_{\rm H}(f)$  dependences. (c) Maximum hysteresis widths measured for our TMD FETs before, during and after the  $T=100^{\circ}{\rm C}$  treatment. A decrease of  $\Delta V_{\rm H}$  at higher temperature and its increase after temperature treatment observed for our devices presents a clear proof that the hysteresis is partially due to adsorbate-type trapping sites. In order to minimize their impact, all following measurements have been performed at  $T=100^{\circ}{\rm C}$ .

WS<sub>2</sub> and MoTe<sub>2</sub>, which makes their annealing dominate over the thermal activation of the remaining defects like oxide traps. At the same time, we believe that an increase of the hysteresis after the 100°C treatment in WS2, MoTe2 and MoSe2 FETs is associated with the chemical properties of these TMDs. Namely, these materials are able to attract a large number of adsorbates which have been previously evaporated from the large area of the whole chip surface, which is in contrast to MoS<sub>2</sub>. Taking into account this difference between MoS<sub>2</sub> and the other three TMD materials, we conclude that a proper comparison of the reliability characteristics for all four devices is more favourable at  $T = 100^{\circ}$ C rather than at  $T = 25^{\circ}$ C after baking. This is because the impact of adsorbates on the total drifts of the  $I_D$ - $V_G$  characteristics is considerably reduced at T = 100°C. Together with some thermal activation, this makes the contribution of charge trapping by oxide traps in SiO<sub>2</sub>, which we are mostly interested in, more visible.

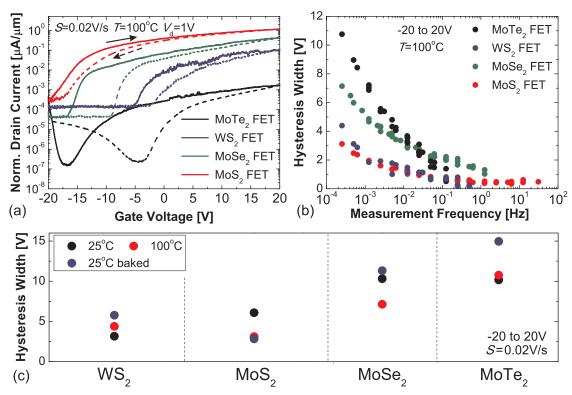

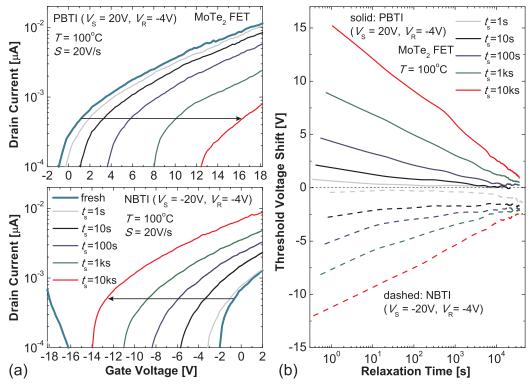

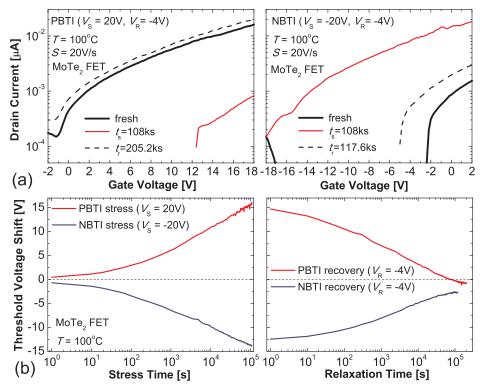

In Fig. 4 we show the evolution of the  $I_D$ - $V_G$  characteristics and the corresponding recovery traces for the threshold voltage shifts  $\Delta V_{\rm th}$  corresponding to positive and negative BTI (PBTI and NBTI, respectively) measured at  $T=100^{\circ}{\rm C}$  for our WS<sub>2</sub> device. While the extracted threshold voltage shifts are considerable, in the case of PBTI the degradation tends to recover completely after several hours. Furthermore, some over-recovery is observed, which is likely because the recovery voltage  $V_R=-4{\rm V}$  corresponds to NBTI bias condition. At the same time, the NBTI recovery at  $V_R=-2{\rm V}$  is incomplete and contains some permanent component. The latter likely

means that  $V_R = -2V$  is still within the NBTI bias range. This prevents relaxation of all defects which have changed their charge states during the NBTI stress at  $V_S = -20\,\text{V}$ . The related results for our ambipolar MoTe<sub>2</sub> device (Fig. 5) show that the magnitudes of both PBTI and NBTI degradations are larger than for the WSe<sub>2</sub> device. At the same time, the PBTI degradation of MoTe<sub>2</sub> FETs is stronger than NBTI, though being recoverable by more than 90% after several hours. In contrast, the recovery of the originally less pronounced NBTI degradation contains a larger permanent component. Also, for smaller stress times the NBTI shifts tend to increase during recovery, which is somehow similar to our previous observations for Si technologies [27].

In Fig. 6 we continue our analysis of the PBTI and NBTI dynamics in the MoTe<sub>2</sub> FET by measuring the evolution of the  $I_{\rm D}$ - $V_{\rm G}$  characteristics during both stress at  $V_{\rm S}=\pm20\,\rm V$  and recovery at  $V_{\rm R}=-4\,\rm V$ , with stress and relaxation times of as long as  $\sim10^5\rm s$ . The stress traces obtained for NBTI and PBTI are more or less similar, with some domination of PBTI over NBTI, making the results consistent with Fig. 5. In contrast, the recovery traces for PBTI and NBTI are considerably different. Namely, the PBTI trace exhibits a complete recovery and saturates slightly below the original  $V_{\rm th}$ . At the same time, NBTI recovery is not complete and contains some permanent component which is conserved even after a long relaxation time. These observations allow us to conclude that  $V_{\rm R}=-4\,\rm V$  corresponds to NBTI bias condition.

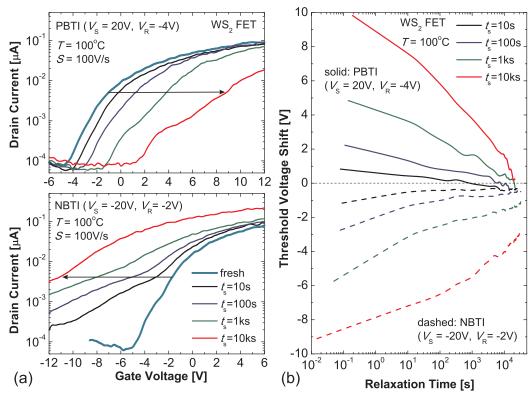

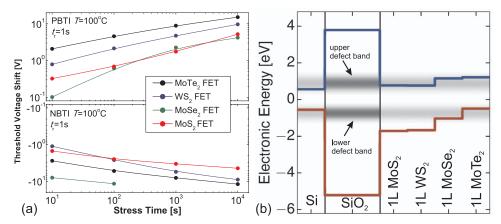

Finally, in Fig. 7 we compare the PBTI and NBTI shifts

Fig. 4: (a) Evolution of the  $I_{\rm D}$ - $V_{\rm G}$  characteristics of our WS $_2$  FETs after subsequent PBTI (top) and NBTI (bottom) stresses with increasing stress times measured at  $T=100^{\rm o}$ C. (b) The corresponding recovery traces for  $\Delta V_{\rm th}$ . While the threshold voltage shifts are considerable, the PBTI traces exhibit weak over-recovery. This likely means that  $V_{\rm R}=-4$  V corresponds to NBTI bias condition. Conversely, for the same reason NBTI recovery at  $V_{\rm R}=-2$  V contains some permanent component.

Fig. 5: (a) Evolution of the  $I_D$ - $V_G$  characteristics of our MoTe<sub>2</sub> FETs after subsequent PBTI (top) and NBTI (bottom) stresses with increasing stress times. (b) The corresponding recovery traces. PBTI degradation is stronger and more recoverable than NBTI containing a larger permanent component. For smaller stress times the NBTI shift tends to increase during recovery.

Fig. 6: (a) Evolution of the  $I_D$ - $V_G$  characteristics of our MoTe<sub>2</sub> device after long PBTI (left) and NBTI (right) stresses and recovery. (b) The corresponding stress (left) and recovery (right) traces for  $\Delta V_{th}$ . The PBTI trace exhibits slight over-recovery and NBTI contains some permanent component.

Fig. 7: (a) Comparison of PBTI (top) and NBTI (bottom) shifts at  $t_r = 1$  s versus stress time for all four devices. (b) The band diagram showing the band edges of our TMDs aligned to SiO<sub>2</sub>; two known oxide defect bands are shown in grey. In MoSe<sub>2</sub> and MoTe<sub>2</sub> FETs charge trapping is likely due to both defect bands, which leads to considerable PBTI and NBTI (especially for MoSe<sub>2</sub> FETs) degradation. In contrast, for MoSe<sub>2</sub> and WSe<sub>2</sub> FETs the lower defect band is relatively far from the valence band, which makes the contribution of the upper defect band dominant. This is consistent with comparably small NBTI shifts and hysteresis observed for these devices.

for all four devices at the relaxation time  $t_r = 1$  s (Fig. 7a) and notice that the difference in the degradation magnitudes can be partially explained based on the band diagram provided in Fig. 7b. This band diagram shows the defect bands known for SiO<sub>2</sub> from our previous works for Si technologies [28], black phosphorus [21] and MoS<sub>2</sub> [19] FETs with the theoretical band offsets for our TMD materials based on [7]. We argue that if the contribution of adsorbates is minimized and charge trapping is dominated by oxide traps in SiO<sub>2</sub>, as it should be at  $T = 100^{\circ}$ C, the magnitudes of the hysteresis and BTI will be mostly determined by the energetic alignment of these defect

bands relative to the conduction and valence band edges of a certain TMD channel material. In particular, the upper defect band in SiO<sub>2</sub> is quite close to the conduction bands of all four TMDs, which is consistent with sizable BTI shifts in all our devices. At the same time, for MoSe<sub>2</sub> and MoTe<sub>2</sub> FETs charge trapping is likely to have a sizable contribution also from the lower defect band, which is quite close to the valence band of these materials. This is fully consistent with the stronger NBTI shifts observed for the MoSe<sub>2</sub> FET, as well as with stronger PBTI and NBTI for the MoTe<sub>2</sub> device. In contrast, for MoS<sub>2</sub> and WS<sub>2</sub> devices the contribution of the lower defect band is

negligible. This is consistent with weaker NBTI and smaller hysteresis (Fig. 3b) in the  $MoS_2$  and  $WS_2$  FETs. At the same time, we can conclude that for all four TMDs the alignment of the  $SiO_2$  defect bands is not very favourable, especially for the ambipolar  $MoTe_2$  device. Therefore, in order to improve the reliability of TMD FETs, one would need to use gate insulators other than  $SiO_2$ .

#### V. CONCLUSIONS

We have performed a first comprehensive reliability study of different TMD FETs fabricated on the same SiO<sub>2</sub> substrate. First we have analyzed the sensitivity of these devices to adsorbate-type trapping sites. We found that in all TMD devices the contribution of adsorbates can be minimized at higher temperature. However, only the MoS<sub>2</sub> FETs conserve the reliability improvement after the temperature is decreased again. As such, we concluded that charge trapping by oxide traps in bare TMD FETs should be studied at higher temperatures. Then, we have compared the hysteresis and BTI degradation/recovery dynamics for different TMD FETs and found that the difference in the measured hysteresis widths and threshold voltage shifts can be partially explained by the relative alignment of the conduction and valence band edges of the TMDs with the defect bands in SiO<sub>2</sub>. Although for the investigated TMDs this alignment is not favourable, our study provides fundamental insights into the understanding of the reliability of the next-generation TMD FETs and opens new possibilities for decreasing the impact of charge trapping by oxide traps in these devices.

## VI. ACKNOWLEDGEMENTS

The authors acknowledge the financial support through the Austrian Science Fund (FWF) grant n° 12606-N30.

#### REFERENCES

- [1] Y. Ding, Y. Wang, J. Ni, L. Shi, S. Shi, and W. Tang, "First Principles Study of Structural, Vibrational and Electronic Properties of Graphene-like MX<sub>2</sub> (M = Mo, Nb, W, Ta; X = S, Se, Te) Monolayers," *Physica B: Condensed Matter*, vol. 406, no. 11, pp. 2254–2260, 2011.

- [2] E. Kadantsev and P. Hawrylak, "Electronic Structure of a Single MoS<sub>2</sub> Monolayer," *Solid State Communications*, vol. 152, pp. 909–913, 2012.

- [3] A. Geim and I. Grigorieva, "Van der Waals Heterostructures," *Nature*, vol. 499, pp. 419–425, 2013.

- [4] T. Georgiou, H. Yang, R. Jalil, J. Chapman, K. Novoselov, and A. Mishchenko, "Electrical and Optical Characterization of Atomically Thin WS<sub>2</sub>," *Dalton Transactions*, vol. 43, pp. 10388–10391, 2014.

- [5] A. Allain and A. Kis, "Electron and Hole Mobilities in Single-Layer WSe<sub>2</sub>," ACS Nano, vol. 8, no. 7, pp. 7180–7185, 2014.

- [6] K. Novoselov, A. Geim, S. Morozov, D. Jiang, Y. Zhang, S. Dubonos, I. Grigorieva, and A. Firsov, "Electric Field Effect in Atomically Thin Carbon Films," *Science*, vol. 306, no. 5696, pp. 666–669, 2004.

- [7] F. Rasmussen and K. Thygesen, "Computational 2D Materials Database: Electronic Structure of Transition-Metal Dichalcogenides and Oxides," *Journal of Physical Chemistry C*, vol. 119, no. 23, pp. 13 169–13 183, 2015.

- [8] Q. Ji, Y. Zhang, T. Gao, Y. Zhang, D. Ma, M. Liu, Y. Chen, X. Qiao, P.-H. Tan, M. Kan, J. Feng, Q. Sun, and Z. Liu, "Epitaxial Monolayer MoS<sub>2</sub> on Mica with Novel Photoluminescence," *Nano Letters*, vol. 13, no. 8, pp. 3870–3877, 2013.

- [9] A. Roy, H. Movva, B. Satpati, K. Kim, R. Dey, A. Rai, T. Pramanik, S. Guchhait, E. Tutuc, and S. Banerjee, "Structural and Electrical Properties of MoTe<sub>2</sub> and MoSe<sub>2</sub> Grown by Molecular Beam Epitaxy," ACS Applied Materials & Interfaces, vol. 8, no. 11, pp. 7396–7402, 2016.

- [10] H. Qiu, L. Pan, Z. Yao, J. Li, Y. Shi, and X. Wang, "Electrical Characterization of Back-gated Bi-layer MoS<sub>2</sub> Field-effect Transistors and the Effect of Ambient on Their Performances," *Applied Physics Letters*, vol. 100, p. 123104, 2012.

- [11] D. Late, B. Liu, H. Matte, V. Dravid, and C. Rao, "Hysteresis in Single-Layer MoS<sub>2</sub> Field Effect Transistors," ACS Nano, vol. 6, pp. 5635–5641, 2012.

- [12] K. Cho, W. Park, J. Park, H. Jeong, J. Jang, T.-Y. Kim, W.-K. Hong, S. Hong, and T. Lee, "Electric Stress-Induced Threshold Voltage Instability of Multilayer MoS<sub>2</sub> Field Effect Transistors," ACS Nano, vol. 7, pp. 7751–7758, 2013.

- [13] Y. Guo, X. Wei, J. Shu, B. Liu, J. Yin, C. Guan, Y. Han, S. Gao, and Q. Chen, "Charge Trapping at the MoS<sub>2</sub>-SiO<sub>2</sub> Interface and its Effects on the Characteristics of MoS<sub>2</sub> Metal-Oxide-Semiconductor Field Effect Transistors," Applied Physics Letters, vol. 106, no. 10, p. 103109, 2015.

- [14] Y. Illarionov, G. Rzepa, M. Waltl, T. Knobloch, A. Grill, M. Furchi, T. Mueller, and T. Grasser, "The Role of Charge Trapping and MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN Field-Effect Transistors," 2D Materials, vol. 3, p. 035004, 2016.

- [15] S. R. Das, J. Kwon, A. Prakash, C. J. Delker, S. Das, and D. B. Janes, "Low-Frequency Noise in MoSe<sub>2</sub> Field Effect Transistors," *Applied Physics Letters*, vol. 106, no. 8, p. 083507, 2015.

- [16] Y.-F. Lin, Y. Xu, S.-T. Wang, S.-L. Li, M. Yamamoto, A. Aparecido-Ferreira, W. Li, H. Sun, S. Nakaharai, W.-B. Jian, K. Ueno, and K. Tsukagoshi, "Ambipolar MoTe<sub>2</sub> Transistors and Their Applications in Logic Circuits," *Advanced Materials*, vol. 26, no. 20, pp. 3263–3269, 2014.

- [17] J. Kumar, M. A. Kuroda, M. Z. Bellus, S.-J. Han, and H.-Y. Chiu, "Full-Range Electrical Characteristics of WS<sub>2</sub> Transistors," *Applied Physics Letters*, vol. 106, no. 12, p. 123508, 2015.

- [18] X.-X. Li, Z.-Q. Fan, P.-Z. Liu, M.-L. Chen, X. Liu, C.-K. Jia, D.-M. Sun, X.-W. Jiang, Z. Han, V. Bouchiat, J.-J. Guo, J.-H. Chen, and Z.-D. Zhang, "Gate-Controlled Reversible Rectifying Behaviour in Tunnel Contacted Atomically-Thin MoS<sub>2</sub> Transistor," *Nature Communications*, vol. 8, no. 1, p. 970, 2017.

- [19] Y. Illarionov, T. Knobloch, M. Waltl, G. Rzepa, A. Pospischil, D. Polyushkin, M. Furchi, T. Mueller, and T. Grasser, "Energetic Mapping of Oxide Traps in MoS<sub>2</sub> Field-Effect Transistors," 2D Materials, vol. 4, no. 2, p. 025108, 2017.

- [20] S. Yang, S. Park, S. Jang, H. Kim, and J.-Y. Kwon, "Electrical Stability of Multilayer MoS<sub>2</sub> Field-Effect Transistor under Negative Bias Stress at Various Temperatures," *Physica Status Solidi (RRL) - Rapid Research Letters*, vol. 8, pp. 714–718, 2014.

- [21] Y. Illarionov, M. Waltl, G. Rzepa, J.-S. Kim, S. Kim, A. Dodabalapur, D. Akinwande, and T. Grasser, "Long-term Stability and Reliability of Black Phosphorus Field-Effect Transistors," ACS Nano, vol. 10, no. 10, pp. 9543–9549, 2016.

- pp. 9543–9549, 2016.

[22] Y. Illarionov, M. Waltl, G. Rzepa, T. Knobloch, J.-S. Kim, D. Akinwande, and T. Grasser, "Highly-Stable Black Phosphorus Field-Effect Transistors with Low Density of Oxide Traps," npj 2D Materials and Applications, vol. 1, no. 1, p. 23, 2017.

- [23] A. Castellanos-Gomez, M. Buscema, R. Molenaar, V. Singh, L. Janssen, H. S. van der Zant, and G. A. Steele, "Deterministic Transfer of Two-Dimensional Materials by All-Dry Viscoelastic Stamping," 2D Materials, vol. 1, no. 1, p. 011002, 2014.

- [24] Y. Illarionov, A. Smith, S. Vaziri, M. Ostling, T. Mueller, M. Lemme, and T. Grasser, "Bias-Temperature Instability in Single-Layer Graphene Field-Effect Transistors," *Applied Physics Letters*, vol. 105, no. 14, p. 143507, 2014.

- [25] T. Grasser, P.-J. Wagner, H. Reisinger, T. Aichinger, G. Pobegen, M. Nelhiebel, and B. Kaczer, "Analytic Modeling of the Bias Temperature Instability Using Capture/Emission Time Maps," in *IEEE International Electron Devices Meeting (IEDM)*, Dec. 2011, pp. 27.4.1–27.4.4.

- [26] Y. Illarionov, K. Smithe, M. Waltl, T. Knobloch, E. Pop, and T. Grasser, "Improved Hysteresis and Reliability of MoS<sub>2</sub> Transistors with High-Quality CVD Growth and Al<sub>2</sub>O<sub>3</sub> Encapsulation," *IEEE Electron Device Lett.*, vol. 38, no. 12, 2017.

- [27] T. Grasser, M. Waltl, K. Puschkarsky, B. Stampfer, G. Rzepa, G. Pobegen, H. Reisinger, H. Arimura, and B. Kaczer, "Implications of Gate-Sided Hydrogen Release for Post-Stress Degradation Build-up after BTI Stress," in *IEEE International Reliability Physics Symposium (IRPS)*, 2017, pp. 6A–2.

- [28] G. Rzepa, M. Waltl, W. Goes, B. Kaczer, J. Franco, T. Chiarella, N. Horiguchi, and T. Grasser, "Complete Extraction of Defect Bands Responsible for Instabilities in n and pFinFETs," in *IEEE Symposium* on VLSI Technology, 2016, pp. 208–209.