# Calibrated Nanoscale Dopant Profiling and Capacitance of a High-Voltage Lateral MOS Transistor at 20 GHz Using Scanning Microwave Microscopy

Enrico Brinciotti, Giorgio Badino, Martin Knaipp, Georg Gramse, Juergen Smoliner, and Ferry Kienberger

Abstract—We quantitatively image the doping concentration and the capacitance of a high-voltage lateral metal-oxidesemiconductor transistor device with a channel length of 0.5  $\mu$ m at 20-GHz frequency using scanning microwave microscopy (SMM). The transistor is embedded in a deep n-well forming a flat pnjunction with the p-substrate, with the shape of the pn-junction resolved in the SMM images. Calibrated dC/dV imaging of the device revealed doping concentration values in the range of 10<sup>15</sup>-1019 atoms/cm3, including the p-body, n-drift region, n-sourcediffusion, as well as all the pn-junctions and the silicon/oxide interfaces at a minimum feature size of 350 nm and SMM electrical resolution of 60 nm. SMM doping concentrations have been compared with technology computer-aided design simulations, resulting in a quantitative agreement between model and experiment. dC/dV images have been acquired at different tip dc bias voltages, allowing to determine the p and n dopant polarity. From the reflection scattering  $S_{11}$  signal calibrated capacitance measurements have been obtained from the various transistor regions in the range of 300 aF to 1 fF. The results suggest that both dC/dV dopant profiling and capacitance measurements can be used for quantitative nanoscale semiconductor device imaging.

*Index Terms*—Dopant profiling, microwave, nanoscale, scanning microwave microscopy, semiconductors.

#### I. INTRODUCTION

OPANT concentration is one of the most important parameters to properly determine and control the design, the functionalities, and the performance of solid-state electronic

Manuscript received December 12, 2016; accepted January 18, 2017. Date of publication January 25, 2017; date of current version March 8, 2017. This work was supported by EC-FP7PEOPLE-2012-ITN-317116 Nanomicrowave and Austrian FFG Nanospec 843594. The review of this paper was arranged by Associate Editor C. W. Liu.

- E. Brinciotti, G. Badino, and F. Kienberger are with the Keysight Labs, Keysight Technologies Austria GmbH, Linz 4020, Austria (e-mail: brinciottienrico@gmail.com; giorgio\_badino@keysight.com; ferry\_kienberger@keysight.com).

- M. Knaipp is with the Process Development, Austriamicrosystems, Unterpremstaetten 8141, Austria (e-mail: Martin.Knaipp@ams.com).

- G. Gramse is with the Biophysics Institute, Johannes Kepler University, Linz 4020, Austria (e-mail: georg.gramse@jku.at).

- J. Smoliner is with the Institute for Solid State Electronics, Technical University of Vienna, Vienna A-1040, Austria (e-mail: juergen.smoliner@tuwien.ac.at).

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TNANO.2017.2657888

devices. With the size of modern devices shrinking, dedicated characterization techniques have been developed to meet lateral resolution requirements while guaranteeing the necessary doping sensitivity and doping polarity specificity. Non-destructive probing of the region of interest within the device is also often requested. Scanning Microwave Microscopy (SMM) is a nondestructive technique that allows probing the doping concentration of surface and sub-surface localized features [1]-[9] with nanoscale lateral resolution. Moreover, its broadband 1-20 GHz operating range allows tuning the measuring frequency while giving access to both dielectric [10]-[13] and conductivity [14]–[17] properties including the presence of dopants [15], [18]–[20]. Unlike invasive imaging techniques such as Scanning Spreading Resistance Microscopy (SSRM), SMMexperiments can be performed with virtually no sample modification in an ambient environment using a standard atomic force microscope (AFM) and vector network analyzer (VNA). In SMM, the conductive AFM tip acts as nanoscale imaging and microwave probe, resulting in simultaneous topographic and electrical characterization of the sample under test. There are two main SMM operating modes: reflection  $S_{11}$  measurements for complex impedance and dC/dV imaging for doping profiling. dC/dV effectively measures the derivative of a semiconductor C-V curve with respect to the bias voltage at a fixed DC bias, whereas from  $S_{11}$  reflection measurements calibrated capacitance and resistance images of the sample under test can be obtained. In both cases the conductive AFM tip and the semiconductor form a metal-oxide-semiconductor (MOS) system. In SMM, the probing depth of a semiconductor sample is determined mainly by the skin depth, which depends on the measuring GHz frequency. Accordingly, by choosing a different working point within the 1-20 GHz frequency window one can vary the skin depth, and therefore the probing depth. On a n-type silicon substrate with doping levels ranging from  $4 \times 10^{15}$  atoms/cm<sup>3</sup> to  $1 \times 10^{20}$  atoms/cm<sup>3</sup>, the penetration depth would vary between 1.5 mm and 38  $\mu$ m at 1 GHz, and between 0.3 mm and 9  $\mu$ m at 20 GHz [18]. For a p-type silicon substrate typical values at 20 GHz range between 0.7 mm for low doping and 10  $\mu$ m for high doping concentrations.

SMM has been successfully employed to qualitatively characterize semiconductor structures used in different industrial

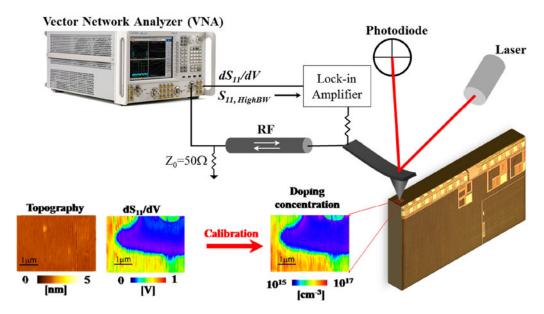

Fig. 1. (a) Scanning Microwave Microscopy (SMM) experimental setup allowing simultaneous acquisition of topography,  $S_{11}$  and dC/dV of the sample under test. Lower panel: calibration procedure for quantitative doping profiling of a cross-section transistor device. The dC/dV image scale is transferred to quantitative dopant values with a dopant calibration sample.

applications [22], [26], [31]-[34]. It was recently shown that the GHz operating frequency can be optimized to obtain a monotonic dependence of the dC/dV signal with the doping concentration [35]. Nevertheless, to the best of our knowledge, no work showing quantitative doping concentration as well as capacitance imaging of such semiconductor structures has been yet presented. Here, we demonstrate the capability of SMM to non-invasively and quantitatively probe the doping concentration and capacitance of a high-voltage (HV) lateral MOS transistor (LDMOS) device. The body of this lateral MOS transistor is formed by a diffusion step and therefore the well-known term of an HV LDMOS (lateral diffused) transistor is used. LDMOS devices, where the extension of the gate electrode works as a field-plate, are one of the most interesting structures in the mainstream HV technologies [21]. LDMOS transistors are widely used in telecommunication electronics, dc-dc converters, and mixed-signal circuit design as integrated high-voltage switches and drivers. To quantitatively extract the doping concentration along with the p and n dopant polarity within the device active region, a dopant calibration sample has been used and different DC tip-bias voltages are applied [22]. The SMM results have been compared with Technology Computer-Aided Design (TCAD) simulations, leading to a quantitative agreement between model and experiments.

# II. MATERIALS AND METHODS

# A. SMM Setup

A commercial transmission line SMM was used (Keysight Technologies, USA), consisting of a standard 5600 AFM interfaced with a 20 GHz VNA, along with 18 N/m solid platinum AFM tips (RMN, USA). The VNA measures the ratio of the incident and reflected signal at the tip/sample interface,

the so called scattering  $S_{11}$  parameter. The high tip-sample contact impedance is matched to the sensitive 50  $\Omega$  characteristic impedance of the VNA via a half-wavelength coaxial resonator in conjunction with a 50  $\Omega$  shunt resistor [23]. The half-wavelength resonator ensures high signal-to-noise ratio with good matching conditions every  $\sim 1$  GHz. Since the admittance Y scales linearly with the circular frequency  $\omega$  at a given capacitance C,  $Y \sim j\omega C$ , it is favorable for the Signal-to-Noise Ratio (SNR) to measure at high frequencies. Accordingly, all the measurements were performed in contact mode at 20 GHz. An intermediate frequency bandwidth (IFBW) of 500 Hz was used, leading to a scan speed of 0.8 line/s (256 points/line).

## B. dC/dV Imaging for Dopant Profiling

dC/dV imaging was performed connecting a dopant profiling measurement module (DPMM) to the four auxiliary inputs of the VNA. The operating principle is explained in details in [22]. Fig. 1 shows the measurement setup for dC/dV experiments. In addition to the GHz signal from the VNA, a kHz signal synthesized by the source of a lock-in amplifier is superimposed using a bias tee and sent to the tip. The sample depletion capacitance changes with the kHz signal, which modulates the reflected GHz signal. This modulation of the reflected signal is detected by the DPMM. A mixer converts the signal into the baseband at zero IF frequency. Subsequently the reflected signal passes through a low-pass filter, and is then sent to the lock-in amplifier operating at the modulation frequency. This final stage rectifies the signal and generates a DC output proportional to the modulation response of the capacitance. In our measurements the incident microwave power was set to -3 dBm (dBm meaning dB per mW input power, thus 0.5 mW), a modulation frequency of 15 kHz, and a modulation drive of 0.5 V were used.

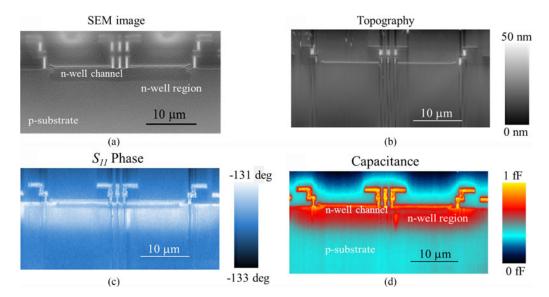

Fig. 2. Cross-section images of a transistor embedded in a deep n-well. The channel length is  $10 \mu m$ . Scanning Electron Microscopy (SEM) micrograph (a) and SMM (b-d) images. The SEM and the topography images reveal the different areas within the transistor: drift region and drain contact area (left), and source/body area (center). From the  $S_{11}$  phase image (c) the calibrated capacitance image (d) is obtained.

# C. Dopant Profiling Calibration

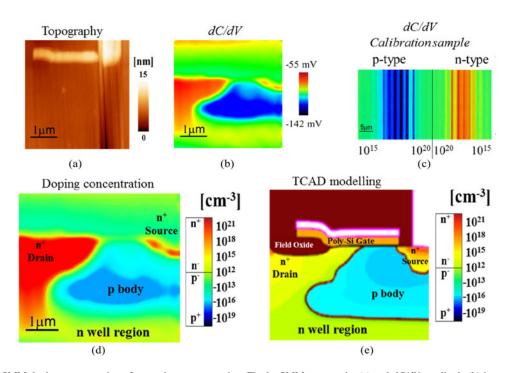

For quantitative dopant profiling with dC/dV, a wellestablished calibration workflow, described in details in [22], which effectively converts the dC/dV signal into doping concentration values, was used. First, a dC/dV amplitude image of a commercially available calibration sample (Infineon Technologies, Germany) [24], is acquired and a dopant calibration curve is generated from it. A flat silicon calibration sample produced by Infineon Munich (shown in Fig. 5(c)), that has both n-type and p-type polarity was used [18], [24]. It consists of a p-Si substrate (10<sup>15</sup> atoms/cm<sup>3</sup>) with 10 different p-type and 10 different n-type implant areas, with doping levels in the range  $4 \times 10^{15}$  –  $1 \times 10^{20}$  atoms/cm<sup>3</sup>. The n-doped and p-doped regions are next to each other and therefore can be imaged in one SMM scan. In a second step, the dC/dV amplitude image of the sample under test is acquired under the same SMM working conditions used in the first step for the calibration sample (i.e. VNA frequency, % drive voltage, DPMM kHz frequency). Using the dopant calibration curve, the dC/dV image of the sample is converted into a calibrated dopant concentration image.

## D. Complex Impedance Calibration

The measured  $S_{11}$  data were converted into capacitance using the calibration procedure established recently [12]. Thereby, a one-port black-box calibration [25] is employed to convert the measured  $S_{11}$  into complex impedance Z. For this, three complex error parameters  $e_{00}$ ,  $e_{01}$ , and  $e_{11}$  are provided via a simultaneous acquisition of  $S_{11}$  and Electrostatic Force Microscopy (EFM) dC/dz approach curves. The main advantage of this method is that it works in situ on the sample under test; therefore, no external capacitance calibration sample is required.

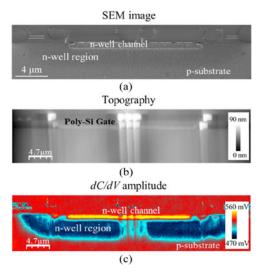

Fig. 3. SEM micrograph (a), SMM topography (b), and dC/dV amplitude (c) of the deep n-well region. The channel length is  $10~\mu m$ . The dC/dV contrast depends on the modulation of the depletion zone, and clearly reveals the n-well region as well as the channel. No contrast is obtained in the field oxide and poly-silicon gate regions.

## E. Cross-Section Transistor Sample

The cross-section transistor sample was designed and fabricated by austriamicrosystems (http://ams.com). A p-type silicon dice with several transistor devices has been cut to obtain a series of cross-section transistors having their active regions accessible with a scanning probe. After cut the sample is exposed to air and a  $\sim$ 1 nm thick native silicon dioxide passivation layer is spontaneously formed. This ensures the presence of the oxide layer and thus of a MOS system when scanning the sample with the SMM conductive probe. In general, SMM works also on non-stoichiometric oxide layers because of the

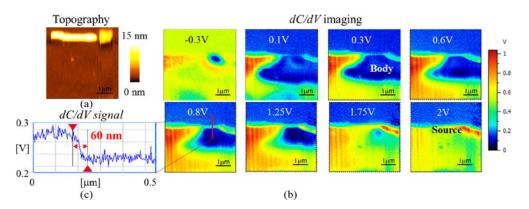

Fig. 4. SMM topography (a) and dC/dV phase images with cross-section (b, c) of a transistor cross-section at different DC tip bias voltages. The minimum channel length is 0.5  $\mu$ m. The topography shows the poly-silicon gate and the field oxide which are higher than the flat active area. The dC/dV images show no unspecific topographic cross-talk in the poly-silicon gate and the field oxide (uniform color at the top of each image). Within the flat active region, the dC/dV signal shows its sensitivity to the differently p- and n-type doped areas. The electrical lateral resolution is shown in the cross-section (c) of the dC/dV image at 0.8 V (red line).

Fig. 5. Calibrated SMM doping concentration of a transistor cross-section. Firstly, SMM topography (a) and dC/dV amplitude (b) images are obtained. Then, a dopant calibration sample having n-type and p-type regions is scanned acquiring a calibration dC/dV image (c) under the same operating conditions. The raw transistor image is then calibrated resulting in quantitative dopant concentrations (d). The scale bar (n-type in red and p-type in blue, respectively) shows the net-doping concentration – i.e. the difference between donors and acceptors - which defines the electrical conductivity in the considered region. (e) TCAD model of the same area.

GHz-capacitive coupling between tip and sample and the corresponding E-field penetration into the sample [22]. Fig. 1 shows a sketch of the sample, measured in cross-section. The device investigated is an n-channel LDMOS transistor implemented in a CMOS-based HV technology. The minimum feature size is 350 nm. Our study was performed on a 30  $\mu m \times 5~\mu m$  active region of a non-butted transistor device embedded in a deep n-well. In particular, a quantitative SMM study has been performed in a 4  $\mu m \times 4~\mu m$  area including poly-silicon gate, field oxide, p-body, n+-source, and n+-drain. The part under investigation is a lateral high voltage n-channel transistor with

a maximum operating voltage of  $V_{\rm DS}=20$  V. The maximum allowed gate voltage is  $V_{\rm GS}=5$  V. The body well is located in a deep n-well which isolates the body from the substrate. Because of the isolation, the body and source potential can be in between the source supply voltage  $V_{\rm SS}$  and the drain supply voltage  $V_{\rm DD}$ . The deep n-well potential is defined by the drain potential. To get the appropriate breakdown voltage the drift region below the field oxide has to be balanced with a remaining part of the body well. This results in the typical pn junction curvature shown in this work [see Fig. 4(b) & Fig. 5(e)].

# F. TCAD Modelling

For the TCAD setup the SYNOPSYS TCAD software was used. During simulation the option "advanced calibration" was activated. The simulation window was defined in a way to best reflect the drain/drift region and the body/source area of a transistor with a channel length of 0.5  $\mu m$ . It was assumed that the deep n-well doping profile shows a one-dimensional dopant distribution and that the deep n-well implant boundary is far away from the simulation window. In addition, the depth of the silicon was set to 20  $\mu m$  to account for the vertical diffusion of the deep n-well.

#### III. RESULTS AND DISCUSSION

# A. Calibrated Capacitance of Transistor

The high-voltage (HV) lateral MOS transistor device [SEM image in Fig. 2(a)] has been imaged in cross-section acquiring SMM topography and microwave  $S_{11}$  images [see Fig. 2(b) and (c). In the SEM micrograph, both the gate and the deep n-well of the device with a channel length of 10  $\mu$ m are visible. The SMM topography shows the poly-silicon gate structure that agrees in size and pattern with the SEM data. The microwave images show both gate and n-well regions, confirming the sensitivity of  $S_{11}$  to the doping distribution within the material. The  $S_{11}$ images have been calibrated [12] into a capacitance image of the transistor [see Fig. 2(d)]. As expected, the highest capacitance value, 1fF, is observed in the metal-like region of the poly-silicon gate. The deep n-well region and its pn junction interface with the p-type substrate are both resolved with roughly 300 aF contrast, with the capacitance being higher in the doped n-well region. Within the active region the capacitance increases with the doping concentration, showing the lowest values in the p-type silicon substrate. Finally, the capacitance image also reveals the n-channel that runs below the field-oxide and polysilicon gate at 600 aF [see Fig. 2(d)].

# B. dC/dV Imaging of the n-Well Region

dC/dV imaging has been performed on the n-channel LD-MOS transistor in CMOS HV technology. Fig. 3 shows a SEM micrograph, topography, and dC/dV amplitude of the device. The SEM image has been acquired after dipping the device in acid, causing the onset of the small granular structures within the n-well region. The topography and the SEM micrograph show an agreement in the overall dimensions. The dC/dV image clearly reveals the differently doped regions within the device's active region, including the deep-n-well, the n-channel, and the flat pn junction formed at the p-substrate/n-well interface. No contrast is obtained in the field oxide and poly-silicon gate top region. This is expected, because the technique is sensitive specifically to voltage induced modulations occurring within the depletion zone underneath the sample surface.

# C. DC Tip Bias Manipulation of Charge Carriers

dC/dV imaging resolves the doped regions within the transistor, and further investigations of the doping depletion zone can

be done by adding a DC tip bias voltage to the SMM tip. Depending on the sign of the applied bias voltage to the AFM tip, the charge carriers in the semiconductor are attracted or depleted from the surface forming a space charge region. The width of the space charge region in the semiconductor varies with the tip bias affecting the capacitance of the MOS junction. For a given tip bias, the width of the space charge region is also a function of the charge carrier density in the semiconductor, which corresponds to the concentration of impurity donor or acceptor atoms, i.e. the dopant concentration. Measuring the differential capacitance dC/dV of the tip-sample interface and its variation with an applied DC tip-sample bias is therefore an important extension for the electrical characterization of semiconductors. As such, the local charge carriers are modulated by the DC voltage bias, and the dC/dV signal is used to simultaneously read-out the effects on the depletion zone. Fig. 4 shows dC/dV images at different tip-bias voltages on a transistor with a channel length of 0.5  $\mu$ m, resolved with an electrical lateral resolution of 60 nm [see Fig. 4(c)]. The topography image shows the poly-silicon gate and the field oxide, with a flat active region that includes the charge carriers. Fig. 4 shows that, at appropriate bias, the dC/dV images are almost exclusively sensitive either to electrons (n-type areas) or holes (p-type areas). The dC/dV images are shown at steps from -0.3 V up to 2 V tip bias. From the images we see how the doped regions within the active region react differently to the voltage bias, depending on their p or n dopant polarity. When the bias voltage is increased to larger positive voltages, the p-body (blue region) gets depleted and shrinks with almost no contrast at 1.75 V and 2 V anymore. The n+-source (red region on the right side) follows an opposite behavior with respect to the applied bias, and the signal can be observed only at 1.75 V and 2 V. Such a tip voltage induced migration of charge carriers has been also investigated in previous SMM studies and is in line with standard MOS semiconductor theory [26]–[29]. Depending on the dopant polarity and bias voltage, the charge carriers are either accumulated, partially depleted or completely depleted from the surface (inversion). The DC tip bias changes the width and the capacitance of the space charge region, affecting the dC/dV signal. The highest dC/dV signal can be measured in depletion, where the kHz signal can most effectively modulate the space charge capacitance. At small voltages (accumulation), holes from the p silicon are attracted to the surface, shrinking the width of the space charge region. Accordingly, the p-doped body shows the strongest dC/dV signal at 0.1–0.6 V. For strongly positive tip bias voltages, the holes are depleted from the surface and the width of the space charge region increases (inversion), resulting in a decreased dC/dV signal of the p-body at 1.75–2 V. The same mechanism, with opposite voltage dependence, holds for the n-type regions. The n+-type source shows the strongest dC/dV signal at 1.75–2 V because the free electrons accumulate closely to the surface, reducing the width of the space charge region. We observed a slight shift of the space charge region dynamics towards positive voltage values, mostly because of two contributions. Firstly, the work-function of the solid platinum tip influences the working voltage; secondly, the presence of oxide and surface charges influences the voltage dependence of the depletion capacitance [30]. This tip bias voltage dependence

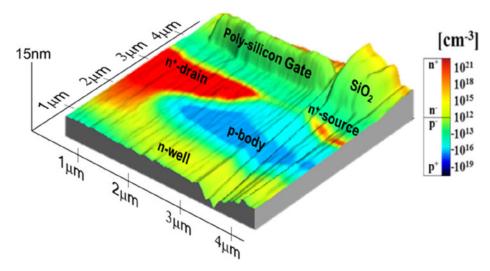

Fig. 6. 3D SMM dopant image obtained by combining the topography with the calibrated doping concentration of the transistor device. The superimposition allows having all the information in one image, highlighting both the differently doped p-type and n-type regions within the device and the topographical pattern.

of the space charge region's width and of the charge carriers is typically used to differentiate n-doped from p-doped areas in quantitative SMM imaging.

# D. Quantitative Dopant Profiling

The dC/dV raw data were calibrated using a dopant profiling calibration sample (cf. Materials and Methods, [22]). A flat calibration sample with differently doped regions has been used [18], [24]. Fig. 5 shows the raw dC/dV image of the transistor and the raw image of the calibration sample, including both n-type and p-type regions with doping concentration in the range of  $10^{15}$ – $10^{20}$  atoms/cm<sup>3</sup>. Again, the transistor image shows the n-channel LDMOS including the p-body, n+ source, n+ drain, poly-silicon gate, and field oxide regions. From the dC/dV calibration image, two calibration curves relating the pand n-doping concentrations to the measured dC/dV values are derived. Using the calibration curves, the dC/dV image of the transistor has been converted into a 2D color map of the doping concentration [see Fig. 5(d)]. Note that the color-bar includes both p-type and n-type doping concentration values. What is shown in Fig. 5(d) is the numerical sum of the local (negative) electrons concentration and the local (positive) holes concentration. The information on the individual carrier concentration in the transition region between the n- and p-type areas is still available in the original SMM p-type and n-type carrier maps of the device, measured at the corresponding tip-bias voltages. The SMM doping concentration values have been compared to a TCAD model that was specifically defined to reflect the drain/drift region and the body/source area of the transistor with a channel length of 0.5  $\mu$ m. Fig. 5(e) shows the modelling results in the area of interest, thus the p- substrate located below the deep n-well is not included. A quantitative agreement between model and experiments has been obtained on most of the transistor regions within the SMM accuracy of 20% for doping profiling [22]. The only area that shows a larger difference is the n-drain, where the doping concentration values measured

with SMM are higher than the modelled ones. This can be attributed to the presence of trapped charges in the native oxide and surface charges, which alter the measured dC/dV signal and thus the doping concentration values. Fig. 6 shows a superposition of the topography image with the doping concentration 2D color-map. The superimposition helps locating the active doped regions within the device by showing their positions with respect to the topographical features such as the poly-silicon gate. Moreover, it shows that the calibrated doping concentration image generated from the dC/dV image has no unspecific crosstalk influence from the topography.

## IV. CONCLUSIONS

The 2D doping concentration map of a n-channel LDMOS transistor in CMOS HV technology has been obtained at 20 GHz frequency using dC/dV SMM. Key device features such as n-source, p-body, and n-drain with a minimum feature size of 350 nm have been resolved and quantitatively measured with an electrical SMM lateral resolution of 60 nm. This suggests that SMM's electrical sensitivity and lateral resolution can be exploited to characterize nanoscale features within real electronic devices. The calibrated SMM doping images showed values of 10<sup>15</sup> to 10<sup>19</sup> atoms/cm<sup>3</sup>, and they have been compared with the doping concentration map from TCAD simulations. The dC/dV experiments revealed the shape of the pn junction formed at the p-body/n-well interface, which is in accordance to TCAD modelling. dC/dV experiments at different DC tip bias allow further characterization of the differently doped regions including the p-body and n-source. As such the doping polarity can be investigated on top of quantitative doping concentrations. From  $S_{11}$ measurements, a calibrated capacitance image of the transistor device has been obtained. The capacitance of the poly-silicon gate, n-well, and the flat diffused pn junction formed at the p-substrate/n-well interface has been quantified with values in the range of 300 aF to 1fF. Our results suggest that both doping profiling and calibrated capacitance imaging capabilities

of SMM should be leveraged for a comprehensive electrical nanoscale analysis of a semiconductor structure.

#### ACKNOWLEDGMENT

We would like to thank Silviu-Sorin Tuca from Johannes Kepler University of Linz and Manuel Kasper from Keysight Technologies Austria for the fruitful technical discussions.

#### REFERENCES

- M. Anlage S. et al., Principles of near-field microwave microscopy. Scanning Probe Microscopy: Electrical and Electromechanical Phenomena at the Nanoscale, vol. 1, S. V. Kalinin and A. Gruverman, Eds. New York, NY, USA: Springer-Verlag, 2007, pp. 215–53.

- [2] V. V. Talanov and A. R. Schwartz, "Near-field scanning microwave microscope for interline capacitance characterization of nanoelectronics interconnect," *IEEE Trans. Microw. Theory Techn.*, vol. 57, no. 5, pp. 1224–1229, May 2009.

- [3] M. Farina, D. Mencarelli, A. Di Donato, G. Venanzoni, and A. Morini, "Calibration protocol for broadband near-field microwave microscopy," *IEEE Trans. Microw. Theory Techn.*, vol. 59, no. 10, pp. 2769–2776, Oct. 2011.

- [4] A. Gregory *et al.*, "Spatially resolved electrical characterisation of graphene layers by an evanescent field microwave microscope," *Physica* E, vol. 56, pp. 431–434, 2012.

- [5] P. Vlahacos C. et al., "Near-field scanning microwave microscope with 100 μm resolution," Appl. Phys. Lett., vol. 69, pp. 3272–3274, 1996.

- [6] A. Tselev et al., "Near-field microwave scanning probe imaging of conductivity inhomogeneities in CVD graphene," *Nanotechnology*, vol. 23, 2012, Art. no. 385706.

- [7] M. C. Biagi et al., "Nanoscale electric permittivity of single bacterial cells at gigahertz frequencies by scanning microwave microscopy," ACS Nano, vol. 10, no. 1, pp. 280–288, 2016.

- [8] Y. Ma E. *et al.*, "Mobile metallic domain walls in an all-in-all-out magnetic insulator," *Science*, vol. 350, no. 6260, pp. 538–541, 2015.

- [9] C. Gao et al., "High spatial resolution quantitative microwave impedance microscopy by a scanning tip microwave near-field microscope," Appl. Phys. Lett., vol. 71, pp. 1872–1874, 1997.

- [10] J. Hoffmann et al., "Measuring low loss dielectric substrates with scanning probe microscopes," Appl. Phys. Lett., vol. 105, 2014, Art. no. 013102.

- [11] K. Lai et al., "Calibration of shielded microwave probes using bulk dielectrics," Appl. Phys. Lett., vol. 93, 2008, Art. no. 123105, doi: 10.1063/1.2990638.

- [12] G. Gramse et al., "Calibrated complex impedance and permittivity measurements with scanning microwave microscopy," *Nanotechnology*, vol. 25, 2014, Art. no. no. 145703.

- [13] C. Gao and X. D. Xiang, "Quantitative microwave near-field microscopy of dielectric properties," *Rev. Sci. Instrum.*, vol. 69, pp. 3846–3851, 1998, doi:10.1063/1.1149189.

- [14] S. Berweger *et al.*, "Microwave near-field imaging of two-dimensional semiconductors," *Nano Lett.*, vol. 15, pp. 1122–1127, 2015.

- [15] A. Imtiaz, T. M. Wallis, and P. Kabos, "Near-field scanning microwave microscopy," *IEEE Microw. Mag.*, vol. 15, no. 1, pp. 52–64, Jan./Feb. 2014.

- [16] W. Kundhikanjana et al., "Hierarchy of electronic properties of chemically derived and pristine graphene probed by microwave imaging," Nano Lett., vol. 9, pp. 3762–3765, 2009.

- [17] K. Lai et al., "Nanoscale electronic inhomogeneity in In2Se3 nanoribbons revealed by microwave impedance microscopy," Nano Lett., vol. 9, pp. 1265–1269, 2009.

- [18] E. Brinciotti et al., "Probing resistivity and doping concentration of semiconductors at the nanoscale using scanning microwave microscopy," Nanoscale, vol. 7, pp. 14715–14722, 2015.

- [19] A. Imtiaz et al., "Frequency-selective contrast on variably doped p-type silicon with a scanning microwave microscope," J. Appl. Phys., vol. 111, 2012, Art. no. 093727.

- [20] K. Lai et al., "Modeling and characterization of a cantilever-based near-field scanning microwave impedance microscope," Rev. Sci. Instrum., vol. 79, 2008, Art. no. 063703.

- [21] M. Knaipp, G. Rohrer, R. Minixhofer, and E. Seebacher, "Investigations on the high current behavior of lateral diffused high-voltage transistors," *IEEE Trans. Electron. Devices*, vol. 51, no. 10, pp. 1711–1719, Oct. 2004.

- [22] H. P. Huber et al., "Calibrated nanoscale dopant profiling using a scanning microwave microscope," J. Appl. Phys., vol. 111, 2012, Art. no. 014301.

- [23] H. Happy et al., "Measurement Techniques for RF Nanoelectronic Devices: New Equipment to Overcome the Problems of Impedance and Scale Mismatch," IEEE Microw. Mag., vol. 1527–3342, pp. 30–39, 2014.

- [24] T. Schweinbock and S. Hommel, "Quantitative scanning microwave microscopy: A calibration flow," in *Microelectronics Reliability*, vol. 54, no. 910, 2014, pp. 2070–2074.

- [25] J. Hoffmann, M. Wollensack, M. Zeier, J. Niegemann, H.-P. Huber, and F. Kienberger, "A calibration algorithm for nearfield scanning microwave microscopes," in *Proc. 12th IEEE Conf. Nanotechnol.*, 2012, pp. 1–4.

- [26] J. Smoliner et al., "Scanning microwave microscopy/spectroscopy on metal-oxide-semiconductor systems," J. Appl. Phys., vol. 108, pp. 0643151–0643157, 2010.

- [27] L. Michalas et al., "Modeling and de-embedding the interferometric scanning microwave microscopy by means of dopant profile calibration," Appl. Phys. Lett., vol. 107, 2015, Art. no. 223102.

- [28] H. P. Huber et al., "Calibrated nanoscale capacitance measurements using a scanning microwave microscope," Rev. Sci. Instrum., vol. 81, 2010, Art. no. 113701.

- [29] H. Bentarzi, Transport in Metal-Oxide-Semiconductor Structures. Berlin, Germany: Springer-Verlag, 2011.

- [30] J. Smoliner et al., "Mechanism of bias-dependent contrast in scanning-capacitance-microscopy images," Appl. Phys. Lett., vol. 79, no. 19, 2001, Art. no. 3182.

- [31] S. Hommel et al., "Scanning microwave microscopy for electronic device analysis on nanometre scale," *Microelectron. Rel.*, vol. 64, pp. 310–312, 2016.

- [32] L. Michalas et al., "Scanning microwave microscopy for non-destructive characterization of SOI wafers," in Proc. IEEE Joint Int. EUROSOI Workshop Int. Conf. Ultimate Integr. Silicon, Vienna, 2016, pp. 238–241.

- [33] S. Friedman *et al.*, "Characterizing non-linear microwave behavior of semiconductor materials with Scanning Microwave Impedance Microscopy," in 2016 IEEE MTT-S Int. Microw. Symp., May 22–27, 2016, pp. 1–3.

- [34] G. Gramse and E. Brinciotti et al., "Quantitative sub-surface and non-contact imaging using scanning microwave microscopy," Nanotechnology, vol. 26, 2015, Art. no. 135701.

- [35] E. Brinciotti et al., "Frequency analysis of dopant profiling and capacitance spectroscopy using SMM," *IEEE Trans. Nanotechnol.*, vol. 16, no. 1, pp. 75–82, Jan. 2017.

Enrico Brinciotti received the B.Eng. degree in biomedical engineering and the M.Eng. degree in nanotechnology engineering from Sapienza University of Rome, Rome, Italy, and the Ph.D. degree in physics from the Johannes Kepler University Linz, Linz, Austria, in 2016. He is currently an R&D Engineer with Keysight Technologies. He joined Agilent Technologies in 2013 and from Nov. 2014, he is a member of the central research laboratory of Keysight Technologies. His current research focus is on high-frequency characterization of materi-

als at the nanoscale, with a particular focus on semiconductors and thin-films applications.

Giorgio Badino received the Master's degree in bionengineering and Bachelor's degree in biomedical engineering both from the University of Genova, Genoa, Italy. In 2014, he joined Keysight Technologies, Linz, Austria as an R&D Engineer. His research interest includes materials characterization and microwave interaction mechanisms at the nanoscale.

Martin Knaipp received the M.Sc. degree in physics from the Technical University of Vienna, Vienna, Austria, in 1994, and the Ph.D. degree from the Institute for Microelectronics, Vienna, for his work on temperature modeling of semiconductor devices, in 1998. In 1998, he joined the Research and Development Group at austriamicrosystems, Unterpremstaetten, Austria. The topic of his work was process and device simulation using TCAD tools. He is currently working in HV development, and he is the Technical Project Leader of submicrometer HV process development.

Juergen Smoliner received the Degree in physics and the Ph.D. degree both from the University of Innsbruck, Innsbruck, Austria. From 1988 to 1993, he was with the Technical Institute "Walter Schottky," University of Munich, Germany. In 1993, he joined the Institut für Festkörperelektronik, TU-Wien, Austria, where he is currently a University Professor. His current research interest includes solid-state physics and nanoelectronics, with a particular focus on scanning probe microscopy methodologies.

Georg Gramse received the Ph.D. degree in nanoscience from the Institute Bioengineering of Catalonia, Barcelona, Spain, and the Master of Science degree in nanotechnology and physics from Freie University of Berlin, Berlin, Germany. He is a Postdoctoral Researcher at the Johannes Kepler University Linz, Linz, Austria. His research area is nanotechnology focusing on scanning probe microscopy for electrical characterization at low and high frequencyand applications are in the field of biophysics and material science.

Ferry Kienberger received the Ph.D. degree in technical physics in 2002 with subsequent Postdoctoral stays in bioinformatics and biophysics. He is currently the SMM group leader at Keysight Laboratories Linz, Linz, Austria. In 2007, he joined the research lab of Agilent Technologies. The work included topics on nanobiotechnology and measurement electronics including high-frequency microwave applications. Since 2014, he has been a member of the Central Research Laboratory of Keysight Technologies and the Head of the Keysight

Research Laboratory, Linz. Keysight is a leading test and measurements company headquartered in Santa Rosa, CA, USA, with more than 10 000 employees.