# Impact of Mixed Negative Bias Temperature Instability and Hot Carrier Stress on MOSFET Characteristics—Part II: Theory

Markus Jech<sup>®</sup>, Bianka Ullmann, Gerhard Rzepa, Stanislav Tyaginov, Alexander Grill, Michael Waltl<sup>®</sup>, Dominic Jabs<sup>®</sup>, Christoph Jungemann, *Senior Member, IEEE*, and Tibor Grasser, *Fellow, IEEE*

Abstract—In this paper, we examine the interplay of two serious reliability issues in MOSFET devices, namely, bias temperature instability (BTI) and hot-carrier degradation (HCD). Most publications are devoted to the characterization of either BTI or HCD, and complex models have been developed to independently describe each degradation mode. However, very limited data are available on the interplay of both degradation regimes, particularly the effect of a drain bias onto the charging and discharging dynamics of oxide traps. Part I of this paper provides an extensive experimental study toward the impact of mixed-mode stress conditions on the dynamics of oxide defects. Here, we present the first microscopic modeling approach beyond a simple electrostatic approximation. We extend the existing nonradiative multiphonon theory by taking nonequilibrium processes such as full carrier distribution functions which include the effect impact ionization along the channel into account. To ultimately validate our framework, we compare simulation results and experimental data for a single-oxide defect as well as a large ensemble of traps in a MOSFET device. We show that our modeling approach accurately captures the rather puzzling measurement trends for a broad stress regime and allows developing the knowledge on how oxide defects can be affected by an increased drain stress.

Index Terms—Bias temperature instability (BTI), defect modeling, device simulation, hot-carrier degradation, mixed-mode stress, reliability, single-oxide defects.

Manuscript received May 25, 2018; revised July 31, 2018; accepted August 13, 2018. Date of publication November 8, 2018; date of current version December 24, 2018. The work was supported in part by Austrian Science Fund (FWF) under Project P 26382-N30, Project P 23958-N24, and Project I2606-N30, in part by Austrian Research Promotion Agency (FFG) under Project 861022, and in part by the European Union's Horizon 2020 Research and Innovation Programme under the Marie Sklodowska-Curie grant agreement No. 794950. The review of this paper was arranged by Editor C. Monzio Compagnoni. (Corresponding author: Markus Jech.)

- M. Jech, B. Ullmann, G. Rzepa, A. Grill, M. Waltl, and T. Grasser are with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria (e-mail: jech@iue.tuwien.ac.at).

- S. Tyaginov is with the Institute for Microelectronics, Technische Universität Wien, 1040 Vienna, Austria, also with the loffe Physical-Technical Institute, Russian Academy of Sciences, 194021 Saint Petersburg, Russia, and also with IMEC, Kapeldreef 75, 3001 Leuven, Belgium.

- D. Jabs and C. Jungemann are with the Institut für Theoretische Elektrotechnik, RWTH Aachen, 52072 Aachen, Germany.

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2018.2873421

### I. INTRODUCTION

ODERN CMOS technologies face two major reliability issues, bias temperature instability (BTI) and hot-carrier degradation (HCD) [1], [2]. The vast majority of publications concerning reliability topics is focused on the independent experimental characterization of either BTI or HCD as well as the development of models for each individual degradation mode [3]–[8]. BTI, on the one hand, in particular, its recoverable component, is related to oxide defects and charge trapping in the gate stack. Nonradiative multiphonon (NMP) theory [9], [10], specifically the four-state NMP model [4], provides a physical framework to accurately describe this phenomenon and has been successfully applied to model BTI recovery across various technologies [11]–[13].

On the other hand, HCD is more permanent and assumed to be driven by the generation of interface traps due to the dissociation of Si–H bonds at or near the Si/SiO<sub>2</sub> interface [14]–[17]. The most recent formulation of an HCD model by Tyaginov *et. al.* [18], [19] links microscopic quantities, such as the nonequilibrium energy distribution function (EDF) of carriers, to the trap density at the interface. Special attention is paid to the EDF, obtained as a solution of the Boltzmann transport equation (BTE), which is a key ingredient of the model and determines the rate of interaction of energetic charge carriers and the Si–H bond.

Both individual degradation phenomena are reasonably well understood and rather intricate models have been published, which are able to capture the characteristics of each mode. However, only a handful of publications are devoted to the interplay of both mechanisms, and in particular, the implications of an applied drain bias on the recoverable component of BTI [20]–[27]. Experimental studies show that with increased drain bias, the recoverable component, typically attributed to BTI, decreases [20], [22], [23]. At the best, a simple electrostatic approximation is used to model this behavior, where the reduction of the electric field across the interface for an applied  $V_D$  is taken into account [21]. This assumption, however, implies that source-sided defects would be rather independent of an applied  $V_D$ . Quite contrary to this, we have shown in Part I [28] of this paper as well as in a recent publication [22] that even defects located in the vicinity of the source can be heavily affected by a drain bias.

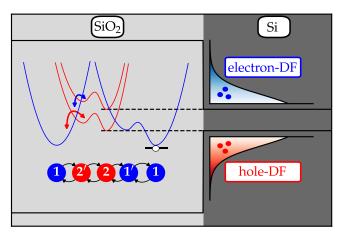

Fig. 1. Schematic of the possible interactions of a defect with the channel within the four-state NMP theory. In the full physical picture, the oxide defect can interact with VB and CB carriers of the channel.

In this paper, we present a first modeling approach to accurately describe the complex behavior of oxide defects for increased drain bias stress. We extend the physical framework of the four-state NMP theory [4] toward nonequilibrium processes by explicitly taking nonequilibrium EDFs for electrons and holes into account. To validate our model, we compare the simulation results and experimentally recorded characteristics for single-oxide defects for various  $V_G$ and  $V_D$  stress conditions. Throughout this paper, we used two different realizations of 2.2-nm SiON pMOSFETs of a 130-nm commercial technology. The nanoscale devices used in Section III have a metallic gate length and width of L=120and W = 160 nm, respectively. The large area devices, on the other hand, have the same gate length but a width of  $W = 10 \mu m$ . The simulations are able to fully explain the rather intricate defect behavior for increased  $V_D$  stress. Finally, we apply this approach to a large ensemble of oxide traps to understand the reduction of the recoverable BTI component with increased mixed-mode stress in MOSFET devices.

## II. EXTENDED NONRADIATIVE MULTIPHONON MODEL

The NMP four-state model, primarily developed to describe the dynamics of charging and discharging of oxide defects, is based on four different atomistic defect states. It comprises a neutral state 1 and a positively charged state 2, and for each of these charge states, an additional metastable configuration Fig. 1. Transitions between these states can be split into two distinct types: structural reconfigurations of the defects are pure thermal transitions modeled using an Arrhenius equation. According to transition state theory, charge exchange events between oxide defects and the semiconductor, on the other hand, are formulated as NMP transitions, including charge carriers in the valence band (VB) and conduction band (CB) Fig. 1. Generally, the total NMP rates for the VB and CB can be written as

$$k_{i,j}^{V,(C)} = \int_{-\infty,(E_C)}^{E_V,(\infty)} D_{p,(n)}(E) f_{p,(n)}(E) A_{i,j}(E, E_T) f_{i,j}(E, E_T) dE$$

with the density of states of the VB  $(D_p)$  and CB  $(D_n)$  and the carrier distribution function for holes  $(f_p)$  and electrons  $(f_n)$ . Furthermore,  $A_{i,j}$  accounts for tunneling processes and is approximated by a Wentzel-Kramer-Brillouin factor and  $f_{i,j}$  is the so-called line shape function and can be seen as a thermally broadened switching trap level. It is calculated by forming the thermal average of the overlaps between the eigenstates of the potential energy surfaces describing states iand j. Usually, the largest contributions arise from the energy levels close to their intersection point. The key quantity which enters both models for BTI and HCD is the carrier EDF,  $f_{p,n}(E)$ . However, during pure BTI conditions, only a gate stress voltage is applied as opposed to the HCD regime, where a high gate and drain bias is applied. Thus, for BTI carriers are in equilibrium and properly described by a Fermi-Dirac distribution, while for HCD, this assumption is not valid anymore. To access the full spectrum of how carriers are shifted from equilibrium and distributed over energy, a selfconsistent solution of the coupled BTE for holes and electrons is mandatory [29], [30].

To illustrate the necessity to consider nonequilibrium processes and highlight the difference in the simulation results, we use two variants of the NMP model described earlier in our TCAD simulations: a *quasi*-equilibrium model that approximates the EDFs for mixed-mode simulations by Fermi–Dirac distributions, termed NMP<sub>eq</sub>.

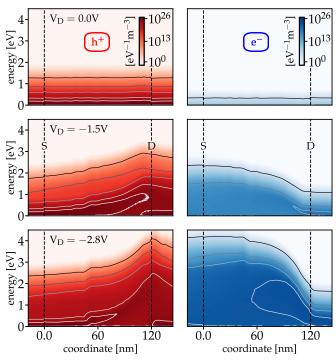

The second variant, termed NMPneq. includes distribution functions for holes and electrons evaluated with the higher order spherical harmonics expansion simulator SPRING [31], [32]. Thereby, the bipolar BTE was solved self-consistently including phonon and impurity scattering mechanisms as well as impact ionization with secondary carrier generation. As an example, EDFs for  $V_G = -1.5 \text{ V}$ and  $V_D = 0.0/-1.5/-2.8$  V are summarized in Fig. 2. Apparently visible is that nonequilibrium processes such as impact ionization affect not only the drain end of the channel but also the carrier energy distribution at the source side (see Fig. 2, electron EDF for high  $V_D$ ). While high energetic majority carriers typically are accumulated at the drain end of the channel—a characteristic well known in modeling of HCD—while electron EDFs become more pronounced in the channel and source regions. Although the holes II-rate is smaller compared to the electron rate in silicon, the results show a substantial contribution of secondary generated electrons for higher  $V_D$  bias [see Fig. 2 (bottom), EDF for holes and electrons].

The NMP<sub>eq.</sub> model is quite similar to the electrostatic model introduced in [21]. It accounts for the changes of macroscopic device quantities such as the electric field and the carrier concentration across the interface. With increased drain bias, the inversion layer across the interface is no longer uniform, particularly on the drain side where a pinchoff region is formed.

Using the NMP<sub>eq.</sub> model has therefore two implications: the charging and discharging dynamics of defects in the oxide are mainly determined by the interaction with carriers in the VB, also in the HCD stress regime where carriers potentially have enough energy to trigger impact ionization and, thus,

Fig. 2. Distribution functions for various stress regimes obtained from a solution of the bipolar BTE coupled via impact ionization. Hole EDFs (left). EDFs for the secondary generated electrons (right). A substantial contribution of secondary-generated carriers is visible for increasing stress conditions, particularly in the channel and source region.

create secondary carriers. Furthermore, the source side of the channel is rather unaffected even by a very high  $V_D$ . Hence, the simulated characteristics of oxide defects located in this region does not change with increasing  $V_D$ .

However, this is in stark contrast to our recent experimental studies presented in [22] and in Part I of this paper [28], where we have shown that defects, irrespective of their spatial location, do change their characteristics for various stress regimes. To access this rather intricate behavior in our simulations, we use our nonequilibrium model NMP<sub>neq.</sub> by using nonequilibrium EDFs for holes and electrons within (1). The interaction of high energetic carrier in the VB as well as the interplay of defects with the secondary generated electrons in the CB are shown to be the missing aspect to explain the puzzling results shown in Part I of this paper.

In the following sections, we apply both variants of the model to explain the behavior of a single-oxide defect and a large ensemble of traps for different stress regimes. We show a detailed analysis of the charging and discharging dynamics to finally unravel the experimentally recorded characteristics.

### III. SINGLE-TRAP CHARACTERISTICS

For the study of individual oxide defects, we characterized nanoscale 2.2-nm SiON pMOSFETs of a 130-nm commercial technology with  $W=160\,$  nm and a gate length of  $L=120\,$  nm. All experimental details, such as stress and recovery sequences, can be found in Part I of this paper. We chose the defect BI for our simulation study, since we could fully characterize this particular defect for a very broad range of stress conditions.

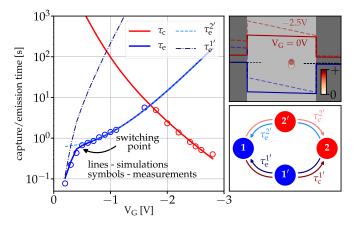

Fig. 3. Switching trap behavior of B1 for increased  $V_{\rm G}$  bias stress. Circles: measurement data. Solid lines: simulation results. Effect of an increased electric field  $E_{\rm OX}$  (right) upon the trap level (top), as well as the different capture and emission pathways which cause the switching behavior.

The basis of our study provides the behavior of the trap for pure BTI conditions. By applying the NMPeq. model and optimizing the parameter set, we are able to represent the experimentally recorded characteristic capture and emission times of B1 Fig. 3. As shown in the figure, the defect shows a switching trap behavior [3], [4], [33] for pure BTI stress conditions: the emission time shows a strong bias dependence below  $V_{\rm th} \sim -0.5$  V. With increasing  $V_G$  stress, the trap level shifts accordingly and the discharging pathway changes from the preferred path  $2 \to 1' \to 1$  at low  $V_G$  to  $2 \to 2' \to 1$  at higher  $V_G$  [see Fig. 3 (bottom right)]. The effective emission times for each individual discharging pathway, also called the first passage time  $\tau_e^i$  (see Section III), are as well indicated in Fig. 3. Furthermore, the time constants are mainly governed by transitions between the VB and the oxide trap due to the low concentration of carriers in the CB for the given stress voltages.

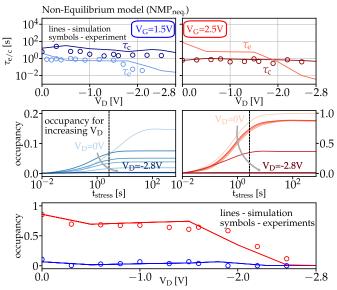

Interestingly, the behavior of B1 changes in a rather unexpected and complex way with increased drain bias, as already shown in Part I (see Figs. 4 and 5). Stressing the device with  $V_G = -1.5$  V and  $V_G = -2.5$  V for a broad range of drain biases,  $V_D = [0.0 \text{ V}, -2.8 \text{ V}]$ , reveals intricate and puzzling defect behavior. With higher drain bias the characteristic capture time of the defect—the time it needs to charge the defect—either stays constant or slightly decreases. However, at the same time, the defect's occupancy decreases dramatically. The most feasible explanation would be an even faster decreasing emission time. Thus, the defect would partially have already emitted its charge before the measurement setup switched to recovery conditions. Separate measurements actually reveal the proposed trend and support this idea. Unfortunately, only a limited number of experimental traces are available due to the difficulties of uniquely identifying the defect for high  $V_G$  and  $V_D$  bias conditions.

To understand and explain the measured behavior in detail, we apply both variants of the NMP model described in the previous section. Naturally, for all subsequent simulation, a unique parameter set was used, extracted from the simulations described in Fig. 3. The only free parameter left is the

Fig. 4. Experimental characterization of B1 for increasing  $V_D$  bias versus simulation results obtained with the NMPeq. model. Capture and emission times (top) for  $V_G=-1.5$  V (blue) and  $V_G=-2.5$  V (red). The simulated occupancy for different stress times  $t_{\rm stress}$  (middle) as well as the resulting occupancy at  $t_{\rm stress}=2$  s compared to experimental data (bottom). As can be seen, the NMPeq. model fails to describe the behavior of the defect B1.

lateral position of the trap. According to Part I, we set the position to the experimentally extracted 80 nm and allowed for a change of  $\pm 20\%$  in our simulations, corresponding to the experimental uncertainty.

First, we apply the NMP<sub>eq.</sub> model. Quite as expected, both characteristic trap parameters, the capture and emission time, increase for higher  $V_D$  bias due to the reduced oxide field  $E_{\rm OX}$  Fig. 4. The extracted occupancy of the defect for a stress time of  $t_{\text{stress}} = 2$  s—a cut along the dashed line in Fig. 4 (middle)—shows a similar decreasing trend for increasing  $V_D$  as the measurements Fig. 4. However, for  $V_G = -2.5$  V, the plateau visible in the measured data is not properly represented and, furthermore, the simulation results tend to saturate at a much higher occupancy compared to the experimental data. Even worse,  $\tau_e$  as well as  $\tau_c$  show contrary trends as the measured data. However, this is not a surprising result since in the NMP<sub>eq.</sub> model the carrier concentrations in the VB and CB as well as the EDFs stay approximately the same compared to the pure BTI regime. Thus, the determining factor is the electric field in the oxide,  $E_{OX}$ , just like the simple electrostatic model.

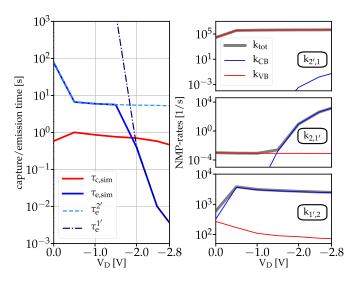

Next, we applied our nonequilibrium NMP<sub>neq.</sub> model. As shown in Fig. 5, all relevant characteristics are well represented by the model. The capture time  $\tau_c$  for both  $V_G$  conditions stays approximately constant while the emission time  $\tau_e$  of the defect dramatically decreases with  $V_D$ . This behavior translates into a very good agreement with the measured occupancy of B1 [see Fig. 5 (middle and bottom)]. Particularly specific features, such as rather constant occupancy between  $V_D = -0.5$  and -1.5 V followed by a rapid decrease properly captured, and will be discussed in the following. A detailed analysis of the capture and emission pathways reveals the nature of this interesting behavior (see Fig. 6): while the path

Fig. 5. Experimental characterization of B1 for increasing  $V_D$  bias versus simulation results obtained with the NMP<sub>neq.</sub> model. The extended model is able to capture the rather complex experimental trends and properly describes all characteristic quantities of B1 for increased  $V_D$  bias.

Fig. 6. Detailed analysis of the various stress regimes for  $V_G=-2.5$  V. The simulated capture and emission time together with the first passage times for the two different emission pathways,  $\tau_e^2$  and  $\tau_e^1$  (left). At around  $V_D\sim-1.8$  V the emission pathway switches from  $2\to 2'\to 1$  to the faster one over 1', similar to the switching trap behavior shown in Fig. 3. The NMP transition rates  $k_{i,j}$  which determine the first passage times as well as the emission time  $\tau_e$  [see (2)] (right). The analysis clearly shows a large contribution of secondary generated carriers in the CB to the total NMP transition rates.

for charging the defects stays the same over the whole  $V_D$  bias range  $(1 \rightarrow 2' \rightarrow 2)$ , the discharging path changes, similar to the switching trap behavior characterized in Fig. 3. As one can see for low  $V_D$  conditions, the defect emits its charge over  $2 \rightarrow 2' \rightarrow 1$ . However, starting from  $V_D \sim -1.8$  V, the emission time  $\tau_e$  is determined by the faster pathway  $2 \rightarrow 1' \rightarrow 1$ . To understand the nature of this change in  $\tau_e$  all relevant NMP transition rates to calculate the first-passage time for a pathway, and thereby the emission time  $\tau_e$  are shown in Fig. 6 (right). The relationship between the NMP rates  $k_{i,j}$ ,

the first passage times  $\tau_e^i$  and the emission time  $\tau_e$  are given by [4]

$$\tau_e^{2'} = \frac{1}{k_{2,2'}} + \frac{1}{k_{2',1}} \left( 1 + \frac{k_{2',2}}{k_{2,2'}} \right) \\

\tau_e^{1'} = \frac{1}{k_{2,1'}} + \frac{1}{k_{1',1}} \left( 1 + \frac{k_{1',2}}{k_{2,1'}} \right) \\$$

$$\tau_e \approx \frac{1}{\frac{1}{\tau_e^{2'}} + \frac{1}{\tau_e^{1'}}} \tag{2}$$

with  $\tau_e^{2'}$  describing the emission time from  $2 \to 1$  over the metastable state 2' and  $\tau_e^{1'}$  over 1'. Two very important implications can be seen in Fig. 6. First, it is clear that interactions with the CB play a major role due to the high NMP rates, particularly for  $k_{2,1'}$ . As can be seen in Fig. 2, starting from  $V_D < -1.5$  V impact ionization leads to a high concentration of (energetic) carriers in the CB which dominate the respective transition rates and, thus, determine the new and faster discharging path via 1' to 1. Second, the VB rates are rather constant for all stress conditions. Typically, the electric field and, thus, the shift of the trap level determine the transition rates. This can be clearly seen in Fig. 4 for the NMP<sub>eq.</sub> model, where both  $\tau_e$  and  $\tau_c$  increase with applied  $V_D$  (= lower electric field). However, taking into account the EDFs from Fig. 2, one can see a broad energetic distribution of particles in the channel region. Although the electric field decreases with increasing  $V_D$  bias, the high energy fraction of the particles in the VB leads to a stronger contribution to the transition rates. Thus, even the VB NMP rates remain rather constant over the various stress conditions. To summarize, this analysis provides insights into how nonequilibrium EDFs are able to change the respective NMP transition rates and further explain the results shown in Fig. 5. Finally, to obtain the good agreement between simulations and experiment for the  $NMP_{neq.}$  model, we set the lateral position of the trap B1 to  $x_{\text{trap}} = 65 \text{ nm}$ , which is within the  $\pm 20\%$  uncertainty of the experimentally extracted position of 80 nm.

Although the measurement data are rather puzzling, the extended  $NMP_{neq.}$  model is able to fully explain the complex behavior of BI without introducing any new parameters, while the  $NMP_{eq.}$  model fails to adequately describe all measured characteristics. The detailed analysis presented helps to understand how holes and secondary generated electrons interact with oxide defects. Thereby, it further validates our approach and demonstrates the necessity to include nonequilibrium effects for nonuniform BTI stress. However, for the sake of completeness, we want to emphasize that it is difficult to deduce a general behavior of oxide defects for increasing  $V_D$  stress regimes. Due to the rather large physical parameter set of a four state defect as well as the broad distribution of these parameters in an amorphous oxide, each defect will exhibit a different response to an applied drain bias.

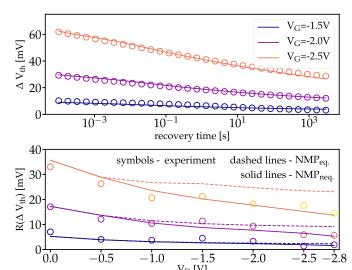

# IV. BEHAVIOR OF LARGE AREA PMOSFETS

In this section, we apply the described methodology to a large ensemble of oxide traps to elucidate the behavior of large area devices. Our comprehensive study covers a broad  $V_G - V_D$  stress matrix with  $V_G = -1.5/-2.0/-2.5$  V and  $V_D$  ranges from 0 V up to -2.8 V. We defined the recoverable component R within the measurement window of  $t_{\rm stress} = 1$  ks

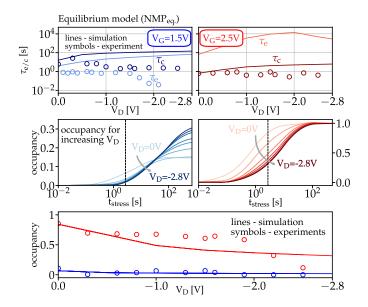

Fig. 7. Comparison of simulated threshold voltage shifts (solid lines) to the experimental data (open circles) for pure BTI conditions (top). The data set was used to calibrate the NMP<sub>eq</sub>, model to extract a unique parameter set for all simulations. Recoverable component *R* for various stress regimes (bottom). As can be seen, the NMP<sub>neq</sub>, model (solid lines) properly represents the experimental trend (open circles), while the NMP<sub>eq</sub>, model (dashed lines) fails to predict *R*.

and  $t_{\text{recovery}} = 1$  ks to be the difference between  $\Delta V_{\text{th,max}}$  (1 us after switching from stress to recovery conditions) and the degradation  $\Delta V_{\text{th}}$  after 1 ks of recovery.

Our measurements are in full agreement with other experimental studies [20], [21] which also show a reduced recoverable component *R* with increased drain bias. Depending on the applied stress regime, the total degradation is a superposition of charged oxide traps due to BTI and the creation of interface states due to HCD. However, it was shown that hot-carrier induced interface states hardly recover at the used measurement conditions [34]. Thus, the overall recoverable component *R* is mainly determined by oxide traps.

In order to extract the model parameters, we again started by calibrating the NMP<sub>eq.</sub> model to pure BTI measurement data. We used the extended measure-stress-measure technique with  $V_G = -1.5/-2.0/-2.5$  V and stress and recovery times of 1 ks to characterize BTI. As shown in Fig. 7, the NMP<sub>eq.</sub> model is able to accurately represent the experimental data. Note that for all subsequent simulations, we used the same unique parameter set. Furthermore, we want to highlight that the extracted model parameter set is in full agreement with the frequently reported defect band in SiON of about 1.35 eV below the Si channel mid gap (1.41 eV was used in this paper) [11], [13], [35], [36].

As for the single trap BI, we applied both models, NMP<sub>eq</sub>. and NMP<sub>neq</sub>, to access the behavior of oxide traps and the recoverable component R for mixed-mode stress regimes. As shown in Fig. 7, the NMP<sub>neq</sub> model results in a much better agreement with experimental data and predicts the rapid decrease of R much better.

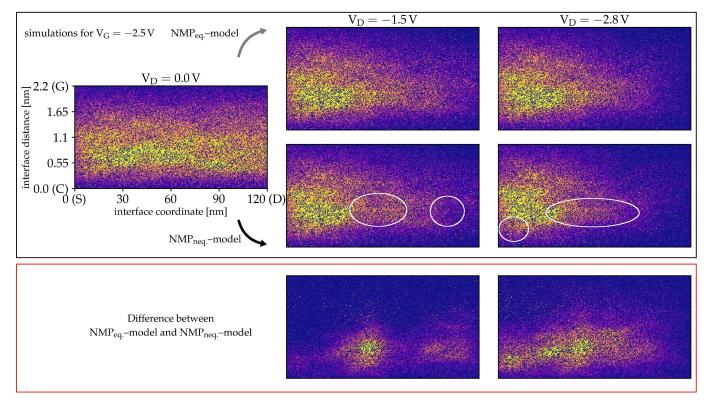

A detailed comparison of both models for a large ensemble of spatially distributed defects across the oxide and with distributed trap parameters is shown in Fig. 8. The simulation snapshots are for  $V_G = -2.5$  V and various  $V_D$  values directly

Fig. 8. Detailed comparison of the NMP<sub>eq</sub>. versus the NMP<sub>neq</sub>. model applied to model the behavior of large area pMOSFETs stressed at nonuniform BTI conditions for  $V_G = -2.5$  V. The simulation snapshots show the distribution of charged defects across the oxide (yellow: charged defects) and are taken directly after the stress. Clearly visible for the NMP<sub>eq</sub>. model is that traps in the source region are unaffected by an increased  $V_D$ , while defects located at the drain side ( $V_D = -1.5$  V) as well as in the middle of the channel ( $V_D = -2.8$  V) stay uncharged due to the reduced oxide field. On the other hand, the NMP<sub>neq</sub>. model predicts a much faster reduction of charged defects (highlighted areas in the middle and right) and as well affects defects located at the source side (highlighted area in the right).

after 1 ks of stress. One can clearly see that with increasing  $V_D$  the amount of charged traps reduces, particularly in the middle of the channel and the drain sides. However, traps in the vicinity of the source side are rather unaffected and possess the same behavior for all drain bias conditions using the NMP<sub>eq.</sub> variant [Fig. 8 (top)]. This is as well reflected by the mismatch between the simulation results and experimental data in Fig. 7. On the other hand, as the NMP<sub>neq.</sub> model takes nonequilibrium processes into account, also the source side of the device is affected. However, as already mentioned in the previous section, the interaction of the defects with energetic carriers in the VB and CB strongly depends on the physical parameters of the individual defect. The results for the NMP<sub>neq.</sub> variant of the model [Fig. 8 (bottom)] show that the reduction of charged defects proceeds much faster. For  $V_D = -1.5$  V, already a substantial difference between both variants of the model is visible. Compared to the NMPeq. model, less defects are charged in the middle of the channel (highlighted area) and on the drain side. Increasing the drain voltage further aggravates the situation. In addition to the defects located in the center of the channel, even some traps located in the source regionhighlighted in Fig. 8—remain partially uncharged and do not contributed to the recoverable component R. By taking into consideration nonequilibrium processes, the predicted trend of the NMP<sub>neq.</sub> model results in a very good agreement between experimental and simulation data (see Fig. 7). We further want to emphasize that all our simulations include the combined

interaction of oxide defects with carriers in the channel as well as in the gate. An applied drain bias, however, severely affects the EDF of carriers in the channel, while carriers in the gate mostly not distorted. Thus, defects spatially located closer to the channel interface are potentially more affected by a drain bias than defects in the vicinity of the gate interface. This particular effect is also visible in Fig. 8.

# V. CONCLUSION

We have presented a modeling approach to understand the impact of an applied drain bias onto the recoverable component of BTI. To represent the rather puzzling and intriguing experimental trends for the dynamics of oxide traps presented in Part I, we extended the existing four state nonradiative multiphonon model toward nonequilibrium processes. The proposed framework includes full distribution functions—a concept well known in modeling HCD—for holes and electrons obtained as a solution of the bipolar BTE.

We compare experimentally recorded characteristics and simulation results for an individual oxide defect as well as a large ensemble of traps in a large area device. A detailed analysis reveals that the complex behavior of defects with increased drain stress can only be fully understood by taking interactions with energetic majority and secondary generated carriers in the VB and CB into account. Furthermore, we show that due to impact ionization also the source side of the device is shifted from equilibrium conditions. Thus, even defects in

this region are possibly affected by an applied drain bias. We thus conclude that our nonequilibrium model is able to fully explain the measured trends and thereby explains the impact of a drain bias on the capture and emission times of oxide defects.

### REFERENCES

- [1] S. Novak et al., "Transistor aging and reliability in 14 nm trigate technology," in Proc. IEEE Int. Rel. Phys. Symp., Apr. 2015, pp. 2F.2.1–2F.2.5, doi: 10.1109/IRPS.2015.7112692.

- [2] S. Ramey et al., "Intrinsic transistor reliability improvements from 22 nm tri-gate technology," in Proc. IEEE Int. Rel. Phys. Symp., Apr. 2013, pp. 4C.5.1–4C.5.5, doi: 10.1109/IRPS.2013.6532017.

- [3] T. Grasser et al., "On the microscopic structure of hole traps in pMOSFETs," in *IEDM Tech. Dig.*, Dec. 2014, pp. 21.1.1–21.1.4, doi: 10.1109/IEDM.2014.7047093.

- [4] T. Grasser, "Stochastic charge trapping in oxides: From random telegraph noise to bias temperature instabilities," *Microelectron. Rel.*, vol. 52, no. 1, pp. 39–70, Jan. 2012, doi: 10.1016/j.microrel.2011.09.002.

- [5] M. Bina et al., "Predictive hot-carrier modeling of n-channel MOSFETs," IEEE Trans. Electron Devices, vol. 61, no. 9, pp. 3103–3110, Sep. 2014, doi: 10.1109/TED.2014.2340575.

- [6] C. Guerin, V. Huard, and A. Bravaix, "General framework about defect creation at the Si/SiO<sub>2</sub> interface," *J. Appl. Phys.*, vol. 105, no. 11, pp. 114513-1–114513-12, 2009, doi: 10.1063/1.3133096.

- [7] A. Bravaix, V. Huard, D. Goguenheim, and E. Vincent, "Hot-carrier to cold-carrier device lifetime modeling with temperature for low power 40 nm Si-bulk NMOS and PMOS FETs," in *IEDM Tech. Dig.*, Dec. 2011, pp. 27.5.1–27.5.4, doi: 10.1109/IEDM.2011.6131625.

- [8] J. H. Stathis, S. Mahapatra, and T. Grasser, "Controversial issues in negative bias temperature instability," *Microelectron. Rel.*, vol. 81, pp. 244–251, Feb. 2018, doi: 10.1016/j.microrel.2017.12.035.

- [9] K. Huang and A. Rhys, "Theory of light absorption and non-radiative transitions in F-centres," *Proc. Roy. Soc. London A, Math., Phys. Eng. Sci.*, vol. 204, no. 1078, pp. 406–423, 1950, doi: 10.1098/rspa.1950. 0184.

- [10] M. J. Kirton and M. J. Uren, "Noise in solid-state microstructures: A new perspective on individual defects, interface states and low-frequency (1/f) noise," Adv. Phys., vol. 38, no. 4, pp. 367–468, 1989, doi: 10.1080/00018738900101122.

- [11] G. Rzepa et al., "Complete extraction of defect bands responsible for instabilities in n and pFinFETs," in Proc. IEEE Symp. VLSI Technol., Jun. 2016, pp. 1–2, doi: 10.1109/VLSIT.2016.7573437.

- [12] Y. Y. Illarionov et al., "The role of charge trapping in MoS<sub>2</sub>/SiO<sub>2</sub> and MoS<sub>2</sub>/hBN field-effect transistors," 2D Mater., vol. 3, no. 3, p. 035004, 2016, doi: 10.1088/2053-1583/3/3/035004.

- [13] G. Rzepa et al., "Comphy—A compact-physics framework for unified modeling of BTI," Microelectron. Rel., vol. 85, pp. 49–65, Jun. 2018, doi: 10.1016/j.microrel.2018.04.002.

- [14] P. M. Lenahan, "Atomic scale defects involved in MOS reliability problems," *Microelectron. Eng.*, vol. 69, nos. 2–4, pp. 173–181, 2003, doi: 10.1016/S0167-9317(03)00294-6.

- [15] S. Tyaginov, "Physics-based modeling of hot-carrier degradation," in Hot Carrier Degradation in Semiconductor Devices. Cham, Switzerland: Springer, 2015, pp. 105–150, doi: 10.1007/978-3-319-08994-2\_4.

- [16] K. Hess et al., "Simulation of Si-SiO<sub>2</sub> defect generation in CMOS chips: From atomistic structure to chip failure rates," in *IEDM Tech. Dig.*, Dec. 2000, pp. 93–96, doi: 10.1109/IEDM.2000.904266.

- [17] K. Hess, L. F. Register, B. Tuttle, J. Lyding, and I. C. Kizilyalli, "Impact of nanostructure research on conventional solid-state electronics: The giant isotope effect in hydrogen desorption and CMOS lifetime," *Phys. E, Low-Dimensional Syst. Nanostruct.*, vol. 3, nos. 1–3, pp. 1–7, 1998, doi: 10.1016/S1386-9477(98)00211-2.

- [18] S. Tyaginov, M. Jech, J. Franco, P. Sharma, B. Kaczer, and T. Grasser, "Understanding and modeling the temperature behavior of hot-carrier degradation in SiON nMOSFETs," *IEEE Electron Device Lett.*, vol. 37, no. 1, pp. 84–87, Jan. 2016, doi: 10.1109/LED.2015.2503920.

- [19] A. Makarov et al., "Hot-carrier degradation in FinFETs: Modeling, peculiarities, and impact of device topology," in *IEDM Tech. Dig.*, Dec. 2017, pp. 13.1.1–13.1.4, doi: 10.1109/IEDM.2017.8268381.

- [20] G. A. Rott, K. Rott, H. Reisinger, W. Gustin, and T. Grasser, "Mixture of negative bias temperature instability and hot-carrier driven threshold voltage degradation of 130 nm technology p-channel transistors," *Microelectron. Rel.*, vol. 54, nos. 9–10, pp. 2310–2314, 2014, doi: 10.1016/j.microrel.2014.07.040.

- [21] C. Schlünder, R. Brederlow, B. Ankele, W. Gustin, K. Goser, and R. Thewes, "Effects of inhomogeneous negative bias temperature stress on p-channel MOSFETs of analog and RF circuits," *Microelectron. Rel.*, vol. 45, no. 1, pp. 39–46, 2005, doi: 10.1016/j.microrel.2004.03.017.

- [22] B. Ullmann et al., "The impact of mixed negative bias temperature instability and hot carrier stress on single oxide defects," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr. 2017, pp. XT-10.1–XT-10.6, doi: 10.1109/IRPS.2017.7936424.

- [23] X. Federspiel, M. Rafik, D. Angot, F. Cacho, and D. Roy, "Interaction between BTI and HCI degradation in high-K devices," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2013, pp. XT.9.1–XT.9.4, doi: 10.1109/IRPS.2013.6532124.

- [24] A. Bravaix et al., "Impact of the gate-stack change from 40 nm node SiON to 28 nm high-K metal gate on the hot-carrier and bias temperature damage," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2013, pp. 2D.6.1–2D.6.9, doi: 10.1109/IRPS.2013.6531961.

- [25] B. Kaczer et al., "Mapping of CMOS FET degradation in bias space— Application to dram peripheral devices," J. Vac. Sci. Technol. B, Microelectron. Process. Phenom., vol. 35, no. 1, p. 01A109, 2017, doi: 10.1116/1.4972872.

- [26] P. Chaparala and D. Brisbin, "Impact of NBTI and HCI on PMOSFET threshold voltage drift," *Microelectron. Rel.*, vol. 45, no. 1, pp. 13–18, 2005, doi: 10.1016/j.microrel.2004.03.016.

- [27] Y. He and G. Zhang, "Experimental insights on the degradation and recovery of pMOSFET under non-uniform NBTI stresses," in *Proc. 18th IEEE Int. Symp. Phys. Failure Anal. Integr. Circuits (IPFA)*, Jul. 2011, pp. 1–6, doi: 10.1109/IPFA.2011.5992767.

- [28] B. Ullmann et al., "Impact of mixed negative bias temperature instability and hot carrier stress on MOSFET characteristics—Part I: Experimental," *IEEE Trans. Electron Devices*, vol. 66, no. 1, pp. 232–240, Jan. 2019.

- [29] M. Bina, K. Rupp, S. Tyaginov, O. Triebl, and T. Grasser, "Modeling of hot carrier degradation using a spherical harmonics expansion of the bipolar Boltzmann transport equation," in *IEDM Tech. Dig.*, Dec. 2012, pp. 30.5.1–30.5.4, doi: 10.1109/IEDM.2012.6479138.

- [30] I. Starkov, H. Enichlmair, S. Tyaginov, and T. Grasser, "Analysis of the threshold voltage turn-around effect in high-voltage n-MOSFETs due to hot-carrier stress," in *Proc. IEEE Int. Rel. Phys. Symp. (IRPS)*, Apr. 2012, pp. XT.7.1–XT.7.6, doi: 10.1109/IRPS.2012.6241937.

- [31] S.-M. Hong and C. Jungemann, "A fully coupled scheme for a Boltzmann-Poisson equation solver based on a spherical harmonics expansion," *J. Comput. Electron.*, vol. 8, nos. 3–4, p. 225, Oct. 2009, doi: 10.1007/s10825-009-0294-y.

- [32] S.-M. Hong, C. Jungemann, and M. Bollhofer, "A deterministic Boltzmann equation solver for two-dimensional semiconductor devices," in *Proc. Int. Conf. Simulation Semiconductor Process. Devices*, Sep. 2008, pp. 293–296, doi: 10.1109/SISPAD.2008.4648295.

- [33] J. F. Conley, P. M. Lenahan, A. J. Lelis, and T. R. Oldham, "Electron spin resonance evidence that E'<sub>γ</sub> centers can behave as switching oxide traps," *IEEE Trans. Nucl. Sci.*, vol. 42, no. 6, pp. 1744–1749, Dec. 1995.

- [34] G. Pobegen, S. Tyaginov, M. Nelhiebel, and T. Grasser, "Observation of normally distributed energies for interface trap recovery after hot-carrier degradation," *IEEE Electron Device Lett.*, vol. 34, no. 8, pp. 939–941, Aug. 2013, doi: 10.1109/LED.2013.2262521.

- [35] G. Rzepa et al., "Efficient physical defect model applied to PBTI in high-κ stacks," in Proc. IEEE Int. Rel. Phys. Symp. (IRPS), Apr. 2017, p. XT–11.1–XT–11.6, doi: 10.1109/IRPS.2017.7936425.

- [36] V. Huard, M. Denais, and C. Parthasarathy, "NBTI degradation: From physical mechanisms to modelling," *Microelectron. Rel.*, vol. 46, no. 1, pp. 1–23, Jan. 2006, doi: 10.1016/j.microrel.2005.02.001.

Markus Jech received the M.Sc. degree in physics from the Technische Universität Wien, Vienna, Austria, in 2014, where he is currently pursuing the Ph.D. degree with the Institute for Microelectronics. His Ph.D. research focuses or nonequilibrium reliability effects in transistors, such as hot-carrier degradation and its interplay with bias temperature instability.

**Bianka Ullmann** was born in Sofia, Bulgaria, in 1984. She received the M.Sc. degree in physics and the Ph.D. degree in engineering sciences from the Technische Universität Wien, Vienna, Austria, in 2012 and 2018, respectively.

Her current research interests include the reliability of MOSFETs, particularly the interplay between bias temperature instability and hot-carrier degradation.

Michael WaltI received the Ph.D. degree from the Technische Universität Wien (TU Wien), Vienna, Austria, in 2016.

He is currently with the Reliability Group and directs the Technology Laboratory, Institute of Microelectronics, TU Wien. His current research interests include the experimental characterization of semiconductor device reliability issues, such as bias temperature instabilities and hot carrier degradation.

Gerhard Rzepa received the B.Sc. degree in electrical engineering and the Dipl.Ing. degree in microelectronics from the Technische Universität Wien (TU Wien), Vienna, Austria, in 2010 and 2013, respectively, and the Ph.D. degree on the topic of modeling of bias temperature instabilities from the Institute for Microelectronics, TU Wien.

He has been with the Institute for Microelectronics, TU Wien.

**Dominic Jabs** received the B.Sc. and M.Sc. degrees in physics from RWTH Aachen University, Aachen, Germany, in 2009 and 2011, respectively, and the Ph.D. degree with the Chair of Electromagnetic Theory, RWTH Aachen University, in 2017, with a focus on the physics-based simulation of semiconductor power devices.

Stanislav Tyaginov was born in Saint Petersburg, Russia, in 1978. He received the M.Sc. and Ph.D. degrees from the loffe Physical-Technical Institute in 2002 and 2006, respectively.

He led the Physics-Based Hot-Carrier Degradation Model Development Group, Technical University Vienna. He currently is a Marie Curie Post-Doctoral Fellow with imec.

He has authored or co-authored over 100 papers in peer reviewed scientific journal and in conference proceedings.

**Christoph Jungemann** (M'97–SM'06) received the Ph.D. degree in electrical engineering from RWTH Aachen University, Aachen, Germany.

After working at Fujitsu Ltd., Kawasaki, Japan, the University of Bremen, Bremen, Germany, the Stanford University, Stanford, CA, USA, and the Braunschweig University of Technology, Braunschweig, Germany, he became a Professor of microelectronics with Bundeswehr University Munich, Neubiberg, Germany, in 2006. Since 2011, he has been the Chair of electromagnetic theory with RWTH Aachen University.

Alexander Grill received the Dipl.Ing. degree in microelectronics from the Technische Universität Wien, Vienna, Austria, in 2013, where he is currently pursuing the Ph.D. degree with the Institute for Microelectronics.

His scientific interests include the simulation of Nitride-based heterostructure devices.

**Tibor Grasser** (F'16) is currently the Head of the Institute for Microelectronics, Technische Universität Wien, Vienna, Austria. He has edited various books, e.g., on the bias temperature instability and on hot carrier degradation (both Springer).

Dr. Grasser is a Distinguished Lecturer of the IEEE Electron Devices Society.